Можно привести следующую классификацию АЛУ.

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

для чисел с фиксированной точкой;

для чисел с плавающей точкой;

для десятичных чисел.

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в от дельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие прием из других устройств (например, памяти) операндов, их преобразование и выдачу результатов преобразования в другие устройства.

Арифметическо-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определенных микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

Обработка любой информации на компьютере сводится к выполнению процессором различных арифметических и логических операций. Для этого в состав процессора входит так называемое арифметико-логическое устройство. Оно состоит из ряда устройств, построенных на рассмотренных выше логических элементах. Важнейшими из таких устройств являются регистры и сумматор.

Регистр представляет собой электронный узел, предназначенный для хранения многоразрядного двоичного числового кода. Такой код может быть числовым кодом команды, выполняемой процессором, либо кодом некоторого числа (данного), которое используется при выполнении данной команды. Упрощенно можно представить регистр как совокупность ячеек, в каждой из которых может быть записано одно из двух значений: 0 или 1, то есть один разряд двоичного числа.

Такая ячейка называемая триггером, представляет собой некоторую логическую схему, составленную из рассмотренных выше логических элементов. Под воздействием сигналов, поступающих на вход триггера, он переходит в одно из двух возможных устойчивых состояний, при которых на выходе будет выдаваться сигнал, кодирующий значение 0 или 1. Для хранения в регистре одного байта информации необходимо 8 триггеров.

Сумматор – это электронная схема, предназначенная для выполнения операции суммирования двоичных числовых кодов. При суммировании по правилам двоичной арифметики двух единиц результат равен 10 и происходит перенос в старший двоичный разряд. Для реализации простейшей операции суммирования одноразрядных двоичных чисел используется логическая схема (одноразрядный сумматор), составленная из следующих логических элементов: двух элементов И, одного элемента ИЛИ и одного элемента НЕ. Эта схема имеет три входа (два слагаемых и возможный перенос из предыдущего разряда) и два выхода (сумма и возможный перенос в следующий разряд). Многоразрядный сумматор строится как логическая схема на основе одноразрядных двоичных сумматоров.

Таким образом, можно сделать вывод, что логические элементы являются теми «кирпичиками», из которых путем конструирования логических схем строится «здание» любого современного компьютера.

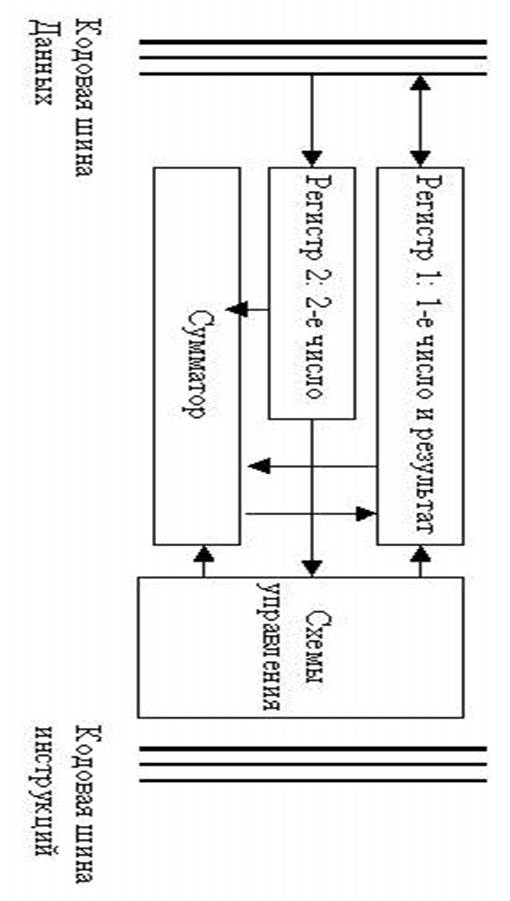

. Функционально в простейшем варианте АЛУ (рис.) состоит из двух регистров, сумматора и схем управления (местного устройства управления).

Сумматор — вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова.

Регистры — быстродействующие ячейки памяти различной длины: регистр 1 имеет разрядность двойного слова, а регистр 2 — разрядность слова. При выполнении операций в регистр 1 помещается первое число, участвующее в операции, а по завершении операции — результат; в регистр 2 — второе число, участвующеев операции (по завершении операции информация в нем не изменяется). Регистр 1 может и' принимать информацию с кодовых шин данных, и выдавать информацию на них; регистр 2 только получает информацию с этих шин.

Логическая структура микропроцессора, т. е. конфигурация составляющих микропроцессор логических схем и связей между ними, определяется функциональным назначением. Именно структура задает состав логических блоков микропроцессора и то, как эти блоки должны быть связаны между собой, чтобы полностью отвечать архитектурным требованиям. Срабатывание электронных блоков микропроцессора в определенной последовательности приводит к выполнению заданных архитектурой микропроцессора функций, т. е. к реализации вычислительных алгоритмов. Одни и те же функции можно выполнить в микропроцессорах со структурой, отличающейся набором, количеством и порядком срабатывания логических блоков. Различные структуры микропроцессоров, как правило, обеспечивают их различные возможности, в том числе и различную скорость обработки данных.

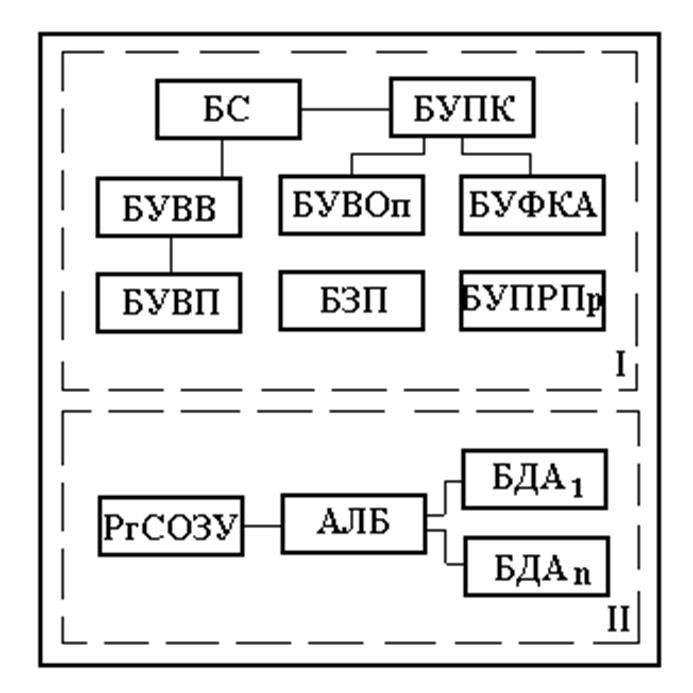

Логические блоки микропроцессора с развитой архитектурой показаны на рис. 2.3.

Рис. 2.3. Общая логическая структура микропроцессора: I - управляющая часть, II - операционная часть; БУПК - блок управления последовательно-стью команд; БУВОп - блок управления выполнением операций; БУФКА - блок управления формированием кодов адресов; БУВП - блок управления виртуальной памятью; БЗП - блок защиты памяти; БУПРПр - блок управления прерыванием работы процессора; БУВВ - блок управления вводом/выводом; РгСОЗУ - регистровое сверхоперативное запоминающее устройство; АЛБ - арифметико-логический блок; БДА - блок дополнительной арифметики; БС - блок синхронизации.

Коды операции команд программы, воспринимаемые управляющей частью микропроцессора, расшифрованные и преобразованные в ней, дают информацию о том, какие операции надо выполнить, где в памяти расположены данные, куда надо направить результат и где расположена следующая за выполняемой команда.

Управляющее устройство имеет достаточно средств для того, чтобы после восприятия и интерпретации информации, получаемой в команде, обеспечить переключение (срабатывание) всех требуемых функциональных частей машины, а также для того, чтобы подвести к ним данные и воспринять полученные результаты. Именно срабатывание, т. е. изменение состояния двоичных логических элементов на противоположное, позволяет посредством коммутации вентилей выполнять элементарные логические и арифметические действия, а также передавать требуемые операнды в функциональные части микроЭВМ.

Устройство управления в строгой последовательности в рамках тактовых и цикловых временных интервалов работы микропроцессора (такт - минимальный рабочий интервал, в течение которого совершается одно элементарное действие; цикл - интервал времени, в течение которого выполняется одна машинная операция) осуществляет: выборку команды; интерпретацию ее с целью анализа формата, служебных признаков и вычисления адреса операнда (операндов); установление номенклатуры и временной последовательности всех функциональных управляющих сигналов; генерацию управляющих импульсов и передачу их на управляющие шины функциональных частей микроЭВМ и вентили между ними; анализ результата операции и изменение своего состояния так, чтобы определить месторасположение (адрес) следующей команды.

Дата добавления: 2015-11-26; просмотров: 1553;