РАЗДЕЛ 3 Программное обеспечение микропроцессорных систем 4 страница

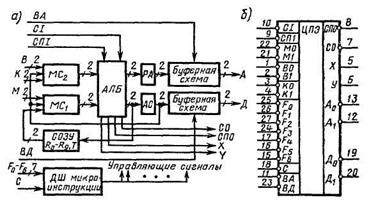

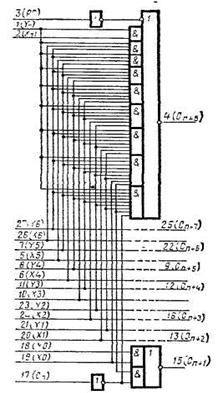

Данные от внешних источников информации поступают в ЦПЭ по одной из трех входных магистралей: В, М и К. Результаты вычислений передаются из ЦПЭ на ВУ по одной из двух выходных магистралей: А и Д. Внутри ЦПЭданные могут храниться в одном из регистров СОЗУ, РА, АС. Данные из входных магистралей, регистров СОЗУ, АС могут поступать на вход АЛБ через два внутренних мультиплексора. Входы и выходы CI, СП1, С0, СП0, X, Y служат для организации сдвигов и переноса, возможных при выполнении арифметических и логических операций. Если обозначить операнды, поступающие в АЛБ а0a1 и bob1 то сигналы на выходах X, Y, С0 определяются логическими уравнениями

X=a0b0 V a1b1; Y= a1b1 V a0b1 V a1b0 V b0b1 V a0a1;

Рис. 1. Схема ЦПЭ К589ИК02 (а) и его условное обозначение (б).

Центральный процессорный элемент выполняет операцию в соответствии с кодом микрооперации F0 – F6, подаваемым на вход дешифратора микроинструкций. Дешифратор ДШ микроинструкций управляет работой мультиплексоров, выбирает один из регистров СОЗУ и определяет операцию, выполняемую в АЛБ. Синхронизируется работа ЦПЭ синхроимпульсами С.

Для ЦПЭ характерна такая последовательность работы. После прихода положительного фронта сигнала синхронизации на входах F0 – F6устанавливается код микроинструкции. В соответствии с этим кодом к АЛБ с помощью мультиплексоров подключаются входы информационных магистралей либо один из регистров СОЗУ или регистр АС. После преобразования этих данных в соответствии с кодом микроинструкции в АЛБ формируется результат, который загружается по отрицательному фронту синхросигнала в указанный в той же микроинструкции регистр. Затем содержимое РА и АС через выходной буфер в соответствии с сигналами управления буфером ВА и ВД (выборка адреса и данных соответственно) может подаваться на выходные магистрали А и Д.

Мультиплексоры имеют различные организацию и назначение. Мультиплексор МС1 в зависимости от кода микроинструкции передает на входы АЛБ информацию со входной магистрали М, АС или из выбранного регистра СОЗУ. Мультиплексор MC2 соединяет со входом АЛБ входные магистрали В, АС или магистраль К. Выходные сигналы второго мультиплексора образованы как поразрядная конъюнкция кода на магистрали К и выбранных информационных сигналов В или А С. Если на магистраль К подавать информацию со специальных разрядов микрокоманды, то можно маскировать входы в АЛБ и тем самым значительно увеличивать число реализуемых в ЦПЭ микроопераций. Магистраль К может использоваться при арифметических операциях для маскирования частей обрабатываемых полей и для передачи констант из памяти микрокоманд.

Арифметическо-логический блок способен выполнять арифметические и логические операции, включая двоичное сложение в дополнительном коде, операции ± 1, поразрядное логическое сложение и умножение, поразрядное «исключающее ИЛИ—НЕ» и поразрядное логическое дополнение. Для выполнения операции сдвига вправо имеются выводы входа СП1 и выхода СП0. Линии входа С1 и выхода С0 переноса предназначены для обеспечения последовательного распространения переноса. Данные на выходы С0 и СП0 поступают через буферную схему с тремя состояниями, причем разрешается выдача либо С0, либо СП0. Выходы X, Y предназначены для организации ускоренного переноса произвольной длины слова.

Содержание выполняемой микрокоманды определяется функциональной F- и регистровой R-группами микроинструкции: F-группа определяется тремя старшими

разрядами данных (F6, F5, F4), R-группа — четырьмя младшими разрядами.

Группа R1 включает в себя регистры R0 — R9, Т, АС и обозначается символом Rn, группы R2 и R3 содержат только регистры Т и АС. Форматы и кодировка F- и R-групп приведены в табл. 8.1 и 8.2 соответственно[1]. Система микроопераций и ее описание для произвольной, нулевой и единичной информации на магистрали К приведены в табл. 8.3 и 8.4. [1].

ВТОРОЙ ВОПРОС

Блок микропрограммного управления К589ИК01 представляет собой основную микросхему устройства управления, определяющего последовательность выполнения микрокоманд. В БМУ в соответствии с кодом выполняемой микрооперации, поступающей из памяти микрокоманд, формируется адрес очередной микрокоманды. Кроме того, в БМУ записывается, хранится и выдается информация, определяемая внешними условиями (например, сигнал переноса из старшего разряда ЦПЭ), в соответствии с которой организуются условные переходы.

В БМУ заложена возможность выполнения 11 типов микроопераций перехода (четыре типа операций безусловного перехода и семь условного) и восьми микроопераций приема, хранения и выдачи признаков. Большое число типов выполняемых БМУ микроопераций позволяет строить на его основе устройства управления, реализующие эффективные микропрограммы.

Адрес микрокоманды состоит из девяти двоичных разрядов, но в отличие от обычного линейного представления массива ячеек памяти К589ИК01 предполагает, что ячейки расположены в виде прямоугольной матрицы. Размер матрицы 32 строки на 16 колонок. Расположение микрокоманды задается элементом, находящимся на пересечении одной из колонок и одного из столбцов. Номер колонки определяется младшими четырьмя разрядами адреса микрокоманды, а номер строки — пятью старшими. Таким образом, общее количество слов памяти микрокоманд, адресуемых БМУ, составляет 512.

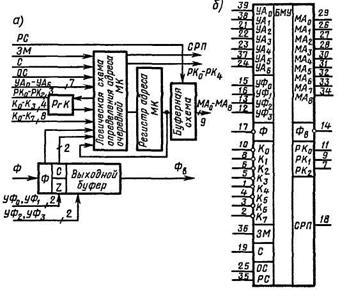

Блок микропрограммного управления (рис. 2) состоит из логической схемы определения очередного адреса микрокоманды, управляемой кодами операций, поступающими по магистрали У А, регистра адреса микрокоманды и схем, управляемых по магистрали УФ (обеспечивающих запись, хранение и выдачу информации о признаках). Код команды, по которому из памяти микрокоманд вызывается соответствующая микропрограмма, поступает па магистрали К, причем первые четыре разряда кода команды могут быть записаны в регистре команд РгК- Информация о признаках поступает в БМУ по входу Ф, а извлекается — по выходу Фв. Схема записи, хранения и выдачи информации о признаках состоит из триггера Ф и двух флажковых триггеров С и Z.

Через некоторое время после прихода фронта сигнала синхронизации на магистрали УА устанавливается код микрооперации перехода, поступающий из памяти микрокоманд. Далее в логической схеме определения очередного адреса микрокоманды МК происходит выработка кода необходимого адреса. Код с приходом среза сигнала синхронизации загружается в регистр адреса МК, если на входе ЗМ установлен «0». В противном случае по срезу сигнала синхронизации в регистр адреса МК загружается код, содержащийся в магистрали К. Информация, содержащаяся на входах К0 — К3, загружается в разряды 4—7 регистра адреса МК, а со входов К4 — К7 — в разряды 1—3. В восьмой разряд РгА МК записывается «0».

Если в результате работы схемы определения очередного адреса установлен адрес, являющийся элементом матрицы, находящимся на пересечении нулевой строки и 15-й колонки, то на выход СРП микросхемы выдается стробирующий сигнал разрешения прерывания.

Аналогично выполняются микрооперации по записи информации о признаках во флажковые триггеры. В триггер Ф информация записывается в то время, когда на

входе синхронизации С установлен «0». Далее по приходу среза сигнала синхронизации в соответствии с кодом микроопераций, поступающим на входы УФ0, УФ1, происходит загрузка содержимого триггера Ф во флажковые триггеры С и Z. Выдача содержимого флажковых триггеров определяется кодом операции, устанавливаемым на входах УФ2, УФ3.

Рис. 2. Схема БМУ К589ИК01 (а) и его условное обозначение (б).

В табл. 8.5 [1] приведены системы микроопераций по записи и считыванию информации о признаках вофлажковые триггеры.

В микрооперациях определения очередного адреса микрокоманды используются выходные сигналы триггеров флажковой логики Ф, С и Z. В табл. 8.6 [1]приведена система микроопераций БМУ по определению очередного адреса микрокоманды. Ограниченное число выводов микросхемы К589ИК01 не позволяет использовать прямую адресацию следующей микрокоманды в формате текущей, для этого необходимо иметь 9-разрядное поле магистрали управления адресом УА. В микрокоманде, управляющей работой БМУ, указываются способ формирования адреса следующей микрокоманды и двоичный код малой разрядности (4- или 5-разрядный) для формирования кода адреса. При принятом условном формате памяти микрокоманд в виде матрицы из 32 строк и 16 колонок адрес следующей микрокоманды может принадлежать только определенной области памяти по отношению к текущему адресу (текущая колонка, текущая строка, ограниченная область вблизи текущего адреса). Возможные законы формирования следующего адреса задаются старшими разрядами магистрали УА. Переходы могут быть разделены на безусловные, условные и по кодам регистра команды и магистрали К4 – K7.

Например, если в следующей микрокоманде с адресом 011010111 по магистрали УА записан код 0010111, то будет осуществлен переход к микрокоманде с адресом 101110111, так как первые два разряда указывают тип формирования следующего адреса — переход в текущей колонке JCC. Адрес колонки совпадает с предыдущим адресом (младшие разряды текущего кода адреса — 0111), а младшие пять разрядов микрокоманды указывают номер следующего адреса в текущей колонке— 10111.

При коде старших разрядов магистрали УА6 — УА4, равном 1010, осуществляется условный переход в текущей строке по содержимому триггера С. Например, для предыдущего адреса микрокоманды 011010111 и кода магистрали управления адресом 1010001 при содержимом триггера С = 1 адрес следующей микрокоманды 010010011. В этом коде старшие два разряда совпадают с соответствующими разрядами адреса предыдущей микрокоманды, три младших разряда кода строки 001 задаются младшими разрядами кода УА, четвертый разряд совпадает с соответствующим разрядом предыдущего адреса, второй и третий разряды равны 01, а младший разряд равен коду триггера С. При содержимом триггера С = 0 следующий адрес будет равен 010010010.

Управление адресом по содержимому регистра команд и магистрали К расширяет логические возможности устройства управления и допускает простую организацию режима прерывания программ. Например, при выполнении перехода по разрядам команд К4 — К7 (JPX) код следующего адреса находится в группе адресов строк, определяемой кодами МА8 — МА6 текущего адреса микрокоманды и содержимым разрядов УА1 и УА0. Адрес колонки следующей микрокоманды задается кодом магистрали K4 — К7. При этом адрес следующей микрокоманды будет задан кодом МА8МА7МА6УА0К7К6К5К4.

Выводы МА0 — МА8 и Фв, определяющие выходную информацию, могут быть установлены сигналами PC и ОС в третье состояние. Это позволяет, например, при обработке прерываний адрес очередной микрокоманды задавать ВУ.

ТРЕТИЙ ВОПРОС

Блок приоритетного прерывания К589ИК14 обеспечивает прием сигналов запроса прерывания от различных устройств, входящих в состав вычислительной системы, и выработку при определенных условиях сигнала необходимости перехода к подпрограмме обработки прерывания. При совместном использовании БМУ К589ИК01 и БПП К589ИК14 в БПП вырабатывается сигнал, определяющий установку адреса микрокоманды на МА кодом ВУ, в том числе выходным кодом БПП. При этом выходной код БПП соответствует начальному адресу подпрограммы, вызвавшей прерывание предыдущей программы. Рассматриваемая схема БПП обеспечивает прерывание по восьми источникам запросов и имеет возможность наращивания их количества. БПП обеспечивает выполнение следующих функций:

асинхронный прием и хранение сигналов запроса на прерывание в восьми

направлениях;

выдачу кода уровня принятого сигнала запроса на прерывание;

прием и хранение кода уровня прерывания, обрабатываемого процессором;

выдачу процессору сигнала о наличии запроса на прерывание более высокого

приоритета по сравнению с обрабатываемым.

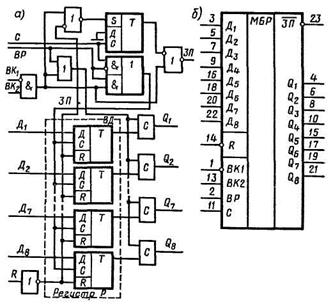

Блок приоритетного прерывания (рис. 3) состоит из совокупности триггеров, в которые по восьми направлениям ЗПр0 — ЗПр7 поступают сигналы запроса на прерывание, и триггерного регистра для хранения кода уровня приоритета программы, обрабатываемой процессором. Информация на этот регистр поступает по магистрали П0 — П2. Кроме того, в состав БПП входят схемы, обеспечивающие выдачу сигнала о наличии запроса на прерывание, и буферная схема, через которую на магистраль КП выдается код поступившего запроса.

Код приоритета выполняемой процессором программы записывается в триггерный регистр текущего приоритета по приходу фронта сигнала разрешения записи. При поступлении на входы ЗПр0 — ЗПр7 от ВУ сигналов, индицирующих запросы на прерывание, они запоминаются в соответствующих триггерах.

Рис. 3. Схема БПП К589ИК14 (а) и его условное обозначение (б).

В зависимости от того, с какого направления пришел сигнал, он получает с помощью шифратора код своего приоритета, сигнал сравнивается с кодом текущего приоритета, записанным по магистрали П0 — П2. Если уровень приоритета пришедшего запроса старше приоритета выполняемой программы и есть сигнал СРП, то с приходом сигнала синхронизации на выходе Пр устанавливается «0», указывающий о необходимости прерывания работы процессора.

Код уровня пришедшего сигнала на прерывание может быть выдан из БПП по магистрали КП0 — КП2, что определяется сигналом РСЧ. В момент установления сигнала Пр блокируется допуск других запросов на прерывание. Блокировка снимается после записи в триггерный регистр текущего состояния нового кода уровня прерывания.

Входы РГ, ВП и выход РПГ служат для аппаратного расширения количества направлений приема сигналов запроса прерывания.

Литература:

1. Л.Н. Преснухин «Микропроцессоры», ч. 1, стр.: 245-258.

2. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования», стр.: 169-177.

ЗАНЯТИЕ 3.2.3. Назначение, характеристики, состав и работа по функциональной

схеме МПК К589: МБР К589ИР12, СУП К589ИК03, ШФ

К589АП16, ШФИ К589АП26.

ВОПРОСЫ ЗАНЯТИЯ:

1. Назначение, характеристики, состав и работа по функциональной схеме многорежимного буферного регистра (МБР) К589ИР12.

2. Назначение, характеристики, состав и работа по функциональной схеме схемы ускоренного переноса (СУП) К589ИК03.

3. Назначение, характеристики, состав и работа по функциональной схеме шинного формирователя без инверсии (ШФ) К589АП16 и шинного формирователя с инверсией (ШФИ) К589АП26.

ПЕРВЫЙ ВОПРОС

Многорежимный буферный регистр К589ИР12 представляет собой универсальный 8-разрядный регистр с выходами, имеющими третье состояние. Входящие в МБР схема управления режимами и независимый триггер для формирования запроса на прерывание центрального процессора (рис. 1) позволяют использовать его для реализации многих типов интерфейсных и вспомогательных устройств, включая простые регистры данных, буферные регистры со стробированием данных, мультиплексоры, двунаправленные шинные формирователи, прерываемые каналы ввода — вывода и др.

Многорежимный буферный регистр состоит из восьми информационных Д-триггеров, восьми выходных буферных устройств с тремя устойчивыми состояниями, Д-триггера для формирования запроса на прерывание и схемы управления режимами работы регистра.

Данные на информационные триггеры поступают по магистрали Д, а считываются через выходной буферный регистр по магистрали Q. Схемой управления выходные буферы передают информацию на выход при формировании «1» на внутренней магистрали ВД, что достигается следующей комбинацией управляющих сигналов:  .

.

Рис. 1. Схема МБР К589ИК.12 (а) и его условное обозначение (б).

При ВД = 0 выходы схемы находятся в третьем состоянии. Устройство управления МБР позволяет записывать информацию с выходными каскадами, находящимися в третьем состоянии и повторяющими коды входной магистрали. Режим записи информации соответствует уровню «1» на внутренней управляющей магистрали: ЗП = (С/\  )×(

)×(  /\ВК2/\ВР).

/\ВК2/\ВР).

В случае если режим записи обеспечивается сигналами С /\  , выходные каскады находятся в третьем состоянии, при организации записи сигналами

, выходные каскады находятся в третьем состоянии, при организации записи сигналами  BK2/\BP информация входной магистрали подается на выходную магистраль.

BK2/\BP информация входной магистрали подается на выходную магистраль.

Установка информационных триггеров в «0» обеспечивается входным управляющим сигналом R = 0.

Триггер запроса прерывания служит для выработки сигнала запроса на прерывание в процессорной системе. Принято, что МБР находится в состоянии прерывания, когда выходу ЗП соответствует «0».

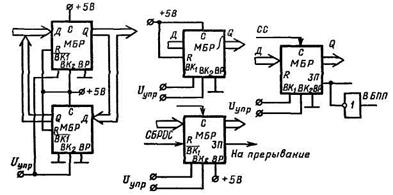

Рис. 2. Примеры использования МБР.

Уровень «1» на триггере запроса прерывания устанавливается при следующих входных сигналах: ЗП = C /\ (  /\

/\  ); уровень «0» устанавливается при

); уровень «0» устанавливается при

ЗП = R V (BK1 V  ).

).

Примеры организации обмена информацией с помощью МБР приведены на рис. 2.

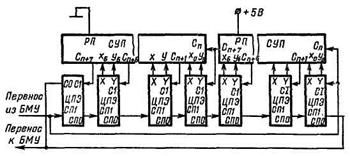

ВТОРОЙ ВОПРОС

Схема ускоренного переноса К589ИК03предназначена для формирования групповых переносов при совместном использовании с ЦПЭ в многоразрядных сумматорах (рис. 4). Одна схема СУП имеет 17 информационных входов и восемь информационных выходов, позволяющих организовать ускоренный перенос для

16-разрядного сумматора. На каждом из выходов СУП сигнал переноса для i-гo разряда формируется согласно уравнению

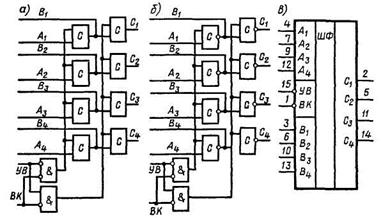

Возможные варианты совместного использования ЦПЭ и СУП представлены на рис. 3.

Рис. 3. Схема использования СУП К589ИК03 совместно с ЦПЭ.

Рис. 4. Структурная схема ускоренного переноса.

Схема имеет 17 информационных входов, 8 информационных выходов и один управляющий вход, позволяющий управлять выходом самого старшего переноса.

В каждом ЦПЭ формируются сигналы подготовки сквозного переноса, которые подаются в схему ускоренного переноса, а она в свою очередь вырабатывает сигналы переносов, поступающие в ЦПЭ. Если в каждом разряде 1, то сигнал подготовки также 1 и через данную секцию происходит перенос от младшей к старшей. Так как схема ускоренного переноса генерирует сигналы переносов во все ЦПЭ одновременно вне зависимости от разрядности, то время суммирования многоразрядных слов существенно сокращается по сравнению с последовательным межсекционным переносом.

ТРЕТИЙ ВОПРОС

Шинные формирователи.Интегральные микросхемы К589АП16 и К589АП26 обеспечивают развязку входов и выходов устройств, работающих на двунаправленную магистраль.

Микросхемы шинных формирователей (ШФ) обеспечивают передачу информации длиной 4 бит по одному из двух направлений.

Микросхемы состоят из набора повторителей (рис. 5, а) или инверторов (рис. 5, б), объединенных общим управлением. Структура ШФ допускает параллельное использование нескольких таких микросхем. Выбирают ту или иную микросхему, т. е. переводят ее в активное состояние сигналом на вход выбора кристалла ВК.

Установка на входе ВК «0» обеспечивает возможность управления выдачей информации по входу УВ.

Данные могут поступать в микросхему по магистралям А или В, а выдаваться — по магистралям В или С. Если на входе УВ установлена «1», то информация со входов B1 — В4 «поступает» на выходы С1 — С4, в противном случае информация со входов А1 — А4 «поступает» на В1 - В4.

Микросхема К589АП26 отличается от микросхемы К589АП16 тем, что входная информация, проходя через инверторы, изменяет свое значение на инверсное.

Рис. 5. Схемы ШФ К589АП16 (а), К589АП26 (б) и их условное обозначение (в)

Литература:

1. Л.Н. Преснухин «Микропроцессоры», ч. 1, стр.: 248, 258-261.

2. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования», стр.: 175-177.

ТЕМА 3.3 Программное обеспечение.

ЗАНЯТИЕ 3.3.1. Классификация команд и режимы адресации.

ВОПРОСЫ ЗАНЯТИЯ:

1. Классификация команд.

2. Способы адресации в микропроцессорах.

3. Режимы адресации.

ПЕРВЫЙ ВОПРОС

Микропроцессор работает по программе, хранимой в ячейках памяти. Содержимое одной или нескольких таких ячеек образует команду МП.

Команда МП – это такое двоичное число, которое, будучи воспринято им, заставит МП выполнить определенные действия. МП может выполнять лишь те действия, которые предусматриваются его командами.

Существуют команды разного назначения. Большинство из них осуществляет пересылку данных, расположенных в памяти или в одном из внутренних регистров МП. Имеются команды, осуществляющие взаимодействие МП с устройствами ввода- вывода; есть и другие команды, предназначенные для управления и выполнения некоторых вспомогательных функций МП.

Вся совокупность команд, воспринимаемых МП, образует его систему команд.

Раньше мы говорили о том, что команды МП .могут иметь различную длину и состоять из 1, 2 или 3 байт. Однако код операции, указывающий на то, что должен делать МП при выполнении данной команды, всегда содержится в ее первом байте и при вводе в МП размещается в регистре команд. Этот код дешифруется и управляет дальнейшими действиями МП. Команда должна указывать МП также адрес или месторасположение данных, подлежащих обработке. Например, МП может получить указания о пересылке содержимого ячейки памяти по заданному адресу в один из внутренних регистров или сдвиге содержимого аккумулятора.

Из приведенных примеров следует, что команда указывает МП не только, что ему необходимо сделать, но и где хранятся и куда должны быть направлены обрабатываемые данные.

Итак, любая команда должна состоять из двух частей: первая часть представляет собой код операции, вторая часть называется адресной. Однако, встречаются так называемые безадресные команды. К ним относится, например, команда останова.

Код операции и адресная часть однобайтных команд размещаются в восьми двоичных разрядах, адресная часть многобайтных команд — во втором и третьем байтах команды. В этих же байтах могут непосредственно размещаться обрабатываемые данные, так что в зависимости от кода операции содержимое второго и третьего байтов может восприниматься как адрес или как данные.

Число команд в системе команд МП значительно больше, чем число кодов операций, поскольку при формировании команды один и тот же код операции может использоваться при различных способах адресации.

В зависимости от назначения команды МП делятся на пять групп:

1) Команды пересылки (выполняют обмен данными между регистрами МП или между регистрами и памятью);

2) Арифметические команды (производят операции сложения, вычитания, инкрементирования или декрементирования данных в регистрах и ячейках памяти;

3) Логические команды (выполняют операции «И», «ИЛИ», «ИЛИ—НЕ», сравнения, сдвига или дополнения данных в регистрах и ячейках памяти);

4) Команды ветвления (производят операции условного и безусловного переходов по программе, вызова подпрограммы и возврата к основной программе);

5) Команды управления и операций со стеком, устройствами ввода — вывода (выполняют операции ввода—вывода, управляют указателем стека и признаками состояний).

Всего система команд МП насчитывает 111 разных команд. Некоторые из них поддаются модификации.

По функциональному назначениюкоманды каждой микроЭВМ, по сравнению с командами МП, можно разделить на следующие группы:

1) команды пересылки данных между оперативной памятью и регистрами микропроцессора;

2) команды для выполнения арифметических и логических операций; 3) команды управления;

4) команды связи с подпрограммами;

5) команды для сдвига данных в регистрах, очистки регистров, формирования дополнительного кода и т. п.;

6) команды ввода/вывода;

7) специальные системные команды.

Команды групп 1 и 2 не требуют особого пояснения. В группу 3 входят команды для проверки признаков результата и осуществления условного или безусловного ветвления. Основное назначение команд этой группы состоит в том, чтобы изменить нормальный ход выполнения программы путем загрузки в счетчик команд такого значения, которое соответствовало бы желаемой точке программы. Команды группы 4 обеспечивают передачу управления на подпрограмму с сохранением информации о том месте программы, из которого произошла передача, а также возврат управления из подпрограммы в исходную программу с восстановлением контекста исходной программы. Команды группы 5 предназначены для выполнения разнообразных унарных операций, т. е. операций с одним операндом по манипулированию данными. По функциональному назначению эти команды близки к командам группы 2. Команды группы 6 обеспечивают обмен данными между оперативной памятью микро-ЭВМ и внешними устройствами. Для таких команд может отсутствовать специальная мнемоника, как это сделано, например, в микро-ЭВМ «Электроника-60». И наконец, команды группы 7 предназначены для выполнения управляющих операций над самим микропроцессором. К таким командам относят команды ожидания, останова, ловушки, управления прерыванием, сброса устройств, а также особая команда NOP (нет операции).

В ЭВМ третьего поколения используются команды с переменной адресностью. Операционная и адресная части команды могут быть различными, что позволяет менять структуру и длину (количество разрядов) команд.

ВТОРОЙ ВОПРОС

В системе команд каждой ЭВМ, в том числе и микроЭВМ, значительное место занимают адресные команды.

Дата добавления: 2015-12-08; просмотров: 2098;