РАЗДЕЛ 3 Программное обеспечение микропроцессорных систем 3 страница

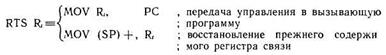

По команде RTS Ri содержимое регистра связи загружается в счетчик команд PC (этим самым обеспечивается возврат в вызывавшую программу) и затем прежнее содержимое регистра связи восстанавливается путем извлечения его из стека.

В качестве регистра связи возможно использование и счетчика команд. В этом случае экономится один регистр общего назначения (его можно применять для других целей).

В виде эквивалентной системы команд обращение и возврат из подпрограммы будут выглядеть следующим образом:

Такой способ связи с подпрограммами практически не накладывает ограничений на глубину вложенности подпрограмм (она зависит лишь от числа ячеек памяти, отведенных под стек) и способы обращений. Не существует ограничений и для обращения подпрограммы самой к себе — рекурсивное обращение. Использование рекурсивных обращений позволяет создавать компактные и эффективные программы обработки данных.

Обмен данными с внешними устройствами.Обмен данными между процессором и внешними устройствами осуществляется с помощью стандартных циклов магистрали. Каждое внешнее устройство должно иметь как минимум два регистра: регистр команд и состояний и буферный

регистр данных За каждым регистром закрепляется один из четных адресов на общей Магистрали, принадлежащий области последних 4К слов адресного пространства.

Обмен данными рассмотрим на примере взаимодействия процессора и дисплея, являющегося стандартным системным устройством. Дисплей рассматривается как прибор, состоящий из двух совершенно независимых устройств (клавиатуры и устройства отображения на экране). Каждое устройство имеет свои два регистра.

Рассмотрим программный Способ передачи данных.

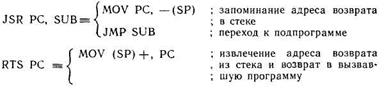

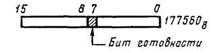

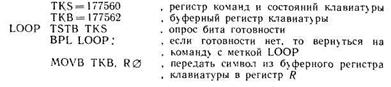

Формат регистра команд и состояний клавиатуры имеет вид

Седьмой бит регистра команд и состояний, называемый битом готовности, имеет следующий смысл: БИТ [7] = 1 показывает, что была нажата клавиша, БИТ [7] =0 показывает, что клавиша не нажималась.

В случае нажатия одной из клавиш клавиатуры дисплея бит готовности устанавливается в 1 и код символа, соответствующий нажатой клавише, пересылается в буферный регистр ввода клавиатуры.

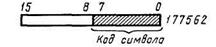

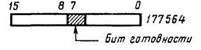

Формат буферного регистра ввода клавиатуры имеет вид

Справа от регистров указаны их восьмеричные адреса на общей магистрали.

На языке ассемблера процесс ввода одного символа с клавиатуры дисплея в регистр R0 описывается следующим образом:

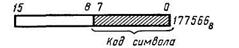

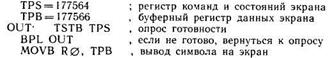

Аналогично происходит и процесс вывода символа на экран.

Формат регистра команд и состояний устройства отображения на экране имеет вид

Бит готовности принимает значение 1 в том случае, когда устройство готово принять символ для вывода на экран. В процессе вывода символа на экран бит готовности сбрасывается устройством в 0 и по окончании вывода снова устанавливается им в 1.

Формат буферного регистра вывода на экран имеет вид

Если необходимо вывести на экран дисплея младший байт регистра R0, то программа на языке ассемблера будет выглядеть следующим образом:

Форматы регистров данных нестандартной аппаратуры в основном определяются разработчиком. Для регистров команд и состояний рекомендуется общий формат, которым следует руководствоваться при разработке аппаратуры.

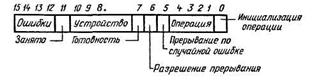

Общий формат регистра команд и состояний таков:

Разряды 15—12 используются для сигнализации о наличии ошибки (разряд 15) и о характере ошибки (14—12). Они устанавливаются внешним устройством. Разряд 11 сигнализирует о том, что внешнее устройство занято выполнением внутренних операций и не может принять участия в обмене данными. Разряды 10—8 применяются для выбора устройств, подключенных к общему контроллеру. Разряды 7—5 являются разрядами условий и служат для программного определения состояний устройства и управления прерыванием. Для определения функции, выполняемой внешним устройством, служат разряды 4—1. Разряд 0 служит для инициирования (запуска) операции.

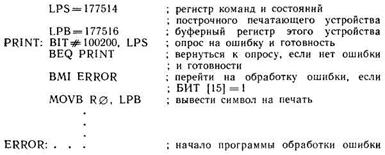

Рассмотрим программу вывода одного символа на построчное печатающее устройство с анализом бита ошибки:

Система прерывания,прерывание — непредусмотренное обращение к подпрограмме. Микро-ЭВМ имеет два вида прерываний: внутренние и внешние. Внутренние прерывания происходят по инициативе процессора при возникновении в нем необычных ситуаций, а внешние прерывания — по требованию устройств ввода — вывода, подсоединенных к общей магистрали.

Внешние прерывания. Разрешением запроса на внешнее прерывание от конкретного устройства управляет БИТ [6] регистра команд и состояний этого устройства.

Сигнал запроса на прерывание формируется в двух случаях: 1) бит разрешения прерывания установлен (БИТ [6] = 1), а бит готовности (БИТ [7])переходит из состояния 0 в состояние 1; 2) бит готовности установлен (БИТ [7] =1), а бит разрешения прерывания (БИТ [6]) переходит из состояния 0 в состояние 1.

Установка и сброс бита разрешения прерывания осуществляются программным способом. При начальном пуске машины, а также при выполнении команды RESET вырабатывается на общей магистрали импульс INIT, который сбрасывает в нуль биты разрешения прерывания в регистрах команд и состояний всех устройств, подсоединенных к общей магистрали. Запросы на прерывание процессора от внешних устройств могут быть удовлетворены только в том случае, если седьмой бит регистра состояния процессора равен нулю (PSR [7] =0). В противном случае (PSR [7] =1) все запросы на прерывание игнорируются (замаскированы).

Линия разрешения прерывания от процессора проходит последовательно через все внешние устройства. Таким образом, приоритет устройств понижается по мере удаления от процессора. Любое устройство, которое может прервать процессор, может также прервать выполнение программы обслуживания устройства с более низким приоритетом, если PSR [7] =0. При такой структуре возможно вложение прерываний любого уровня (число вложений ограничивается лишь числом ячеек памяти, отведенных под стек).

Каждому внешнему устройству, подсоединенному к общей магистрали, ставится в соответствие своя пара ячеек оперативной памяти, называемая вектором прерывания. Первое слово вектора прерывания содержит адрес начала подпрограммы обработки прерывания для данного устройства, а второе слово — содержимое регистра состояния процессора для этой подпрограммы. Обычно второе слово в этом случае хранит информацию о значении седьмого бита — бита разрешения прерывания. Если этот бит равен единице, то прерывание от устройства с более высоким приоритетом будет запрещено на время работы программы обработки прерывания. Каждое внешнее устройство, способное работать по прерыванию, имеет свой «запаянный» вектор, числовое значение которого соответствует адресу первого слова вектора прерывания в оперативной памяти. В случае удовлетворения запроса на прерывание устройство посылает свой вектор прерывания в процессор, тем самым сообщая процессору адрес начала подпрограммы обслуживания прерывания для этого устройства и состояние процессора.

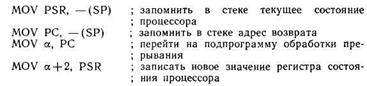

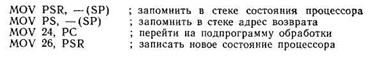

Действия, которые выполняет процессор после получения вектора прерывания, можно описать с помощью эквивалентной системы команд:

где α— адрес вектора прерывания.

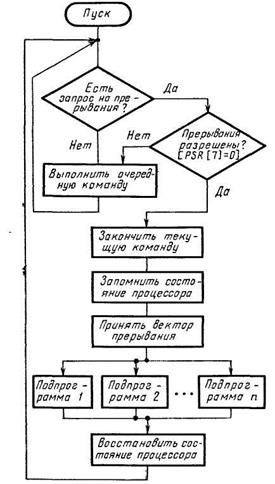

Схема, приведенная на рис. 6, поясняет принцип работы микро-ЭВМ по прерыванию.

Рис. 6. Схема системы прерывания микро-ЭВМ.

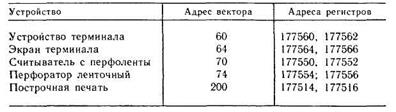

Таблица 2.

Адреса векторов внешних прерываний и адреса регистров основных системных устройств приведены в табл. 2.

В качестве примера использования системы прерывания приведем программу, обеспечивающую работу системного терминала в режиме электрифицированной пишущей машинки во время выполнения некоторой фоновой программы:

Всякий раз при нажатии клавиши выполнение фоновой программы приостанавливается и происходит передача управления по вектору прерывания, расположенному в ячейке памяти с адресом 60.

После печати символа по команде RTI происходит возврат к прерванному месту фоновой программы и продолжение ее выполнения.

Внутренние прерывания. Возникают в случае возникновения необычных ситуаций в процессоре (ошибка магистрали, резервная или запрещенная команда, установлен бит слежения Т в регистре состояния процессора, сбой питания) или в случае появления в программе команд IOТ, ЕМТ, TRAP. Механизм внутренних прерываний аналогичен механизму внешних прерываний. Например, выход напряжения или частоты питающей сети за допустимые пределы вызывает внутреннее прерывание, действие которого можно описать с помощью системы команд:

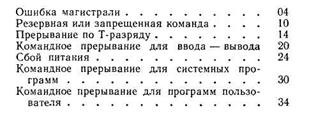

Причины, вызывающие прерывания и адреса векторов внутренних прерываний, приведены ниже:

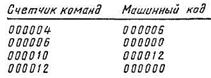

Самый простой случай использования внутренних прерываний — организация ловушек останова. Например, чтобы организовать останов процессора при возникновении ошибки магистрали или появлении в программе резервной или запрещенной команды, достаточно включить в программу строки

Результатом трансляции этих строк будет следующая информация в ячейках памяти:

Как видно, каждая подпрограмма обработки прерывания состоит из единственной команды останова HALT.

ЕМТ- и TRAP-команды используются в качестве эффективного средства организации и вызова подпрограмм. Любая из 25610. ЕМТ-команд с машинными кодами 1040008—1043778 вызывает внутреннее прерывание по вектору, расположенному по адресу 308. Соответствующим образом написанная подпрограмма обработки прерывания (подпрограмма-диспетчер) обеспечивает вызов одной из 25610 подпрограмм согласно коду младшего байта ЕМТ-команды.

Обычный вызов подпрограммы с помощью команды JSR R,-, SUB требует двух ячеек памяти, вызов же подпрограммы с помощью ЕМТ-команды занимает одну ячейку памяти. В сложных программах, построенных по модульному принципу, вызовы подпрограмм занимают значительное место, поэтому применение ЕМТ- и TRAP-команд позволяет получить существенную экономию ячеек памяти.

Сетевой таймер (часы реального времени).Для организации измерения временных интервалов в микроЭВМ реализовано внутреннее прерывание по таймеру с вектором, находящимся по адресу 1008. Если таймер включен, то на линию прерывания по таймеру поступают импульсы с частотой питающей сети 50 Гц или с периодом 0,02 с. Подпрограмма обслуживания прерывания по таймеру обеспечивает накопление и подсчет импульсов («тиков») в некоторой выбранной ячейке памяти. Для обеспечения достаточной емкости таймера вместо одной ячейки памяти применяют две. Для реализации арифметической операции с удвоенной разрядностью используется команда ADC — прибавление переноса.

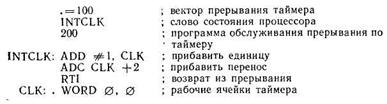

Программа обслуживания таймера на языке ассемблера может быть написана так:

Емкость таймера в этом случае составит более 20 000 ч. Действительно, максимальное число, которое можно записать в 32 двоичных разрядах, N = 232—1 = = 4 294 967 295. Отсюда максимальная емкость таймера T = 4 294 967 295/ (50 -3600) =23 859 ч.

Литература:

1. Л.Н. Преснухин «Микропроцессоры» часть 2, стр.: 171-177, 180-212.

ЗАНЯТИЕ 3.1.3. Структурная схема, характеристики и основная элементная база

микроЭВМ «Электроника-60».

ВОПРОСЫ ЗАНЯТИЯ:

1. Назначение, состав, характеристики и структурная схема микроЭВМ «Электроника-60».

2. Устройства микроЭВМ и их элементная база.

3. Особенности функционирования микроЭВМ «Электроника-60.

ПЕРВЫЙ ВОПРОС

МикроЭВМ «Электроника-60» предназначена для обработки информации и может быть использована в системах управления технологическими процессами в составе испытательного оборудования, а также для научно-техническихи экономических расчетов.

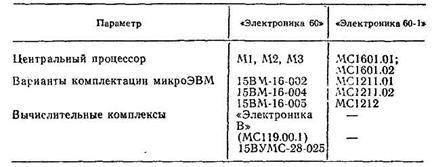

Семейство включает в себя серии микроЭВМ двух исполнений: «Электроника 60», «Электроника 60-1».

Отдельные модели микроЭВМ внутри серии конструктивно совместимы, имеют набор базового ряда комплекта БИС, единый состав (набор) программного обеспечения, достаточно близкие наборы команд, ориентированы на конкретную область применения. Второе поколение микроЭВМ является логическим развитием основных концепций первого. Все модели данного семейства выполнены в полном соответствии с основными принципами операций, реализованными в базовой микроЭВМ.

Все микроЭВМ «Электроника 60», «Электроника 60-1» различаются реализацией ЦП (модули Ml, M2, соответственно), которые, в свою очередь, отличаются набором команд, быстродействием, степенью интеграции и объемом резидентной памяти.

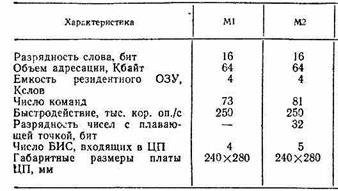

Основные характеристики модулей центральных процессоров типа М1, М2.

Упрощенная стpyктурная схема микроЭВМ «Электроника-60» приведена на рисунке.

Структура ЭВМ разработана по модальному принципу, то есть все функциональные блоки выполнены в виде конструктивно законченных устройств (модулей), связь между которыми осуществляется через единый канал обмена информацией.

В состав микроЭВМ «Электроника-60» кроме процессора могут входить устройства управления пишущей машинкой и устройства управления перфовводом и перфовыводом. В качестве внешних устройств используются электрическая пишущая машинка «Консул-260», фотосчитыватель, FS-1501 и перфоратор ПЛ-150.

Возможно подключение других внешних устройств НГМД, АЦПУ, а также устройств пользователя, разработанных с учетом требований интерфейса.

Конфигурация системы определяется пользователем и зависит от конкретного применения.

ВТОРОЙ ВОПРОС

Отдельные модели микроЭВМ внутри серии конструктивно совместимы, имеют набор базового ряда комплекта БИС, единый состав (набор) программного обеспечения, достаточно близкие наборы команд, ориентированы на конкретную область применения. Второе поколение микроЭВМ является логическим развитием основных концепций первого. Все модели данного семейства выполнены в полном соответствии с основными принципами операций, реализованными в базовой микроЭВМ.

Базовый комплект БИС. Системотехнической основой построения микроЭВМ серии «Электроника 60» является МПК БИС серии 581, в состав которого входят следующие БИС:

КР581ИК2 (БИС управления) — осуществляет связь регистрового АЛУ процессора с линиями управляющих сигналов канала микроЭВМ и генерирует последовательность адресов микрокоманд, по которым производится обращение к БИС микрокомандного ПЗУ;

КР581ИК1 (БИС регистрового АЛУ) – выполняет арифметико-логические преобразования над данными и осуществляет информационный обмен с каналом микроЭВМ;

КР581РУ1, КР581РУ2 (БИС микрокомандного ПЗУ) – хранит микрокоманды, эмулирующие систему команд «Электроника 60», операции связи с пультовым терминалом и программу начального загрузчика.

Центральные процессоры Ml — М2 выполняют 73 команды в формате с фиксированной точкой, М2 дополнительно реализует 8 команд: 4 команды расширенной арифметики с фиксированной точкой (умножение, деление, арифметический сдвиг 16-разрядного слова, арифметический сдвиг 32-разрядного слова); 4 команды для выполнения операций над числами с плавающей точкой (сложение, вычитание, умножение, деление).

Модули ОЗУ. Основные модули ОЗУ (динамического типа) являются модули П1, П2, различающиеся емкостью, быстродействием, потребляемой мощностью и типом применяемых БИС.

Характеристики основных модулей ОЗУ

Адреса модулей памяти устанавливаются с помощью микропереключателей на модуле, в том числе в диапазоне 32...128 Кслов. Для этого применяют расширяющие адресные разряды РАД16, РАД17, которые можно устанавливать модульным переключателем.

Модули ППЗУ и ПЗУ. В модулях ППЗУ ультрафиолетовое стирание информации осуществляется в течение 30 мин (длина волны 400 нм). В блоках применено импульсное питание микросхем памяти (серия К573), причем только тех, к которым производится обращение. Микросхемы устанавливаются в модуль ППЗУ с помощью 16 колодок (розеток) на 24 вывода каждая.

Модуль ПЗУ типа ПП1 содержит 32 БИС ПЗУ серии К556, установленных на колодках, схемы адресаты и управления. Номер банка памяти устанавливается с помощью микропереключателей В1. Возможно использование модуля с неполной емкостью ПЗУ (с помощью микропереключателей В2). Тип микросхем определяется микропереключателем ВЗ.

Характеристики основных модулей ППЗУ и ПЗУ

ТРЕТИЙ ВОПРОС

Канал обмена информацией соединяет процессор, память и все внешние устройства. Канал («ОБЩАЯ ШИНА») содержит 39 линий связи, из которых 32 являются двунаправленными.

Связь между двумя устройствами, подключенными к шине, осуществляется по принципу управляющий – управляемый. В любой момент времени активным может быть только одно устройство. Активное устройство управляет циклами обращения и каналами, удовлетворяет по мере необходимости требованиям на прерывания от внешних устройств, контролирует представление прямого доступа к памяти. Пассивное устройство всегда является исполнительным и может принимать или передавать информацию только под управлением активного устройства.

Процессор всегда является активным устройством, а память – пассивным. Остальные устройства могут попеременно работать в активном и пассивном режимах. Связь по шине всегда замкнута.

На управляющий сигнал, передаваемый активным устройством, должен поступать ответ от пассивного устройства. Асинхронное выполнение операции передачи данных устраняет необходимость в тактовых импульсах и позволяет осуществлять обмен с максимально возможной скоростью. Обмен данными между двумя устройствами может выполняться как 16-разрядными словами, так и байтами. Обмен данными между устройством пользователя и ЭВМ может выполняться в трех различных режимах: в программном режиме, в режиме прямого доступа к памяти, в режиме прерывания программы.

Процессор «Электроника-60» управляет общей шиной, внешними устройствами и выполняет арифметико-логические операции. Процессор содержит восемь 16-разрядных регистров общего назначения (РОН), которые могут использоваться в качестве накопительных и индексных регистров и указателей стека. Из числа указанных РОН два имеют специальное назначение. РОН6 используется как указатель аппаратного стека, а РОН7 – как счетчик команд.

Основной единицей представления информации является 16-разрядное слово. Имеется возможность также работать с байтами. Команда может состоять из одного, двух или трех 16-разрядных слов. Второе и третье слово интерпретируются как непосредственный операнд либо как адрес.

Набор команд аналогичен в основном базовому набору команд СМ-4. Более мощные модели микроЭВМ, имеющие расширенный набор команд , который позволяет решать задачи с фиксированной и плавающей точками. В отличие от малых ЭВМ в микроЭВМ имеется два кода специальных команд обращения к слову состояния программы по записи и чтению.

Адрес имеет 16 разрядов, что позволяет адресовать память объемом до 64 К байт. Номинальная емкость ОП определяется шестнадцатью адресами слов.

МикроЭВМ типа «Электроника 60» относятся к классу многорегистровых микроЭВМ с единой магистралью. Они предназначены для обработки информации и могут использоваться: для научно-технических и экономических расчетов; в составе испытательного и контрольно-измерительного оборудования; в системах управления технологическими процессами; автоматизации научных экспериментов; в качестве ЭВМ предварительной обработки информации при совместной работе с малыми ЭВМ систем СМ ЭВМ.

Режимы адресации и система команд микроЭВМ «Электроника-60» будут рассмотрены в лекции 6.3.1.

Литература:

1. А.Л. Неня «Принципы действия и применение микропроцессоров и микроЭВМ», стр.: 22-24.

2. А.А. Мячев «Персональные ЭВМ и микроЭВМ (основы организации)», стр.: 230-239.

ТЕМА 3.2. Микропроцессорные комплекты (МПК).

ЗАНЯТИЕ 6.2.1. Микропроцессорные комплекты и их функциональный состав.

Назначение, состав и характеристики МПК серии К589.

ВОПРОСЫ ЗАНЯТИЯ:

1. Основные микропроцессорные комплекты и их функциональный состав.

2. Секционированный микропроцессорный комплект БИС серии К589.

ПЕРВЫЙ ВОПРОС

Наибольшее распространение получили микропроцессоры, управляемые по программам или микропрограммам. Такие МП строятся на базе ЭСЛ, ТТЛШ, КМОП, И2Л и других распространенных логических элементов. Современные микропроцессоры представляют собой набор БИС, соединенных между собой определенным образом, которые составляют так называемые микропроцессорные комплекты (МПК).

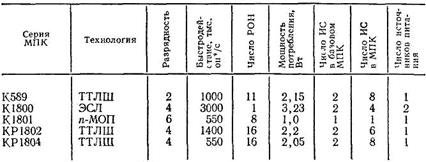

За последние годы разработано значительное количество различных МПК. Сравнительные обобщенные характеристики некоторых из них приведены в табл. 1.

Таблица 10.1

Микропроцессорные комплекты изготовляют в виде секционных БИС с возможностью наращивания. Исключение составляет БИС КР580ИК80А – восьмиразрядный МП, в котором можно увеличить разрядность обрабатываемых данных путем двойного пересчета.

В состав секционных МПК входят, как правило, n-разрядная МП секция, предназначенная для обработки информации и временного хранения результатов, схема микропрограммного УУ, а также БИС, выполняющие функции по обработке прерываний программы, синхронизации и связи с периферийными устройствами.

Возможность наращивания разрядности обрабатываемой информации и применение микропрограмм обеспечивают гибкость и широкую сферу применения секционных МПК, так как разработчик аппаратуры сам может определять набор команд.

В структуре МП можно выделить операционную и управляющую части. Операционная часть проводит логическую обработку информации, управляющая часть декодирует команды и формирует сигналы, необходимые для выполнения той или иной операции. Каждая команда представляет собой небольшую программу, состоящую из элементарных операций. Последовательность таких команд называется микропрограммой. Очередность команд, в соответствии с которой работает управляющая часть МП, называется программой.

Первые МП строились на р-канальных МОП-транзисторах, поэтому имели невысокое быстродействие. В дальнейшем появились МП, в которых использовались n-канальные МОП-транзисторы и биполярные интегральные структуры (И2Л, ТТЛШ и ЭСЛ), что привело к значительному увеличению быстродействия.

Количество различных операций, выполняемых некоторыми МП, доходит до 100, причем в них предусматриваются операции с двойной длиной слова и побайтовой обработкой информации. В процессе развития наряду с МП, имеющими фиксированный список команд, появились МП с микропрограммным управлением, которое позволяет изменять список команд и алгоритмы управления. Это увеличивает гибкость процессора и упрощает реализацию последовательности относительно сложных микрокоманд.

Важнейший параметр МП — быстродействие. В настоящее время диапазон быстродействия МП — от десятков тысяч до 1—3 млн. коротких операций.

Отечественная промышленность выпускает секционированные микропроцессорные комплекты серий К589, КР1802, КР1804, K1800 и др.

ВТОРОЙ ВОПРОС

Интегральные микросхемы серии К589 представляют собой комплект электрически и конструктивно совместимых микросхем, предназначенных для построения высокопроизводительных модульных микропроцессоров с микропрограммной архитектурой.

Микропроцессорный комплект БИС серии К589 состоит из восьми микросхем, выполненных по ТТЛШ-технологии:

- блока микропрограммного управления (БМУ) К589ИК01;

- центрального процессорного элемента (ЦПЭ) К589ИК02;

- схем ускоренного переноса (СУП) К589ИК03;

- многорежимного буферного регистра (МБР) К589ИР12;

- блока приоритетных прерываний (БПП) К589ИК14;

- шинных формирователей без инверсий (ШФ) К589АП16 и с инверсией

(ШФИ) К589АШ6;

- схемы синхронизации и управления (МСУ) К589ХЛ4.

Комплект обеспечивает построение автономных микро- и миниЭВМ, контроллеров, устройств автоматики с различной архитектурой благодаря модульности структуры, возможности параллельного наращивания микропрограммного управления, совместимости с ТТЛ-транзисторами серии К155 и др.

Микросхемы герметизированы в пластмассовых корпусах с вертикальным расположением выводов.

Соединяя параллельно несколько МП, можно получить процессор с требуемой длиной слова. Для реализации 16-разрядного процессора, содержащего УУ, шины и микропрограммное ЗУ, требуется примерно 20 БИС и 10 ИС. Такой процессор заменяет эквивалентную систему на ТТЛ ИС среднего уровня интеграции, имеющую более 200 корпусов. Центральный процессор (ЦП) в нем состоит из восьми микросхем ЦПЭ, одного БМУ, ЗУМК.

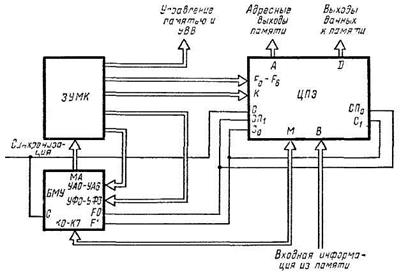

На рис. 1 показана структурная схема такого процессора. Микропрограмма, находящаяся в управляющей памяти, после включения питания устанавливает ЦП в исходное состояние и осуществляет выборку и выполнение команд. Разрядность слова микропрограммной памяти определяется числом и разрядностью микроинструкций.

Центральный процессорный элемент имеет шесть групп входов и выходов, по которым происходит связь с другими схемами. Четыре из них (В, М, A, D) используются преимущественно для связи с внешней памятью и устройствами ввода- вывода. Группа выводов F0 - F6 используется для управления работой ЦПЭ, а входы К – для маскирования информации для занесения константы.

Рис. 1. Структурная схема МП, выполненного на основе серии К589.

Литература:

1. Л.Н. Преснухин «Микропроцессоры», ч. 1, стр.: 245-261.

2. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования», стр.: 167-177.

ЗАНЯТИЕ 3.2.2. Назначение, характеристики, состав и работа по функциональной

схеме МПК К589: ЦПЭ К589ИК02, БМУ К589ИК01,

БПП К589ИК14.

ВОПРОСЫ ЗАНЯТИЯ:

1. Назначение, характеристики, состав и работа по функциональной схеме центрального процессорного элемента (ЦПЭ) К589ИК02.

2. Назначение, характеристики, состав и работа по функциональной схеме блока микропрограммного управления (БМУ) К589ИК01.

3. Назначение, характеристики, состав и работа по функциональной схеме блока приоритетных прерываний (БПП) К589ИК14.

ПЕРВЫЙ ВОПРОС

Центральный процессорный элемент К589ИК02представляет собой двухразрядную секцию операционного узла, допускающую объединение аналогичных ЦПЭдля увеличения разрядности обрабатываемых слов.

В состав ЦПЭ (рис. 1) входят сверхоперативное запоминающее устройство СОЗУ, состоящее из 11 регистров общего назначения (R0 — R 9 и Т), регистр адреса РА, регистр аккумулятор АС, арифметическо-логический блок АЛБ, два мультиплексора МС1и МС2, дешифратор выполняемых функций и буферные схемы выходных магистралей.

Дата добавления: 2015-12-08; просмотров: 1966;