Режимы адресации памяти микро-ЭВМ «Электроника-60», основанные на использовании регистра с номером 7 как счетчика команд.

При выполнении операции, указанной в текущей команде, счетчик команд содержит адрес следующей команды. Применительно к фазе выборки операндов это утверждение в общем случае несправедливо, так как, например, в двухсловных и трехсловных командах счетчик команд последовательно адресует сначала первое слово, затем второе и третье и только после этого в нем формируется адрес следующей команды. Используя счетчик команд, как и всякий регистр общего назначения, и учитывая его функцию, можно реализовать дополнительные режимы адресации. Хотя формально при этом существует восемь таких режимов, полезны из них только четыре:

2 Непосредственный # n

3 Абсолютный * # n

6 Относительный А

7 Относительный косвенный * А

Непосредственный режимпозволяет задавать константу в качестве одного из операндов. Значение константы запоминается в слове, следующем за первым (основным) словом команды. Следовательно, в целом команда становится двухсловной.

Таким образом, символическое обозначение непосредственного режима — это сокращенная запись, в которой использование регистра 7 предполагается по принципу умолчания.

Абсолютный режимимеет уровень косвенной адресации, равный 1.

Константа, запоминаемая в памяти вслед за словом команды, используется для адресации операнда. Этот режим чаще всего применяется для доступа к операндам, хранящимся по заранее известным адресам памяти.

При относительном режимеадресация операнда осуществляется относительно текущего значения счетчика команд, трактуемого в этом случае как индексный регистр. Например, команда

MOV 76(PC), R2,

имеющая адрес 1500, осуществляет загрузку в регистр R2 содержимого слова памяти, имеющего адрес 1602 (все адреса и данные считаются восьмеричными числами). Записанное в команде число 76 представляет собой положительное смещение, которое надо прибавить к текущему содержимому счетчика команд для получения эффективного адреса первого операнда. Значение смещения хранится в слове, следующем за первым (основным) словом команды. Следовательно, при выборке содержимого второго слова счетчик команд будет хранить адрес 1504. При этом 1504 -(- 76=1602 в восьмеричной системе счисления, а это и есть адрес первого операнда. В приведенном примере команды смещение записано в явном виде. Однако в действительности оно не всегда заранее известно. Другое неудобство записи смещения в явном виде состоит в том, что при отладке и изменении текста программы значение смещения может измениться. Чтобы избавить программиста от необходимости всякий раз подсчитывать и записывать смещение в команде, относительный режим адресации предусматривает использование символических имен операндов. В этом случае смещение подсчитывает ассемблер на этапе трансляции программы. Относительный косвенный режим характеризуется уровнем косвенной адресации, равным двум. В этом случае, как и в относительном режиме, в команде используется символическое имя, которому должен предшествовать признаку. Слово памяти, которому присвоено записанное в команде имя, содержит адрес операнда. Режим адресации памяти, использующий регистр с номером 6 для хранения указателя стека.Как отмечалось выше, автоинкрементный и автодекрементный косвенные режимы удобны для выполнения операций над особой структурой данных – стеком. В микро-ЭВМ «Электроника-60» стек организуется в оперативной памяти. Для этой цели чаще выбирают адреса слов 400—476. Выполнение основных операций над стеком (включение элемента в стек и исключение элемента из него) осуществляется с помощью указателя стека, представляющего собой адрес «верхнего» доступного элемента в стеке. Обычно для хранения указателя стека используется регистр 6, которому присваивается имя SP.

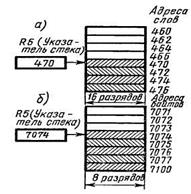

Перед началом работы ЭВМ стек пуст, а указателю стека присваивается значение наибольшего адреса слова в той области памяти, которая отведена для стека (чаще начальное значение указателя стека равно 500). При включении элемента (слова) в стек значение указателя сначала уменьшается на два, а затем по адресу, равному значению указателя, записывается нужный элемент. При включении элемента из стека значение исключаемого элемента считывается по адресу, равному текущему значению указателя стека, после чего осуществляется увеличение значения указателя на два.

Используя любой из регистров (R0—R5), можно организовать стек, элементами которого могут быть не слова, а байты. Структуры пословного (а) и байтного (б) стеков показаны на рис. 9. На рисунке заштрихованы занятые элементы стеков.

Рис. 9. Структура пословного (а) и байтного (б) стеков.

Литература:

1. Л.Н. Преснухин «Микропроцессоры» ч. 1, стр.: 357-379.

2. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования», стр.: 139-141.

3. Б.Я. Лихтциндер «Микропроцессоры и вычислительные устройства в радиотехнике», стр.: 134-150.

ЗАНЯТИЕ 3.3.2. Языки программирования.

ВОПРОСЫ ЗАНЯТИЯ:

1. Языки программирования.

2. Средства программирования.

ПЕРВЫЙ ВОПРОС

Языки программирования для микроЭВМ можно разделить на три основных уровня: машинные, алгоритмические высокого уровня и ассемблера.

Машинные языки находятся на самом нижнем уровне иерархии языков программирования и им свойствен следующий недостаток. Будучи языками цифр, они неудобны для описания вычислительных процессов, требуют от программистов больших усилий при написании и отладке программ. Достоинство машинного языка - для программирования на нем требуется лишь знание системы команд ЭВМ, а для выполнения составленных таким образом программ вычислительная машина не нуждается ни в каком трансляторе. Кроме того, при использовании машинного языка можно достигнуть максимальной гибкости в реализации технических возможностей ЭВМ.

Алгоритмические языки высокого уровня (например, ФОРТРАН, БЕЙСИК, ПЛ/М, ПАСКАЛЬ, АДА и др.) занимают верхнее положение в иерархии языков программирования. Будучи приближенными к привычной математической нотации и в ряде случаев обеспечивая естественную форму описания вычислительных процессов, они достаточно просты и удобны в программировании, но не всегда позволяют в полной мере реализовать технические возможности ЭВМ, а результирующие машинные программы, получаемые после трансляции программ с алгоритмических языков, обычно неэффективны с точки зрения объема или быстродействия. Недостаток таких языков заключается в том, что их применение предполагает наличие транслятора, представляющего собой сложный программный комплекс и требующего для своей разработки большого труда. Тем не менее, вследствие своих неоспоримых достоинств алгоритмические языки высокого уровня широко применяются в программировании для различных классов микроЭВМ.

Языки ассемблера, занимая промежуточное положение между машинными языками и языками высокого уровня (будучи при этом гораздо ближе к машинным языкам), объединяют в себе некоторые достоинства самого нижнего и самого верхнего уровней языков программирования. Свое название языки ассемблера получили от имени программы, преобразующей программу на таком языке, в машинные коды.

Язык Ассемблер, обеспечивая возможность использования символических имен в программе и избавляя программиста от утомительной работы по распределению памяти ЭВМ для переменных и констант, существенно облегчает труд программиста, повышает производительность по сравнению с программированием на машинном языке. Язык Ассемблер позволяет гибко и полно реализовать технические возможности ЭВМ, как и машинный язык. Транслятор программ с языка Ассемблера гораздо проще и компактней транслятора программ, требующегося для алгоритмического языка высокого уровня, а результирующая машинная программа на выходе ассемблера может быть столь же эффективной, как и программа, которую сразу написали на машинном языке.

Каждый язык ассемблера является машинно-зависимым и отражает аппаратурные особенности (в частности, состав программно-доступных регистров) той микроЭВМ, для которой он создан.

Программа, написанная на языке Ассемблер, состоит из последовательности предложений, или операторов, и называется исходной программой или исходным модулем.

Одна из тенденций развития языков программирования – более широкое использование непроцедурных или описательных языков. Описательная программа констатирует, какой результат желателен, не указывая, как этого достичь. В программе формулируются соотношения, а не последовательность вычислений, и, таким образом, программист освобождается от обязанности разрабатывать шаги алгоритма и определять их порядок. Наиболее известные непроцедурные языки: Визикальк, Мультиплан, Пролог.

Другое направление, по которому развиваются языки программирования, использование параллельных вычислений в мультипроцессорных системах. Казалось бы, что 100 процессоров должны решить задачу в 100 раз быстрее, чем один. Но такого ускорения можно достичь только тогда, когда программное обеспечение способно разбить задачу на много частей, которые могут решаться одновременно.

В некоторых языках предусмотрены явные способы указания заданий, которые могли бы выполняться параллельно. В других языках предполагается, что компилятор будет анализировать и выявлять то, что поддается распараллеливанию. Одним из таких языков является язык Компел.

Среди огромного разнообразия языков программирования не существует самого лучшего или самого худшего. Выбор языка программирования в каждом конкретном случае определяется целями его предполагаемого применения.

ВТОРОЙ ВОПРОС

Имеется пять классов средств программирования:

- редактирующие программы,

- транслирующие программы,

- программы-загрузчики,

- моделирующие программы,

- отладочные программы.

Каждый из этих классов облегчает выполнение некоторого этапа разработки программ. Редактирующие программы облегчают создание исходной программы. С помощью транслирующих программ из исходной получают объектную программу, т. е. программу на машинном языке. Загрузчики переносят объектную программу из внешней памяти, например перфоленты, в память микроЭВМ. Моделирующие программы позволяют проверить значительную часть объектной программы при отсутствии микроЭВМ. Отладочные программы облегчают отладку объектной программы на микроЭВМ.

Все эти средства программирования делятся на кросс-средства и резидентные. Кросс-средства — это программы, которые выполняются не на микроЭВМ, для которой разрабатывается программное обеспечение, а на какой-либо другой машине. Резидентные средства — это программы, которые выполняются на микропроцессоре, для которого разрабатывается программное обеспечение.

Рассмотрим подробнее перечисленные классы средств программирования.

Редактирующие программы –это программы, облегчающие создание исходных программ. Редактирующая программа принимает исходную программу, обычно вводимую в ЭВМ с клавиатуры (иногда с перфоленты), и записывает часть этой программы во внешнюю память ЭВМ, например на диск или магнитную ленту.

Редактирующая программа выполняет также специальные команды пользователя по добавлению, исключению или замене частей исходно программы, хранимой во внешней памяти. Редактирующие программы оперируют с исходной программой как с текстом, совершенно не учитывая те синтаксические правила, которым должна удовлетворять программа.

Редактирующие программы различаются возможностями, которые они предоставляют для выполнения изменений в программе. Например, некоторые редактирующие программы могут оперировать только с целыми строками программы, другие — могут добавлять, исключать или заменять в программе произвольные последовательности символов.

Транслирующие программы обеспечивают получение объектной программы из программы, написанной на языке высокого уровня.

Важно различать язык программирования и реализацию языка. Язык программирования — это система записи, набор правил, определяющих синтаксис правильной программы. Реализация языка — это программа, которая преобразует запись высокого уровня: в последовательность машинных команд.

Имеются два основных вида средств реализации языка (транслирующих программ): компиляторы и интерпретаторы.

Компиляторы транслируют вес текст программы, написанной на языке высокой уровня, в машинный код в ходе одного непрерывного процесса. При этом создается полная программа в машинных кодах, которую затем можно выполнить безучастия компилятора. Обычно работа с компилируемым языком состоит из трех этапов: сначала текс программы создается при помощи редактора текст или какой-либо другой программы текстовой обработки, затем текст компилируется, и наконец, скомпилированная программа выполняется.

Интерпретатор — это программа, осуществляющая пошаговую трансляцию входной программы с последующим исполнением машинной программы, полученной на каждом шаге трансляции. Разница между компилятором и интерпретатором подобна разнице между переводчиком литературы и переводчиком устной речи. Переводчик литературы берет всю книгу и создает новый текст на другом языке. Переводчик устной речи переводит каждую фразу, как только она произнесена.

Для выполнения интерпретируемой программы интерпретатор должен находиться в основной памяти, в то время как для скомпилированной программы компилятор уже не нужен.

В принципе любой язык программирования может быть как интерпретируемым, так и компилируемым, но в большинстве случаев по традиции у каждого языка есть свой предпочтительный способ реализации.

Основное преимущество компиляции – высокая скорость выполнения готовой программы, поскольку интерпретатор должен строить соответствующую последовательность команд в момент, когда инструкция выполняется.

Интерпретируемый язык неизбежно медленнее компилируемого. В то же время интерпретируемый язык часто более удобен для программиста. Он хорошо подходит для диалогового стиля разработки программы. Отдельные части программы можно написать, проверить и выполнить, не выходя из интерпретатора, а когда найдена ошибка, ее можно исправить немедленно, и при этом нет необходимости возвращаться к программе редактирования текста и затем компилировать программу снова.

Программы-загрузчики –это программы, которые переносят объектную программу с внешнего носителя информации, например перфоленты или линии связи, в оперативную память микроЭВМ.

Эта функция загрузчика должна выполняться на микроЭВМ, для которой разработано программное обеспечение. На загрузчик могут быть также возложены функции преобразования перемещаемого варианта объектной программы в программу в абсолютных адресах и установления связей между объектными программами с помощью взаимных ссылок. Последний процесс называется редактированием внешних связей. В обоих случаях загрузчик изменяет объектную программу на основе управляющей информации, получаемой загрузчиком как от языкового транслятора, так и непосредственно от программиста. Части программы-загрузчика, реализующие функции перемещаемости и редактирования внешних связей, могут быть межмашинными или резидентными программами. Загрузчики резидентного типа обычно поставляются на перфолентах или в виде программируемого ПЗУ.

Моделирующие программы -это межмашинные программы, позволяющие пользователю отлаживать объектную программу без микроЭВМ. Кроме того, моделирующие программы часто предоставляют некоторые виды диагностической информации, недоступной при использовании отладочной программы на микроЭВМ, такие, как указание о переполнении стека или указание о попытке программы записать информацию в ПЗУ. Моделирующая программа под управлением пользователя моделирует выполнение объектной программы на микроЭВМ. Моделирующие программы позволяют: оперировать и выводить на дисплей содержимое памяти моделируемой микроЭВМ и регистров микропроцессора; устанавливать контрольные точки в программе, в которых программа может быть приостановлена при достижении некоторого адреса в программе или при чтении или записи в некоторую ячейку памяти; задавать листинг с печатью каждой команды, принадлежащей области адресов, указанной при задании режима листинга по мере ее выполнения. Моделирующие программы часто предоставляют информацию о времени выполнения программы, например число команд и (или) машинных тактов, выполненных от начала работы программы до ее останова. Моделирующие программы различных производителей отличаются по своим возможностям, однако независимо от того, насколько хороша моделирующая программа, она никогда не может заменить полностью отладку программы на микроЭВМ. Это объясняется тем, что специфические временные соотношения и условия внешнего окружения аппаратуры микроЭВМ невозможно смоделировать полностью.

Отладочные программы являются резидентными, облегчающими отладку объектной программы на микроЭВМ. Обычно они принимают от пользователя команды на выполнение следующих функций: вывод на дисплей (на печать) содержимого постоянной памяти или памяти с произвольным доступом микроЭВМ, а также содержимого регистров центрального процессора; изменение содержимого оперативной памяти; выполнение программы с указанного адреса; приостановка выполнения программы с указанного адреса; приостановка выполнения программы по достижении команды, находящейся в определенной ячейке памяти, или при выполнении заданного условия.

Отладочная программа может приостановить выполнение программы в любом месте, где встречается ссылка на обозначенный идентификатор или переменную; где происходит изменение значения переменной; если переменная принимает любое значение между заданными границами; если переменная или число исполнений оператора становятся равными заданному значению, Кроме этого, возможно выделение специальных регистров слежения, контролирующих состояние шины управления микропроцессора.

Отладочные программы в сочетании с моделирующими программами позволяют значительно уменьшить вероятность появления ошибок в объектных программах.

Литература:

1. М.В. Напрасник «Микропроцессоры и микроЭВМ», стр.:137-143.

ТЕМА 3.4Структура команд микроЭВМ.

ЗАНЯТИЕ 3.4.1. Требования, предъявляемые к системам команд, методам

адресации данных и управлению адресами и операциями.

ВОПРОСЫ ЗАНЯТИЕ:

1. Общие требования к системе команд и методам адресации.

2. Особенности построения и функционирования логических блоков прерывания работы микропроцессоров.

3. Методы и средства управления вводом — выводом данных.

ПЕРВЫЙ ВОПРОС

Системы команд и методы адресации данных.Автоматизация обработки информации и управления МП обеспечивается цифровым программным управлением. Программа вычислений записывается в памяти системы в виде последовательности команд. Каждая команда программы должна: определять вид операции, исполняемой в данном цикле работы; задавать адреса (адрес) двух (или одного) операндов, участвующих в операции; определять место засылки результата операции; указывать адрес расположения следующей команды.

Вследствие малой разрядности микропроцессора очень трудно столь обширную информацию указать с помощью только одного машинного слова. Поэтому проблема выбора формата команд и кодирования полей команд микропроцессора имеет особое значение.

Разрядность команды микропроцессора имеет очень большое значение, поскольку МП отличаются друг от друга именно построением и интерпретацией команд. Гибкость микро-ЭВМ и ее эффективность определяются логической мощностью команд, полнотой системы команд, средствами и способами адресации, а также возможностями организации разветвленных вычислительных процессов. Поэтому большая разрядность команды обеспечивает более широкие возможности микропроцессоров.

Рассмотрим гипотетический формат команд, обращая внимание на необходимость жесткой экономии их разрядности. Код операции должен занимать более трех разрядов, иначе «бедность» выполняемых микропроцессором операций породит проблему «длинных» программ даже для простых задач. Кроме арифметических и логических операций необходимо предусмотреть операции пересылок информации в регистрах микропроцессоров, операции ветвления в зависимости от различных условий, операции ввода — вывода. В системе команд микропроцессора желательно предусмотреть механизм работы со стандартными подпрограммами, поскольку из-за существенных аппаратурных ограничений многие сложные функции в нем выполняются программным способом.

Несмотря на то что при проектировании микропроцессоров может быть использовано большое количество вариантов выделения полей команд, ограниченная разрядность команды создает существенные трудности при размещении в команде достаточной информации о коде операции и методах адресации данных. Возможным решением проблемы является введение в систему команд операций с удвоенной разрядностью и команд с переменной разрядностью. При применении команд с удвоенной разрядностью первое слово команды содержит информацию о кодах операций, способах адресации, признаке одиночной или двойной команды и информацию о старших разрядах адреса операнда. Второе слово двухсловной команды несет информацию о младших адресах операнда. Полный адрес определяется кодом второго слова и кодом старших разрядов адреса, записываемых в первом слове команды. Естественно, что использование двухсловных команд требует двух обращений в ОЗУ за командой и специальных средств микропроцессоров для правильной интерпретации обоих слов команды (эти средства применяются и для анализа типа команды, усложняясь по мере увеличения количества слов в команде).

Чтобы определить М слов информации в памяти, необходимо иметь па = log2M разрядов для прямого указания кода адреса. При М = 65К слов па = 16. Байтовый формат поля адреса позволяет прямо адресовать лишь 28 = 256 слов (ячеек) памяти. В одной команде желательно иметь двухадресный формат, т. е. желательно одновременно задавать адреса хотя бы одного исходного операнда и результата. Вследствие малой разрядности команды микро-ЭВМ прямой двухадресный формат можно задать лишь при обращении к внутреннему регистровому файлу небольшой информационной емкости.

Кроме поля кода операции и кода адреса (адресов) команда должна содержать поле признаков, указывающее на особенности адресации. Методы адресации определяют механизм формирования исполнительного (прямого) адреса в памяти, исходя из значений адресного поля и поля признаков адресации команды. Используется большое количество методов адресации в микропроцессорах, позволяющих расширить адресуемое пространство информации и связать между собой различные части вычислительных процессов. Гибкость системы команд в большей степени определяется разнообразием методов адресации.

Адрес следующей команды в микропроцессоре задается с помощью счетчика команд. При обычном ходе выполнения программы переход к очередной команде требует операции прибавления единицы в счетчик команд. При операциях условного или безусловного перехода в счетчик команд засылается новое значение кода адреса команды, определяющего новую ветвь вычислительного процесса. Движение по ней идет также в соответствии с операцией прибавления единицы в счетчик команд. Введение специального индексного регистра существенно расширяет возможности микропроцессора за счет индексной адресации.

Управление адресами.Команды микропроцессора записывают в виде системы цифровых кодов, поэтому над ними могут выполняться различные арифметические и логические операции, как над обычными двоичными числами.

В результате автоматического преобразования команд происходит их модификация в соответствии с заданными признаками адресации. Чтобы не загружать операционный блок операциями модификации адресов, в состав микропроцессора вводится индексный блок (блок индексной арифметики, или инкремента — декремента).

Управление операциями.Коды операции команд программы, воспринимаемые управляющей частью микропроцессора, расшифрованные и преобразованные в ней, дают информацию о том, какие операции надо выполнить, где в памяти расположены данные, куда надо направить результат и где расположена следующая за выполняемой команда.

Управляющее устройство имеет достаточно средств для того, чтобы после восприятия и интерпретации информации, получаемой в команде, обеспечить переключение (срабатывание) всех требуемых функциональных частей машины, а также для того, чтобы подвести к ним данные и воспринять полученные результаты.

Именно срабатывание, т. е. изменение состояния двоичных логических элементов на противоположное, позволяет посредством коммутации вентилей выполнять элементарные логические и арифметические действия, а также передавать требуемые операнды в функциональные части микро-ЭВМ.

Устройство управления в строгой последовательности в рамках тактовых и цикловых временных интервалов работы микропроцессора (такт — минимальный рабочий интервал, в течение которого совершается одно элементарное действие; цикл — интервал времени, в течение которого выполняется одна машинная операция) осуществляет: выборку команды; интерпретацию ее с целью анализа формата, служебных признаков и вычисления адреса операнда (операндов); установление номенклатуры и временной последовательности всех функциональных управляющих сигналов; генерацию управляющих импульсов и передачу их на управляющие шины функциональных частей микро-ЭВМ и вентили между ними; анализ результата операции и изменение своего состояния так, чтобы определить месторасположение (адрес) следующей команды.

Особенности программного и микропрограммного управления операциями.Вмикропроцессорах используют два метода выработки совокупности функциональных управляющих сигналов: программный и микропрограммный.

Выполнение операций в машине сводится к элементарным преобразованиям информации (передача информации между узлами в блоках, сдвиг информации в узлах, логические поразрядные операции, проверка условий и т.д.) в логических элементах, узлах и блоках под воздействием функциональных управляющих сигналов блоков (устройств) управления. Элементарные преобразования, не разложимые на более простые, выполняются в течение одного такта сигналов синхронизации и называются микрооперациями.

В аппаратурных (схемных) устройствах управления каждой операции соответствует свой набор логических схем, вырабатывающих определенные функциональные сигналы для выполнения микроопераций в определенные моменты времени. При этом способе построения устройства управления реализация микроопераций достигается за счет однажды соединенных между собой логических схем, поэтому ЭВМ с аппаратурным устройством управления называют ЭВМ с жесткой логикой управления. Это понятие относится к фиксации системы команд в структуре связей ЭВМ и означает практическую невозможность каких-либо изменений в системе команд ЭВМ после ее изготовления.

При микропрограммной реализации устройства управления в состав последнего вводится ЗУ, каждый разряд выходного кода которого определяет появление определенного функционального сигнала управления. Поэтому каждой микрооперации ставится в соответствие свой информационный код — микрокоманда. Набор микрокоманд и последовательность их реализации обеспечивают выполнение любой сложной операции. Набор микроопераций называют микропрограммами. Способ управления операциями путем последовательного считывания и интерпретации микрокоманд из ЗУ (наиболее часто в виде микропрограммного ЗУ используют быстродействующие программируемые логические матрицы), а также использования кодов микрокоманд для генерации функциональных управляющих сигналов называют микропрограммным, а микро-ЭВМ с таким способом управления — микропрограммными или с хранимой (гибкой) логикой управления.

К микропрограммам предъявляют требования функциональной полноты и минимальности. Первое требование необходимо для обеспечения возможности разработки микропрограмм любых машинных операций, а второе —

связано с желанием уменьшить объем используемого оборудования. Учет фактора быстродействия ведет к расширению микропрограмм, поскольку усложнение последних позволяет сократить время выполнения команд программы.

Преобразование информации выполняется в универсальном арифметическо-логическом блоке микропроцессора. Он обычно строится на основе комбинационных логических схем.

Для ускорения выполнения определенных операций вводятся дополнительно специальные операционные узлы (например, циклические сдвигатели). Кроме того, в состав МПК БИС вводятся специализированные оперативные блоки арифметических расширителей.

Операционные возможности микропроцессора можно расширить за счет увеличения числа регистров. Если в регистровом буфере закрепление функций регистров отсутствует, то их можно использовать как для хранения данных, так и для хранения адресов. Подобные регистры микропроцессора называются регистрами общего назначения. По мере развития технологии реально осуществлено изготовление в микропроцессоре 16, 32 регистров и более.

ВТОРОЙ ВОПРОС

Процесс прерывания работы микропроцессоров сигналами запроса внешних устройств устраняет необходимость выполнения микропроцессором неэффективных операций по проверке готовности внешних устройств к обмену и снижает затраты времени на ожидание их готовности. Реализация механизма прерываний имеет наибольшую важность в случае необходимости обмена данными с большим числом асинхронно работающих внешних устройств. Использование обмена по методу программируемого безусловного перехода, который может быть успешно реализован в синхронной системе, где моменты готовности к работе внешних устройств определяются достаточно точно, здесь неэффективно.

Для определения требований к построению системных блоков прерывания работы микропроцессоров рассмотрим особенности построения и функционирования внутренних схем прерывания микропроцессоров, реализуемых на кристалле БИС.

Практически все микропроцессоры имеют отдельные выводы на корпусе для ввода и вывода сигналов, определяющих запросы и удовлетворение запросов на прерывания. Сложность связанных с ними электронных схем определяет возможности системы прерываний.

Момент возникновения запроса прерывания микропроцессора не связан с его работой по основной программе или какой-либо подпрограмме. Сигналы запроса прерывания текущей программы асинхронны относительно циклов работы микропроцессора. Поэтому, получив сигнал запроса на прерывание работы, микропроцессор должен закончить выполнение текущей микрооперации или операции и только после этого приступить к удовлетворению запроса. Такой порядок дает возможность получить промежуточные результаты, являющиеся итогом работы микропроцессора по программе (подпрограмме), зафиксировать их в его регистрах и заслать на хранение в память. Процесс сбора и пересылки содержимого внутренних регистров микропроцессора в память часто называется контекстным переключением, так как содержимое регистров имеет определенный смысл только в контексте данной выполняемой программы. Процесс считывания из памяти и распределения данных по определенным регистрам микропроцессора позволяет восстановить контекст, т. е. состояние прерванной программы, после окончания удовлетворения запроса прерывания. Именно такой порядок осуществления процесса прерывания дает возможность перехода от программы к подпрограмме и обратно к последовательности вложенных подпрограмм без потери промежуточной информации и правильного счета по запрограммированным алгоритмам. Однако, контекстное переключение должно гарантировать правильность продолжения работы микропроцессора после прерывания программы (подпрограммы), т. е. не должно вносить никаких последствий в процесс работы микропроцессора, кроме временных перерывов.

Чтобы охарактеризовать важное качество микропроцессора и электронных систем на его основе по возможности прерывания прерывающих программ, вводят понятие «уровень программного прерывания микропроцессора». Если нельзя прервать прерывающую программу, то считается, что электронная система спроектирована с нулевым уровнем прерывания. Чтобы избежать подобных ограничений, большинство МП имеет средства для обеспечения практически произвольного количества уровней прерывания. Это означает, что имеется возможность многократного прерывания прерываний и образования прерываний внутри прерываний, т. е. вложенных прерываний, ведущих к появлению последовательностей вложенных подпрограмм.

Стек — эффективное программно-аппаратурное средство для сохранения и возврата данных при контекстном переключении и осуществления вложенных прерываний. Стек (магазинная память) представляет собой совокупность ячеек памяти, организованных так, что обращение к некоторой последовательности (списку) слов может происходить в процессе, обратном записи. Это означает, что стек позволяет осуществить принцип работы «последнее из списка последовательно записанных слов считывается первым». В стеке реализуется подразумеваемая адресация, т. е. всегда запись или чтение данных происходит в «верхней» ячейке. Образно стек можно представить в виде бесконечной этажерки, где ячейки соответствуют полкам. «Положить» слово можно только выше последнего положенного (записанного) слова; «взять» можно только то слово, которое «положено» самым последним. Чтобы осуществить именно этот порядок обращения, имеется регистр «Указатель полки», который перемещается по мере добавления новых слов на полках вверх или опускается вниз по мере их взятия. Этот регистр — указатель состояния заполненности стека — физически указывает на регистр СОЗУ на кристалле микропроцессора или на ячейку памяти ОЗУ.

Практически неограниченный по информационной емкости стек получается именно во втором случае, поскольку редко возникает необходимость иметь в системе тысячу (и более) уровней прерывания, а такая глубина прерываний вполне реализуется при использовании ОЗУ с доступной величиной информационной емкости.

При удовлетворении запроса на прерывание текущей программы блок управления (БУ) микропроцессора осуществляет запись контекстного состояния рабочих регистров микропроцессора, в стек автоматически начиная с «верхней» ячейки и добавляет единицу в регистр-указатель ячейки стека после каждой записи. Поэтому достаточно одной команды «Записать состояние в стек», чтобы аппаратурные средства МП считали всю контекстную информацию рабочих регистров и направили ее для хранения в стек. Восстановление контекста также происходит автоматически по команде «Восстановить состояние прерванной программы (подпрограммы)», которая ставится последней в подпрограмме прерывания. В процессе восстановления в счетчик команд заносится адрес возврата из прерываний, указывающих на команду, которая должна выполняться первой.

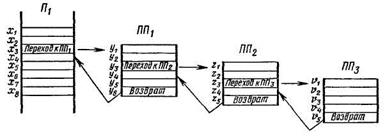

На рис. 1 приведена диаграмма заполнения и освобождения стека при появлении цепочки вложенных прерываний. Анализ последовательности работы МП показывает, что имеют при выполнении вычислений и решении задач управления место организованный переход от подпрограммы к подпрограмме, запоминание промежуточных состояний и последовательное завершение всех подпрограмм.

Рис. 1. Порядок выполнения вложенных подпрограмм при использовании стека.

Таким образом, магазинный механизм запоминания адресов возвратов дает очень удобные средства работы с подпрограммами. При переходе к подпрограмме стек заполняется сверху и его содержимое продвигается вниз. При возврате в прерванную программу содержимое стека продвигается каждый раз вверх, выталкивая в счетчик команд адрес команды возврата. Поэтому для работы со стеком достаточно двух команд: «Записать в стек» («Втолкнуть в стек») и «Считать из стека» («Вытолкнуть из стека»).

В состав микропроцессора можно ввести средства для записи и возвращения не только содержимого счетчика команд, но и всех других регистров, состояние которых необходимо сохранять при прерываниях. При этом в «верх» стека последовательно записывается содержимое счетчика команд, аккумулятора, регистра признаков и т.д. При выполнении одной команды «Возврат» автоматически производится несколько считываний из стека и «разворачивание» извлекаемой информации в определенные регистры.

Виды запросов на прерывания.Вбольшинстве микропроцессоров приняты запросы прерывания немаскируемые и маскируемые.

Немаскируемые запросы на прерывание — такие прерывания, которые аппаратурно реализованы вне программного контроля и не управляются программистом. Сигналы немаскируемых запросов на прерывания обычно поступают в микропроцессор по отдельной шине магистрали управления и имеют наивысший приоритет, т. е. исполняются ранее других запросов на прерывания.

Обычно к немаскируемым запросам на прерывания относятся запросы на прерывания от таких важнейших для системы средств, как схемы питания и контроля правильности передач данных. Например, снижение уровня питания создает опасность потери всей оперативной информации, поскольку полупроводниковые ОЗУ и регистры микропроцессора теряют информацию при отключении или сбоях питания. Поэтому схемы контроля питания в этом случае подают запрос прерывания и совершается переход к подпрограмме аварийной перезаписи оперативной информации в ОЗУ с батарейным невыключаемым питанием или во внешнее магнитное ЗУ. Следовательно, в блоке питания должны быть предусмотрены емкостные фильтры для того, чтобы длительность снижения уровня вторичного напряжения при выключении первичного питания была достаточна для выполнения аварийной подпрограммы. Цепи контроля правильности передач данных должны действовать аналогично Любые ошибки в последовательностной системе запоминаются и искажают все последующие результаты. Поэтому необходимо прекратить вычисления и решением тестовых задач как подпрограмм прерывания выяснить неисправные аппаратурные блоки, провести восстановление работоспособности системы и лишь после этого продолжать выполнение основной программы.

Маскируемые запросы на прерывания управляются командами программы и имеют целью дать программисту возможность гибкого управления вычислительным процессом. Если программист организовал программный цикл ожидания и обмен с устройством, который не может быть прерван, то ему необходимо отключить механизм прерываний. Для этих целей в состав регистра состояния микропроцессора вводится специальный триггер «Разрешение удовлетворения запросов на прерывания». Сигнал с этого триггера поступает в блок управления микропроцессора как сигнал запрета (маскирования) запросов прерывания Триггер «Разрешение удовлетворения запросов на прерывания» устанавливается в состояние «1» и сбрасывается в состояние «О» специальными командами «Установить маску прерываний», «Сбросить маску прерываний». Поэтому программист может вставлять их в программу везде, где это необходимо.

При использований маскируемых запросов на прерывания между внешним устройством и микропроцессором должен осуществляться асинхронный обмен управляющими сигналами до начала собственно процесса прерывания. Поэтому в ряде микропроцессоров прием запроса и начало процесса прерывания сопровождаются выходным сигналом «Запрос прерывания удовлетворен». Этот сигнал может быть использован и для маскирования схемы прерываний. Необходимость в этом связана с тем, что если до конца выполнения подпрограммы прерывания сигнал «Запрос прерывания» не снят, то тот же самый запрос будет выполняться вновь. Поэтому в качестве последней команды подпрограммы прерывания должна стоять команда снятия маски прерывания. Это является гарантией того, что если будет сгенерирован запрос прерывания, то он будет новым.

Определение адреса программы прерывания по сигналам запроса на прерывание от конкретного внешнего устройства.Для задания адреса программы прерывания применяются методы, различающиеся числом дополнительных схем в микропроцессоре или в информационном контроллере внешнего устройства.

Наиболее простой метод заключается в записи кода адреса памяти, где записана первая команда подпрограммы прерывания, в специальном регистре адреса прерывания. В этом случае блок управления микропроцессором после завершения контекстного переключения автоматически считывает и передает в регистр счетчика команд код регистра адреса прерывания. Обратившись по этому адресу, микропроцессор считывает два байтовых числа или одно двухбайтовое число, которое является первой командой подпрограммы прерывания. Поскольку данный метод прямо указывает на место расположения подпрограммы прерывания, для обозначения начального адреса программы прерывания используют термин «вектор прерывания». Таким образом, рассмотренный метод позволяет косвенной адресацией ячейки памяти определить вектор прерывания, а через него и подпрограмму прерывания.

Другой метод требует проведения асинхронного запроса со стороны микропроцессора к внешним устройствам для определения устройства, которое выставило сигнал запроса на прерывание. Информационный контроллер внешнего устройства, пославшего сигнал запроса на прерывание, в ответ на запрос микропроцессора выставляет код команды, который при исполнении блоков управления микропроцессора вызывает ветвление по одному из некоторого множества адресов. Следовательно, этот метод также практически прямо указывает на вектор прерывания, причем позволяет задать векторы прерываний многих подключенных внешних устройств. Для реализации он требует развития средств информационного контроллера. В сложных микропроцессорах используется специальный регистр, адресуемый программистом и называемый регистром вектора прерывания, с помощью которого можно также прямо задать векторы прерывания многих внешних устройств.

Определение адресов программ прерывания по сигналам запроса на прерывания от некоторого множества внешних устройств.Микропроцессор может иметь только два ввода для приема сигналов запросов на маскируемые и немаскируемые прерывания, а в электронной системе может быть необходимо осуществить управление многими внешними устройствами. В этом случае возможно одновременное появление множественных запросов на прерывание работы микропроцессора, т. е. сигналов запросов на прерывание от ряда внешних устройств.

При этом имеется несколько путей решения проблемы управления множественными сигналами запроса на прерывания. Все выходы схем генерации запросов прерывания выполняются на основе каскадов с открытым коллектором или с тремя внутренними состояниями и параллельно соединяются с выводом МП. Срабатывание такого каскада вызывает сигнал запроса прерывания. Микропроцессор, опознав его, проводит анализ и определяет точный адрес

вектора прерывания. Наиболее распространены системы векторных и обзорных прерываний.

Векторные прерывания требуют значительных аппаратурных затрат, но имеют высокую скорость реакции. Один из методов реализации векторных прерываний посылкой кода команды из средств информационного контроллера был рассмотрен выше.

Обзорные прерывания заключаются в выполнении общей подпрограммы прерывания с целью определения вектора прерывания конкретного устройства. Подпрограмма содержит главным образом команды считывания и анализа кода состояния внешних устройств. Последовательный анализ по заранее заданной схеме позволяет выделить устройство, подготовленное к обмену. После этого совершается условный переход и считывается вектор прерывания этого устройства. Данный метод требует для реализации небольших аппаратурных затрат и может быть применен при подключении небольшого числа медленных устройств, поскольку требует значительных затрат времени на осуществление процесса прерывания.

В любой из рассмотренных систем прерываний возникают сложности управления одновременными запросами на прерывания от нескольких устройств. Обычно они разрешаются назначением приоритета каждому внешнему устройству. Поэтому при появлении одновременно нескольких запросов предпочтение отдается запросу на прерывание от более приоритетного устройства.

В системе, реализующей схему управления векторными запросами на прерывания, цепочечное подключение узлов запросов на прерывания приоритетных устройств автоматически выявляет активное устройство: сигнал удовлетворения запроса прерывания проходит через узлы всех более высокоприоритетных схем и вызывает передачу вектора прерывания наиболее приоритетного устройства.

В системе с реализацией принципа обзорных прерываний приоритет устройства прямо устанавливается анализом кода состояния и не требует дополнительной аппаратуры.

Сравнение векторных и обзорных систем прерывания работы микропроцессора показывает, что при их проектировании можно достичь компромисса между количеством аппаратуры микропроцессора и объемом его программного обеспечения. Меньшие аппаратурные затраты требуют большего программного обеспечения и порождают низкоскоростные решения. Более высокое быстродействие достигается более высокими аппаратурными затратами и меньшими программными издержками. Сложность аппаратурных решений не позволяет заложить многого в кристалл микропроцессора. Поэтому в комплекте БИС развитого микропроцессора выпускается специальная БИС программируемого контроллера прерывания.

ТРЕТИЙ ВОПРОС

При проектировании микропроцессорной системы важнейшее значение имеет правильный выбор методов управления вводом — выводом данных.

Микропроцессор обладает очень широкими возможностями организации ввода — вывода, однако на эффективность ввода — вывода существенное влияние оказывают особенности тех технических средств, которые являются источниками (приемниками) вводимых — выводимых данных. Микропроцессор может взаимодействовать с различными типами источников (приемников) данных. В одних из них смена данных происходит в любой момент времени и занимает достаточно большой интервал (по сравнению с быстродействием микропроцессора). Установленные данные могут быть считаны (записаны) через достаточно произвольный интервал времени после установки. К подобным средствам ввода — вывода можно отнести практически все устройства ввода — вывода данных, предназначенные для взаимодействия оператора и системы (например, дисплеи, клавиатура).

Имеются устройства, работающие значительно медленнее, чем микропроцессор, но в периодическом режиме (например, накопители данных на магнитных дисках, печатающие устройства). В этих устройствах данные могут быть записаны (считаны) только в определенные промежутки времени. Если именно в этот промежуток времени микропроцессор не осуществит сеанс взаимодействия, то данные будут потеряны. В то же время, если микропроцессор будет только следить за состоянием таких устройств, он не сможет выполнять других функций в системе. Поэтому во время пассивных промежутков времени между сеансами взаимодействия микропроцессор должен выполнять другие операции в системе. Для этого в системе должна быть решена задача разделения пассивных и активных интервалов взаимодействия. Например, во внешние устройства можно ввести дополнительные технические средства индикации активного состояния, а в МП — средства соответствующей реакции на сигналы возникновения активного состояния в системе.

В системе могут быть данные, снимаемые с датчиков состояния управляемых объектов (процессов), крутизна и предельные значения которых должны быть предметом особого контроля со стороны микропроцессора.

В реальной системе могут быть объединены многочисленные сигналы разнообразных вводимых и выводимых данных. Один из рациональных методов осуществления ввода — вывода в такой системе заключается в организации асинхронного режима работы микропроцессора и приемников — источников информации. В этом случае до обмена данными всегда происходит обмен асинхронными управляющими сигналами. Действительно, обмен по прерываниям работы микропроцессора может начаться только тогда, когда внешнее устройство выработает сигнал готовности («Запрос на прерывание»), а МП, завершив обязательные действия над выполняемой командой программы, выработает ответный сигнал «Запрос на прерывание удовлетворен». Затем микропроцессор осуществляет переход к подпрограмме обслуживания запроса прерывания, которая содержит последовательность команд обмена данными. По завершении подпрограммы прерывания микропроцессор возвращается к продолжению работы по ранее прерванной программе.

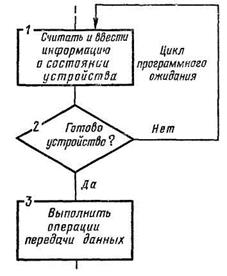

Программный обмен данными по командам условного перехода. Вэтом виде обмена микропроцессор программным путем должен определить, готово ли периферийное устройство к выполнению операций ввода — вывода до того, как начнется программная передача данных. Внешнее устройство должно иметь аппаратурные средства для выработки информации о внутреннем состоянии статусной информации. Микропроцессор считывает эту информацию, передает ее во внутренний регистр-аккумулятор, анализирует и на основе результата анализа принимает решение о готовности устройства.

На рис. 3.3 приведена схема алгоритма программного обмена данными по командам условного перехода. Из нее следует, что микропроцессор может находиться в режиме программного ожидания (готовности) внешнего устройства, выполняя команды блоков 1 и 2. После обнаружения состояния готовности МП передает данные по командам блока 3, а затем приступает к работе по продолжению основной программы.

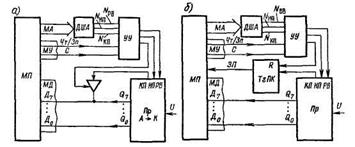

Обмен данными по командам условного перехода. Аналого-цифровой преобразователь при передаче данных имеет трехуровневые выходные каскады, передача данных с которых осуществляется по сигналу «Разрешение выдачи» РВ. По сигналу «Начало преобразования» преобразователь начинает преобразование мгновенной амплитуды входного аналогового сигнала в 8-разрядный код. Время преобразования зависит от реализуемого принципа преобразования и схемотехнического исполнения. Во время преобразования выдается управляющий сигнал «Конец преобразования» КП, равный «0». Он принимает значение «1», когда преобразование аналоговой величины в код завершено. Чтобы считать требуемое значение данных, сигнал РВ должен поступить после того, как установится значение «1» сигнала КП.

Рис. 2. Схема алгоритма программного обмена данными.

На рис. 3, а, приведена схема подключения преобразователя к микропроцессору МП. Для микропроцессора преобразователь Пр представляется как логическое устройство, управляемое сигналами «Начало преобразования» НП, «Конец преобразования» КП и «Разрешение выдачи» РВ. Эти сигналы считываются микропроцессором из байтового выходного регистра данных. Сигналы данных Q7—Q0 имеют правильное значение, если соблюдена последовательность выдачи управляющих сигналов НП, КП, РВ согласно временной диаграмме. Чтобы выдавать требуемые управляющие сигналы в заданное время, каждый управляющий сигнал определяется своим адресом N. Сигнал с дешифратора адреса ДША вместе с сигналом операции микропроцессора «Чтение — запись» Чт/Зп по сигналу импульса синхронизации С определяет генерацию необходимого управляющего сигнала. По сигналам Мнп= 1 и УУрв = 1 осуществляется запуск преобразователя; по сигналам NPB и Nкп = 1 — считывание и ввод в микропроцессор значения сигнала КП. Этот сигнал через трехуровневый каскад вводится в микропроцессор МП по шине Д7. В 8-разрядном МП этот разряд является разрядом знака числа. Поэтому команда «Условный переход по знаку результата» определит либо окончание преобразования (КП =1), либо необходимость перехода к новому циклу анализа (КП = 0). После определения состояния КП = 1 командой «Прочитать данные по адресу МРв» осуществляется ввод информации с преобразователя в МП.

Рис 3. Схема подключения преобразователя к микропроцессору при программном вводе данных (а) и при вводе данных по прерываниям (б).

Из рассмотренного примера и принципа обмена данными по командам условного перехода видно, что микропроцессор должен находиться в режиме ожидания, следя за состоянием внешнего устройства. На чтение статусной информации и ее анализ может быть затрачено большое количество циклов работы микропроцессора, которые, по существу, будут потерянными. Если микропроцессор работает только с одним устройством, то такие потери неизбежны. Однако в электронной системе со множеством источников-приемников данных рассмотренный режим ввода — вывода неэффективен.

Обмен данными по сигналам прерывания работы микропроцессора от внешних устройств.При обмене данными по сигналам прерывания внешние устройства являются сами инициаторами обмена. Микропроцессор работает параллельно с ними над выполнением основной программы и не занимается анализом состояния внешних устройств. Но в микропроцессоре должны быть специальные аппаратурные средства анализа состояния внешних устройств. Когда эти устройства обнаруживают готовность к обмену какого-либо внешнего устройства, то сигнализируют об этом блоку управления микропроцессора. Последний завершает текущую операцию, передает на хранение в память всю информацию внутренних регистров данных и управления и осуществляет переход к подпрограмме обслуживания прерывания. Основная часть этой подпрограммы — команды передачи данных между микропроцессором и конкретным внешним устройством. В конце ее имеются программы восстановления состояния микропроцессора, которое существовало к началу прерывания.

Рис. 4. Схема подключения канала прямого доступа к ОЗУ в микропроцессорной системе.

Ввод данных по прерываниям.Рассмотрим ввод данных с аналого-цифрового преобразователя. В данном случае выходной сигнал «конец преобразования» КП не связан с магистралью данных МД (рис. 4), поскольку нет необходимости анализировать состояние устройства. Этот сигнал используется для установки специального триггера прерывания JK-типа по входу С. Триггер прерывания ТгП применяется для генерации сигнала запроса прерывания микропроцессора МП.

Сигнал «Запрос прерывания» ЗП поступает в блок управления и используется для прерывания работы МП. Так как сигнал ЗП = 1 будет все время вызывать срабатывание схем блока управления процессора, то сразу же после удовлетворения запроса прерывания командой «Считать состояние по адресу Nкп» триггер ТгП переводится в состояние «О» подачей сигнала фиктивного считывания по входу R триггера ТгП. В остальном генерация сигналов и работа схем, показанных на рис. 3 и 4, аналогична.

Обмен данными в канале прямого доступа в память.Ранее рассмотренные методы обмена данными относились к передачам между внешними устройствами и микропроцессором. Если необходимо осуществить обмен между внешним устройством и памятью, то нет необходимости пересылать данные через микропроцессор. Обычно между памятью и внешними устройствами обмен данными заключается в пересылке массивов информации. Если проводить чтение данных в памяти (внешних устройствах), заносить данные в аккумулятор микропроцессора, а затем осуществлять запись в регистры внешних устройств (или память), то затраты времени микропроцессора будут очень большими. Можно в систему ввести контроллер прямого доступа в память, который берет на себя управление передачей, освободив от этих функций системный микропроцессор.

Прямой доступ в память при выполнении операций ввода — вывода позволяет значительно увеличить скорость передачи данных и повысить эффективность использования средств микропроцессора. Построение канала прямого доступа в память является альтернативой программному обмену, поэтому и в данном случае справедливы общие закономерности балансировки программно-аппаратурных средств; выполнение определенных функций аппаратурой упрощает программное обеспечение, значительно сокращает затраты времени на выполнение функций по сравнению с их программной реализацией, но требует использования сложных дополнительных модулей аппаратуры. Последнее увеличивает стоимость, габариты и мощность потребления системы, снижает ее надежность.

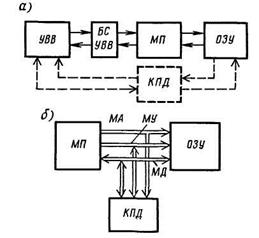

Средства канала прямого доступа КПД в память могут быть подключены «параллельно» процессору так, как это показано на рис. 5, а, с передачей функций арбитража ОЗУ. Однако при этом усложняются схемы управления ОЗУ, появляется второй информационный канал, состоящий из информационных магистралей данных МД, адреса МА и управляющих сигналов МУ (рис. 5,б). Поэтому в микропроцессорных системах решается задача разделения единого информационного канала между микропроцессором и каналом прямого доступа в память посредством использования свойств трехуровневого состояния информационных подмагистралей. Микропроцессор МП во время передачи информации по каналу прямого доступа переводит выходные схемы управления магистралями данных, адресов и управляющих сигналов в высокоомное состояние и тем самым изолируется от остальной части системы, что аналогично обрыву его информационного канала.

Степень влияния операций ввода — вывода в канале прямого доступа на основной вычислительный процесс в системе определяется сложностью аппаратурных средств контроллера этого канала. В простейшем случае контроллер берет на себя управление передачей данных по информационной магистрали в условиях, когда микропроцессор одновременно с выдачей сигнала удовлетворения запроса канала переводится в режим ожидания окончания операций в канале. При этом за счет перевода выходных каскадов управления шинами информационной магистрали в высокоомное состояние микропроцессор эффективно электрически и информационно отключается от системы. Состояние внутренних регистров «замораживается», т. е. микропроцессор в режиме ожидания сохраняет то информационное состояние, которое возникло в нем к моменту удовлетворения запроса канала прямого доступа.

Построение контроллера канала прямого доступа, функционирующего параллельно с микропроцессором, позволяет не отключать последний на время выполнения операций ввода — вывода. Однако операции ввода — вывода с использованием передач по информационной магистрали надо синхронизовать с другими операциями в системе и выполнять их тогда, когда магистраль свободна.

Микропроцессор после обращения к памяти за очередной командой занимается ее расшифровкой и анализом и в этот промежуток времени адреса обращения к памяти еще не известны. Поэтому канал прямого доступа может «занять» цикл обращения к памяти и осуществить операцию ввода или вывода слова данных. Этот метод занятия цикла памяти контроллер канала прямого доступа осуществляет так, что микропроцессор даже «не знает», что одновременно с его функционированием происходят другие операции в системе, поскольку они никакого торможения работы микропроцессора не вызывают.Недостаток канала прямого доступа с занятием цикла — ограничение его производительности быстродействием микропроцессора: обмен данными между памятью и внешними устройствами совершается со скоростью, определяемой частотой выборки команд.

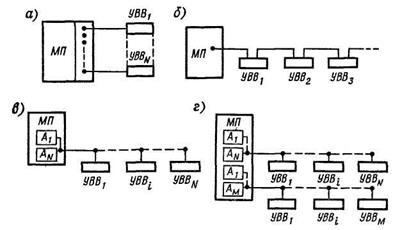

Подключение устройств ввода — вывода к микропроцессору.Способы подключения внешних устройств к микропроцессору определяются возможностями его корпуса, аппаратурно-программных средств, количеством и особенностями устройств ввода — вывода.

Рис. 5. Схемы подключения УВВ к микропроцессору.

Запрос на простое прерывание привлекает внимание микропроцессора к внешней подсистеме и требует анализа ее состояния. Если несколько устройств ввода — вывода УВВ подключены к своим индивидуальным аппаратурным ресурсам (рис. 5, а, радиальный интерфейс), то внутри МП необходимо иметь мультиплексор для последовательного опроса всех УВВ. Когда время реакции критично, можно ввести аппаратурные средства, позволяющие конкретному УВВ, сразу же после выполнения текущей команды программы вызвать свою подпрограмму обслуживания. В случае подключения многих УВВ к одному уровню прерывания при простом прерывании требуется обзор всех причин прерывания и выделения активного УВВ.

Последовательное расположение подпрограмм анализа причин прерываний УВВ в программе может считаться приоритетом, если не задан другой алгоритм. Следовательно, первое активное устройство, обнаруженное программой прерывания, получает ресурс на обслуживание. Аппаратурно этот алгоритм реализуется в «цепочечной» схеме подключения УВВ (рис. 5, б).

Векторное (направленное) прерывание возникает тогда, когда УВВ, выставившее запрос на прерывание, посылает после удовлетворения запроса адрес А1—АN ячейки, где расположена программа прерывания данного УВВ, (рис. 5, в).

Многоуровневые групповые системы прерывания требуют наличия в МП нескольких входов (рис. 5, г) и могут быть векторными приоритетными или обзорными.

Литература:

1. Л.Н. Преснухин «Микропроцессоры» ч. 1, стр.: 62-84.

ЗАНЯТИЕ 3.4.2.Система команд, форматы данных.

ВОПРОСЫ ЗАНЯТИЯ:

1. Основные форматы команд ЕС ЭВМ.

2. Пояснения к некоторым командам.

3. Форматы и система команд микроЭВМ «Электроника-60».

ПЕРВЫЙ ВОПРОС

Для примера рассмотрим систему кодирования команд с переменной адресностью ЕС ЭВМ. В этих машинах имеется 16 универсальных регистров общего назначения и 4 регистра, предусмотренных для операндов с плавающей точкой. Универсальные регистры содержат 32 разряда. В них можно хранить операнды и результаты промежуточных вычислений, индексы (константы модификаций) и базовые адреса. В этом отношении универсальные регистры играют роль сверхоперативной памяти. В ЕС ЭВМ оперативная память разделена на несколько операционных блоков и программу, а данные можно размещать в некоторой отведенной для этой цели области, начальный адрес которой называется базовым.

Рис. 1. Форматы команд машин ЕС ЭВМ.

Таким образом, адрес операнда имеет сложную структуру и состоит из базы и смещения.

Базовый адрес хранится в одном из универсальных регистров, а исполнительный адрес формируется путем сложения текущего и базового адресов.

Регистры с плавающей точкой имеют 64 разряда и используются только для хранения операндов.

В ЕС ЭВМ существует пять основных форматов команд, обозначаемых своим кодом, который указывает на характер выполняемой команды:

1. Команды формата «регистр – регистр» (рис. 1, а) обозначаются форматным кодом RR и имеют длину одного полуслова (16 бит). Они выполняют операции над содержимым регистров, адреса которых А1 и А2. Результат операции помещается на место первого операнда.

2. Команды формата «регистр – индексируемая ячейка памяти» (рис. 1, б) обозначаются RX и имеют длину одного слова. Адрес А1указывает регистр, где хранится первый операнд. В адресе А2 старшие четыре разряда Х2 указывают универсальный регистр,

Дата добавления: 2015-12-08; просмотров: 2459;