РАЗДЕЛ 3 Программное обеспечение микропроцессорных систем 1 страница

ТЕМА 3.1 Типовая структура микроЭВМ.

ЗАНЯТИЕ 3.1.1 Два способа организации микроЭВМ: с разными шинами данных и адреса и с мультиплексированной шиной данных и адреса.

ВОПРОСЫ ЗАНЯТИЯ:

1. Общие сведения о микроЭВМ. Функциональные блоки и организация управления в микроЭВМ.

2. Способ организации микроЭВМ с раздельными шинами адреса и данных.

3. Способ организации микроЭВМ с мультиплексированной шиной данных и адреса.

ПЕРВЫЙ ВОПРОС

Организация микроЭВМ на базе типовых микропроцессорных комплектов определяется принципами формирования МПК, организацией системы памяти, системы ввода-вывода, системы прерываний, архитектурными особенностями микропроцессора и некоторыми характеристиками БИС МПК. Однако основное влияние на организацию микроЭВМ оказывают способы реализации передачи данных и адресов между микропроцессором и другими компонентами микроЭВМ. С этой точки зрения различают два способа организации микроЭВМ: с раздельными шинами данных и адреса; с мультиплексированной шиной данных и адреса.

Микропроцессорные интегральные схемы (МП ИС) и микро-ЭВМ, построенные на их основе, явились следствием бурного развития микроэлектроники, позволившего в одном кристалле полупроводника размещать сложные вычислительные структуры, содержащие десятки тысяч транзисторов. Изготовление больших интегральных схем (БИС) сопряжено с трудоемкой работой по разработке схем, фотошаблонов и подготовкой производства и служб контроля технологических параметров и характеристик БИС. Снижение себестоимости БИС возможно лишь при максимальной автоматизации этапов, предшествующих их изготовлению, и массовости производства. Массовое производство БИС предполагает широкий спрос потребителя, а следовательно, возможность ее использования для большого круга решаемых задач. Микропроцессорные БИС (МП БИС) представляют тот класс интегральных схем, который сочетает в себе высокую степень интеграции, обеспечивающую огромные функциональные возможности, с большой универсальностью по применению. Достигается универсальность тем, что в МП БИС реализованы сложные устройства, позволяющие выполнять над исходными числами логические и арифметические функции, при этом управление процессом вычисления ведется программно. Изменение программы вычисления позволяет осуществить вычисление любой сложной функции.

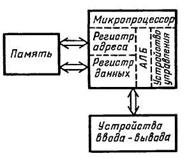

Если рассмотреть схему микро-ЭВМ (рис. 1), то можно прийти к выводу, что в ней содержатся те же блоки, на которых строились вычислительные машины предыдущих поколений.

Рис. 1. Схема микро-ЭВМ.

Однако микро-ЭВМ имеет некоторое архитектурное отличие от предшествующих ЦВМ, обусловленное стремлением объединить в БИС, на которых строится микро-ЭВМ, узлы и блоки, способные проводить сложные преобразования информации при минимальном количестве внешних проводников. Эта особенность обусловлена возможностью построения в БИС сложных электронных схем при ограничении по числу внешних проводников, не превышающих, как правило, 50 или 100 контактов.

Структура процессора микро-ЭВМ строится с учетом этих особенностей БИС. Наиболее распространенной является схема микро-ЭВМ, имеющая две или три общие магистрали, к которым под воздействием устройства управления могут поочередно подключаться входящие в микропроцессор узлы. Такая структура требует ограниченного числа внешних контактов, но обмен информацией между узлами и блоками должен осуществляться в определенной последовательности.

В микро-ЭВМ процессор строится на БИС, образующих базовый МП-комплект. Процессор микро-ЭВМ может быть реализован в виде одной (однокристальный микропроцессор) или нескольких БИС (многокристальный микропроцессор) .

Для построения остальных блоков микро-ЭВМ используются специализированные БИС или ИС средней степени интеграции. Основные типы ИС, применяемых в микро-ЭВМ, могут быть отнесены к одной из четырех групп: базовый микропроцессорный комплект (МПК) ИС; ИС запоминающих устройств; ИС устройств ввода — вывода информации в микропроцессор; ИС для связи микро-ЭВМ с объектами управления.

Обмен информацией между микропроцессором и остальными блоками микро-ЭВМ осуществляется по трем магистралям: адресной, данных и управляющей.

Магистраль адреса (MA) служит для передачи кода адреса, по которому проводится обращение к устройствам памяти, ввода-вывода или другим внешним устройствам, подключенным к микропроцессору.

Обрабатываемая информация и результаты вычислений передаются по магистрали данных (МД).

Магистраль управления (МУ) передает управляющие сигналы на все блоки микро-ЭВМ, настраивая на нужный режим устройства, участвующие в выполняемой команде.

Использование в микро-ЭВМ большого числа магистралей, в данном примере трех типов, обеспечивает высокое быстродействие и упрощает процесс вычисления. Возможно построение микро-ЭВМ с одной или двумя магистралями, по которым последовательно передаются код адреса и обрабатываемая информация, при этом увеличивается время выполнения команды и усложняется организация обмена информацией между узлами.

Структура микро-ЭВМ определяется архитектурой микропроцессора, составом входящих в МП БИС функциональных узлов, количеством внешних магистралей и организацией обмена информацией.

Микропроцессоры на одном кристалле — однокристальные МП — отличаются фиксированной разрядностью и фиксированной системой команд. Функциональная законченность однокристальных МП требует разместить в одном кристалле блоки дешифратора команд и устройства управления, арифметическо-логический блок, устройства управления внешним обменом, каскады согласования внутренних и внешних сигналов.

Многокристальные МП строятся на основе совокупности БИС, представляющих собой МПК. Каждая БИС, входящая в МПК, позволяет реализовать узел или функциональный блок узла МП. Наиболее характерными узлами МП являются арифметическо-логический блок (АЛБ), составляющий основу операционного устройства, и устройство управления (УУ).

Арифметическо-логический блок предназначен для обработки информации в соответствии с поступающим на него управляющим кодом. Выполняемые в АЛБ операции могут быть разделены на три группы: арифметические, сдвига, логические и пересылок.

В качестве арифметических операций обычно используются операции: сложения и вычитания двух кодов; сложения и вычитания единицы; сложения и вычитания с содержимым признака операции.

К операциям сдвига относятся операции арифметического, логического и циклического сдвигов вправо и влево содержимого регистров АЛБ.

Логические операции и операции пересылок обеспечивают выполнение основных логических функций (сложение, умножение) над содержимым регистров и пересылки содержимого между регистрами и между регистрами и внешними магистралями.

Устройство управления формирует управляющие сигналы на все блоки микро-ЭВМ, синхронизируя их работу, и обеспечивает выборку команд из памяти в соответствии с заложенным алгоритмом.

Рассмотрим несколько подробней функционирование отдельных блоков микроЭВМ.

Операционное устройство МП, предназначенное для выполнения операций над операндами в соответствии с кодом выполняемой команды (арифметической, логической, сдвига или пересылочной), обычно включает в себя АЛБ, блоки регистров общего назначения (РОН), блок формирования состояния регистра условий, блок местного управления.

Арифметическо-логический блок непосредственно выполняет микрооперацию над исходными операндами.

Блок РОН обеспечивает хранение операндов и промежуточных результатов вычислений, характеризуется малым временем обращения и ограниченным количеством регистров.

Блок формирования состояний регистра условий записывает в регистр условий двоичный код, характеризующий арифметические и логические признаки результата операции АЛБ. Содержимое регистра признаков может быть использовано устройством управления для формирования условных переходов по результатам операций АЛБ.

Блок местного управления обеспечивает выполнение текущей микрокоманды и управляет в соответствии с кодом микрокоманды всеми блоками операционного устройства.

Структура операционного устройства зависит от количества внешних магистралей и организации обмена информации по ним, а также от организации внутренних магистралей и порядка обмена информации между блоками операционного устройства.

Операционные устройства, реализованные в составе однокристальных МП БИС, отличаются фиксированной разрядностью и системой команд. Ограничения по числу информационных магистралей и внешних контактов приводят к необходимости организовать последовательный вид передачи информации, при котором по одной информационной магистрали последовательно осуществляется обмен информацией между всеми внутренними узлами БИС и внешними магистралями.

Однокристальные МП БИС не позволяют строить высокопроизводительные микропроцессорные системы с параллельной обработкой информации. Время выполнения команд колеблется от 2 до 10 мкс. Однокристальные МП БИС эффективно применяют в устройствах, не требующих высокого быстродействия и имеющих ограничения по объему аппаратуры и ее стоимости. Они реализованы в сериях К580 и К586 МП БИС, содержащих наряду с микропроцессорами ряд вспомогательных БИС для построения микро-ЭВМ.

Устройство управления микро-ЭВМ, обеспечивает выполнение последовательности микроопераций в соответствии с кодом текущей команды и организует выборку команд программы в соответствии с выполняемой программой. Использование микропрограммирования в реализации устройства управления позволяет создавать его на регулярных структурах, допускающих легко вносить изменения в формируемую последовательность управляющих сигналов.

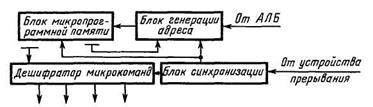

Представленная на рис. 2 обобщенная схема устройства микропрограммного управления содержит: блок микропрограммной памяти, в котором хранятся микрокоманды; блок генерации адреса микрокоманды, формирующий адрес очередной микрокоманды, который в общем случае зависит от кода выполняемой микрокоманды, кодов признаков выполняемых в АЛБ операций, информации блоков синхронизации и прерывания процессора; блок синхронизации, предназначенный для приема управляющих сигналов и формирования последовательности синхросигналов для основных блоков микро-ЭВМ для обеспечения определенной последовательности их работы; дешифратор микрокоманд, формирующий управляющие сигналы, поступающие в исполнительные блоки микро-ЭВМ.

Наиболее распространены варианты реализации устройств управления с использованием в качестве микропрограммной памяти постоянного ЗУ (ПЗУ) или перепрограммируемого ЗУ (ППЗУ) и устройства управления на базе программируемой логической матрицы (ПЛМ).

Рис 2. Обобщенная схема устройства управления.

В первом случае блок памяти микрокоманд выполняют на базе стандартных БИС памяти типа ПЗУ, ППЗУ. Остальные блоки устройства управления объединяют в отдельную БИС или исполняют в виде отдельных узлов на схемах средней интеграции. В устройстве управления на базе ПЛМ все блоки объединяют в одну БИС, представляющую собой фактически законченный цифровой автомат, закон функционирования которого определяется коммутацией внутренних магистралей матрицы.

Устройства управления на ПЛМ. Вэтих устройствах в отличие от рассмотренных схем совмещены функции узла генерации адреса микрокоманды с памятью микропрограммы. Рассмотрим схему такого устройства на примере МПК серии К587 (рис. 3, б).

Рис. 3. Схемы БИС серии К1804 (а) и серии К587 РП1 (б).

Структура устройства содержит память микропрограмм типа ПЛМ, регистр команд РгК, регистр кода условий РгКУ, регистр следующего адреса РгА и регистр признаков управления РгУ.

Регистр признаков управления содержит маски на сигнал записи в регистр команд, регистр следующего адреса и регистр кода условий. Часть сигналов с выхода ПЛМ выводится для управления операционной частью как микрокоманда, а другая часть выходных сигналов ПЛМ не выводится из корпуса БИС и используется для формирования следующего адреса и кода регистра управления. Программируемая логическая матрица позволяет анализировать большое число разрядов, что исключает необходимость в управляемых мультиплексорах. Совокупность всех разрядов РгК, РгКУ и РгА используется как полное адресное слово для ПЛМ.

Регистр команды служит для приема кода команды, задающего устройству управления программу выборки последовательности кодов микрокоманд, выполняя которые микропроцессор реализует алгоритм данной команды. Для этого один из выходов ПЛМ программируется на выработку разрешения на прием новой команды. Выборка той или иной микрокоманды в процессе выполнения алгоритма какой-либо команды микропроцессора не всегда является строго заданной, а может зависеть от условий — результатов операций, зафиксированных в регистре условий.

Регистр адреса является главным задающим звеном при выборке последующей микрокоманды. Разрядность п регистра адреса позволяет устройству управления создавать 2" устойчивых состояний без смены кода команды и кода условий.

Способность ПЛМ порождать новые информационные состояния комбинацией имеющихся закодированных состояний, путем их простого объединения, расширяет

логические возможности ПЛМ как цифрового автомата. Рассмотренное устройство не содержит стековой памяти и, следовательно, не предусматривает модульного программирования. Из рассмотренных устройств на структуру микро-ЭВМ в наибольшей степени влияет вариант реализации устройства управления. Можно выделить три наиболее характерных варианта: реализация в однокристальном процессоре, объединяющем в себе операционную часть и устройство управления; реализация устройства управления в виде микропрограммного автомата с использованием ПЗУ и ППЗУ для записи микрокоманд; реализация устройства управления на основе ПЛМ.

В микропроцессорных комплектах серий К587, К588, К1883 устройства управления реализованы на основе ПЛМ. Микропроцессорные комплекты серий К580, К.1801, К1810, К1816, К1820 содержат в своем составе БИС, в которой реализованы центральный процессор и устройство управления с фиксированной структурой и системой команд. В МПК серий К583, К589, КР1800, КР1802, КР1804 устройство управления строится в виде микропрограммного автомата на базе входящих в эти комплекты БИС, что позволяет потребителю реализовать на их основе необходимую ему систему команд. Микропроцессорные комплекты серий К536, К581 предназначены для построения микро-ЭВМ семейства «Электроника С» и «Электроника-60».

Микропроцессорные комплекты серии К1801 включают в себя однокристальный МП К1801ВМ1, реализующий в себе процессор и устройство управления с системой команд микро-ЭВМ «Электроника-60», и ряда БИС для построения одноплатных микро-ЭВМ. По своим техническим характеристикам МПК серий К580, К1816, К1810, К1820, содержащие однокристальные МП, целесообразно применять для получения устройств цифровой автоматики, простейших контроллеров, а также использовать для построения микро- и мини-ЭВМ различного назначения.

Микропроцессорные комплекты серий К583, К584, К587, К588 предназначены для построения микро-ЭВМ и сложных контроллеров. Благодаря секционной организации, развитой системе магистралей, микропрограммируемости управляющих функций они могут служить основой для построения различных управляющих систем. Малое энергопотребление и высокая помехоустойчивость МПК серий К587 и К588 позволяют проектировать на их основе системы числового программного управления технологическим оборудованием и устройства с ограничениями по потребляемой энергии.

Быстродействующие МП К серий К589, KР1802, КР1804 предназначены для построения микро-ЭВМ и систем быстродействующей автоматики, совместимы по уровням сигналов и могут дополнять друг друга. Микропроцессорные комплекты серий КР1802 и К1804 отличаются подходом к формированию модулей. В МПК КР1804 4-разрядные микропроцессорные БИС содержат все элементы микропроцессора. В МПК серии КР1802 в БИС выполняются отдельные функциональные узлы МП (БИС 8-разрядного АЛ Б, БИС 16 4-разрядных РОН, БИС 16-разрядного арифметического расширителя и т.д.). Отличие по составу модулей рассмотренных МПК позволяет применить для различных областей наиболее подходящий из них по функциональному разбиению. Микропроцессорный комплект серии КР1800 обладает сверхвысоким быстродействием (частота тактовых сигналов 36 МГц) и ориентирован на построение вычислительных средств с высокой производительностью.

ВТОРОЙ ВОПРОС

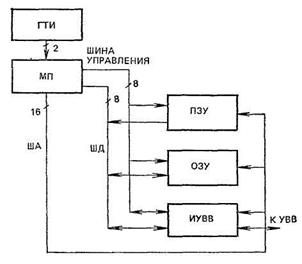

На рис. 4 приведена в качестве примера структура микроЭВМ, реализованной на базе микропроцессорного комплекта КР580. Шестнадцатиразрядная шина адреса (ША) и 8-разрядная шина данных (ШД) и управления образуют интерфейс между микропроцессором (МП), с одной стороны, и ПЗУ, ОЗУ и интерфейсными устройствами ввода — вывода (ИУВВ) — с другой. Выделение отдельных шин для всех управляющих сигналов, адресной информации и данных упрощает организацию обмена информацией между отдельными компонентами и уменьшает время выполнения команд в микроЭВМ. Генератор тактовых импульсов (ГТИ) формирует сигналы, необходимые для работы МП.

Рис. 4. Структура микроЭВМ с раздельными шинами данных и адреса.

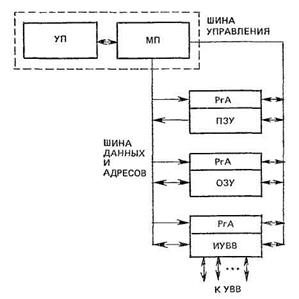

Использование одной шины уменьшает число внешних выводов БИС микропроцессорного комплекта, однако приводит к временному разделению передачи адресов и данных, т. е. к снижению скорости обмена информацией между процессором и адресуемыми устройствами, а также к необходимости применения внешних регистров адреса (РгА).

ТРЕТИЙ ВОПРОС

Представленная на рис. 5 схема иллюстрирует на примере микропроцессорного комплекта К588 организацию микроЭВМ с мультиплексированной шиной адреса и данных.

Такие микропрограммируемые микроЭВМ, как правило, требуют разработки двухуровневого управления - микропрограммного и программного. Это позволяет иметь произвольную систему команд, однако усложняет микро-ЭВМ.

Нормальное функционирование микроЭВМ можно обеспечить лишь при правильном временном соотношении сигналов, определяющих взаимодействие ее компонентов. Поэтому значительную часть технических параметров компонентов МПК составляют различные временные ограничения.

Рис. 5. Структура микроЭВМ с мультиплексированной шиной данных и адреса.

Первичный источник временных сигналов в микроЭВМ – генератор тактовых импульсов, вырабатывающий одно-, двух-, трех- или четырехфазную последовательность импульсов. К параметрам тактовых импульсов предъявляются достаточно жесткие требования, включающие минимальную и максимальную частоты импульсов, максимальные времена фронта и среза импульсов, допуски на низкий и высокий уровни напряжения импульсов, допуски на длительность тактовых импульсов, временные соотношения между тактовыми импульсами различных фаз. Несоблюдение требований к тактовым импульсам может привести к неправильному выполнению операций, поскольку выполнение каждой операции складывается из последовательности действий, каждое из которых имеет вполне определенную длительность. Частота генератора тактовых импульсов обычно стабилизируется кварцем и реализуется в виде отдельного компонента микропроцессорного комплекта или на кристалле микропроцессора (как это сделано в микропроцессорном комплекте К588).

Тактовые импульсы от генератора начинают поступать на микропроцессор сразу после включения источника питания, но запуск микропроцессора осуществляется только по сигналу начальной установки, подаваемому на специальный его вход. По этому сигналу в программный счетчик записывается определенный адрес, с которого микропроцессор начинает выборку команд программы. Кроме того, в некоторых микропроцессорах по сигналу начальной установки производится сброс в нуль нескольких внутренних регистров.

Простейшие способы формирования сигнала начальной установки: а) использование генератора одиночных импульсов, запускаемого, например, от кнопки; б) формирование импульса начальной установки по включению питания с задержкой на время, необходимое для установки номинального значения напряжения питания после включения источника.

Серьезные ограничения накладываются на временные параметры сигналов, обеспечивающих взаимодействие компонентов микроЭВМ. Пока быстродействие компонентов достаточно для правильной реакции на все сигналы микропроцессора, что обычно выполняется в микроЭВМ с небольшим числом компонентов одного микропроцессорного комплекта, никаких проблем по временному сопряжению компонентов не возникает. Усложнение схемы адресации, увеличение емкости памяти, использование компонентов других микропроцессорных комплектов могут привести к несоблюдению некоторых обязательных временных соотношений и, следовательно, к неправильной работе микроЭВМ.

Литература:

1. М.В. Напрасник «Микропроцессоры и микроЭВМ», стр.: 81-84.

2. Л.Н. Преснухин «Микропроцессоры», ч. 1, стр.: 140-162.

ЗАНЯТИЕ 3.1.2 Структурная схема, характеристики и основная элементная база

микроЭВМ «МС1201.01».

ВОПРОСЫ ЗАНЯТИЯ:

1. Назначение, характеристики микроЭВМ «МС1201.01».

2. Структурная схема, состав и элементная база микроЭВМ «МС1201.01».

3. Система команд, режимы адресации и особенности работы микроЭВМ «МС1201.01».

ПЕРВЫЙ ВОПРОС

МикроЭВМ «МС1201.01» представляет собой печатную плату, предназначенную для встраивания в аппаратуру потребителя и выполнения в составе этой аппаратуры функций ввода, хранения, обработки и вывода цифровой информации.

Модификации микроЭВМ различаются типом МП, числом команд, емкостью ОЗУ и быстродействием, но имеют один основной конструктив.

| Характеристика | Модификации | |||

| МС1201 | МС1201.01 | МС1201.02 | МС1201.03 | |

| Тип МП Число команд Емкость ОЗУ, Кбайт | К1801ВМ1 | К1801ВМ1 | К1801ВМ2 | К1801ВМ3 |

МикроЭВМ может применятся в составе технологического оборудования (системы ЧПУ 2Р22 и Контур-1); в контрольно-измерительных и испытательных комплексах; в системах обработки цифровой информации общего назначения.

Во всех возможных применениях микроЭВМ решает одни и теже задачи: ввод, хранение, обработка и вывод информации.

Основные характеристики:

- система счисления для чисел и команд – двоичная;

- основной формат представления чисел и команд – 16 двоичных разрядов;

- принцип работы основных устройств – параллельный;

- быстродействие при выполнении команд типа «СЛОЖЕНИЕ»

- при регистровом методе адресации 400 ± 100 тыс. оп/с;

- при косвенно-регистровом методе адресации 180 ± 40 тыс. оп/с;

- число РОН – 8;

- системный канал микроЭВМ позволяет прямо адресоваться в области памяти

64 КБайта;

- емкость ОЗУ 28 Кбайт 16-разрядных слов;

- емкость системного ПЗУ 4 КБайта слов;

- питание осуществляется от внешних источников постоянного тока с

номинальным значением напряжения +5 В (+5 В и +12 В для МС1201), ток не

более 2,4 А, потребляющая мощность не более 12,6 Вт;

- наработка микроЭВМ на отказ – не менее 10 000 часов, на сбой – не менее

500 часов;

- срок службы – не менее 10 лет;

- габаритные размеры 252×296×12 мм, масса не более 0,8 кг;

- в качестве базового программного обеспечения микроЭВМ приняты: тест

мониторная операционная система (ТМОС); операционная система с

разделением времени (ОС ДВК).

ВТОРОЙ ВОПРОС

МикроЭВМ «МС1201.01» состоит из следующих основных и вспомогательных функциональных блоков и узлов.

Основные:

- процессор (ПРЦ);

- ОЗУ;

- системное ПЗУ (СПЗУ);

- устройство байтового параллельного интерфейса (УБПИ);

- устройство последовательного ввода-вывода (УПВВ);

- устройство интерфейса накопителя на гибких магнитных дисках (УИ ГМД);

- контролирующее устройство для ПЗУ пользователя (КУ ПЗУ);

- регистр режима начального пуска (РНП);

- узел оптоэлектронной развязки сигналов (УОР).

Вспомогательные:

- корректор сигналов управления канала (КСК);

- генератор тактовых импульсов (ГТИ-1, ГТИ-2);

- преобразователь напряжения (ПН-5 В);

- приемо-передатчики сигналов (ПП1…ПП4);

- блок управления приемо-передатчиками сигналов канала (БУПП)

МикроЭВМ представляет собой систему функциональных блоков, связь между которыми осуществляется через единый системный канал (типа «Общая шина») обмена информацией с мультиплексированием шин адреса и данных.

Элементная база микроЭВМ построена на ИМС серий К1801 (8 штук), К531 (15 штук), К155 (23 штуки), К555, КР565 (32 штуки). Основу элементной базы составляют микросхемы серии К1801, выполненные по n-канальной МОП технологии.

На ИМС К1801 построен микропроцессор, К1801РЕ1 представляет собой системное ПЗУ, К1801ВП1-030 устройство управления ОЗУ, К1801ВП1-031 устройство управления байтового параллельного интерфейса, К1801ВП1-034 устройство передачи информации УБПИ, К1801ВП1-035 УПВВ, К1801ВП1-033 устройство управления интерфейса НГМД.

На микросхемах серии К531 в основном построены приемо-передатчики сигналов канала, а ИМС К555 – представляет собой усилитель сигналов.

Интегральные микросхемы серии КР565РУ3 (РУ6 – МС1201.01 и МС1201.02) образуют накопитель ОЗУ динамического типа, полная емкость накопителя 32 КБайта 16-разрядных слов или 8 банков памяти по 4 КБайта в каждом. Для пользователя доступны лишь 7 банков памяти, т.е. 28 Кбайт слов. ОЗУ состоит из накопителя информации (Н ОЗУ), устройства управления ОЗУ (У ОЗУ), буферного регистра данных(БРД), переключателя банков П3 на рисунке 2 (БВБ на схеме 1).

Системное ПЗУ предназначено для хранения программ пульта начального загрузчика с НГМД и резидентного проверяющего теста.

Имеется возможность установки дополнительной микросхемы ПЗУ объемом 4 КБайта 16-разрядных слов в контактирующее устройство (рис. 2), расположенное на плате.

Переключатели П1 и П2 (рис. 2) служат для задания режимов начального пуска, адресов регистров и векторов прерываний внешних устройств.

Разъем Р1 служит для подключения внешнего устройства к последовательному каналу ввода-вывода, а разъем Р2 – для подключения устройств к байтовому параллельному каналу ввода-вывода, а также для подключения НГМД.

Унификация по конструктивному исполнению, системе команд, интерфейсу канала с ЭВМ типа «Электроника-60», позволяет наращивать технические возможности микроЭВМ за счет подключения через канал дополнительных типовых функциональных устройств, а также унифицированных устройств, разработанных пользователем.

Рис. 1. Структурная схема микроЭВМ «МС1201.01»

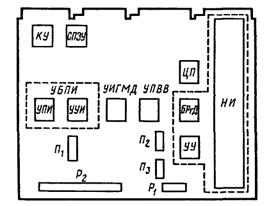

Рис. 2. Схема расположения основных устройств

на плате микро-ЭВМ «Электроника МС1201.01 (02)»

ТРЕТИЙ ВОПРОС

В микроЭВМ «МС1201.01» применяются следующие режимы адресации: регистровый, косвенно-регистровый, автоинкрементный, косвенно-автоинкрементный, автодекрементный, косвенно-автодекрементный, индексный и косвенно-индексный.

МикроЭВМ использует следующие типы команд: безадресные, одноадресные и двухадресные.

Связь между устройствами, подключенными к каналу микроЭВМ осуществляется по принципу «активный – пассивный».

В любой момент времени только одно устройство является активным и управляет циклами обмена информацией в канале. Передача информации осуществляется по асинхронному принципу при помощи специальных сигналов синхронизации К ВВОД Н; К ВЫВОД Н; К СИП Н; К СИА Н, т.е. на инициирующий обмен данными сигнал от активного устройства должен поступить ответный сигнал от пассивного устройства.

В микроЭВМ установлены следующие приоритеты обслуживания прерываний между интерфейсными устройствами ввода-вывода информации:

1 – от УПВВ.

2 – от УИ ГМД.

3 – от УБПИ.

Устройства прямого доступа к памяти в составе микроЭВМ нет. РОН процессора (R0 – R7) могут служить в качестве накопительных регистров, индексных регистров, регистров автоинкрементной и автодекрементной адресации и других целей. Кроме того R6 выполняет функцию регистра указателя стека (РУС), а R7 функции регистра счетчика команд (РСК). Формат регистров 16 двоичных разрядов, при байтовых операциях используются 8 младших разрядов регистров.

Дата добавления: 2015-12-08; просмотров: 2183;