Рекомендации по наладке контроллера параллельного обмена.

Особенностью разработки УС является опасность выхода из строя компьютера, к которому подключается изготовленное УС. В первую очередь это относится к УС, ориентированным на ISA, то есть подключаемым к "внутренностям" компьютера. Большое число сигналов интерфейса ISA, подключение к нему системных устройств компьютера, сложность алгоритмов взаимодействия по ISA, использование внутреннего источника питания — все это приводит к тому, что вероятность поломки компьютера довольно велика.

Шинная организация ПЭВМ характеризуется большим количеством входных, выходных и двунаправленных сигналов, которые должны одновременно формироваться и одновременно контролироваться. Применение стандартных приборов в этом случае потребует большого времени. Поэтому изготавливаются специальные многоразрядные формирователи входных воздействий и регистраторы ответных реакций, существенно упрощающие этот процесс. Большую эффективность имеют системы, в которых предусмотрена та или иная степень автоматизации процесса отладки. При этом часть трудоемких операций можно возложить на персональный компьютер, который служит основой такой системы.

Метод статической отладки цифровых устройств, как следует из его названия, позволяет контролировать работу этих устройств или их отдельных узлов в статическом режиме, то есть в режиме неизменных входных и выходных сигналов. Этот метод основан на том положении, что большинство цифровых устройств может находиться в каждом из своих состояний бесконечно большое время. Он позволяет выявлять по различным оценкам до 80% неисправностей.

Прежде всего это внутренние неисправности микросхем отлаживаемого устройства, приводящие к нарушениям в логике их работы, к невыполнению таблицы истинности. Например, выход логического элемента не реагирует на один или несколько входных сигналов.

Особенность УС как объекта отладки — однотипность набора входных, выходных и двунаправленных сигналов со стороны разъема интерфейса компьютера и однотипность последовательностей этих сигналов в соответствии с протоколом обмена по интерфейсу. Это позволяет обеспечить довольно высокую степень автоматизации процесса отладки и облегчить труд оператора, на долю которого остается только выбор режима работы и анализ результатов контроля.

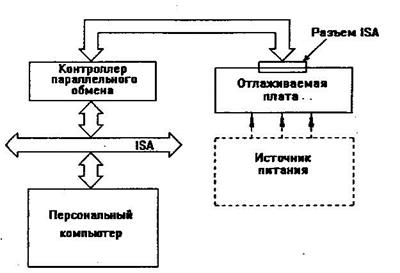

Реализовать систему статической отладки на базе персонального компьютера можно, если использовать разработанный универсальный контроллер параллельного обмена (и, конечно же, соответствующие программные средства). В этом случае аппаратура системы включает в себя только компьютер, рассмотренный контроллер и соединительный кабель, оканчивающийся магистральным разъемом ISA, к которому и подключается исследуемая плата УС (рис 5.3). В принципе, в случае данной системы отлаживаемая плата может быть любой, главное, чтобы количество ее внешних сигналов не превышало количество внешних линий контроллера параллельного обмена. Но для каждой платы нужен свой соединительный кабель (или кабель с индивидуальными зажимами для каждой линии) и, самое главное — свое программное обеспечение.

Рис. 4.3. Функциональная схема статической отладки УС ПЭВМ

Рассмотрим несколько упрощенно управление внешними линиями контроллера параллельного обмена при пошаговой эмуляции машинных циклов ISA. Но сначала выделим минимальный набор сигналов ISA, необходимый в системе отладки. Пусть речь идет только об отладке УС, работающих как устройства ввода/вывода. В этом случае достаточно использовать 10 разрядов адреса (SAO ... SA9), 8 или 16 разрядов данных (SDO ... SD7 или SDO... SD15), два строба обмена (-IOR и -IOW) и два управляющих сигнала (BALE — не обязательно и AEN). Адресные и управляющие сигналы должны быть определены как выходные, данные — как двунаправленные. Однако надо учесть, что в системе отладки обязательно надо предусмотреть контроль правильности информации, выводимой на выходные линии. Все это легко позволяет сделать контроллер параллельного обмена.

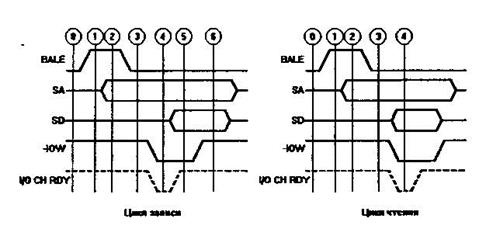

Выделим шаги (или точки останова), которые будут использованы при пошаговой отладке (рис. 5.4). Принцип выделения здесь очень простой: каждый новый шаг отличается от предыдущего изменением хотя бы одного сигнала. При этом если задержка между сигналами определяется только временем распространения сигналов по магистрали или только временем срабатывания логических элементов (например, между -IOR и SD), то мы считаем их одновременными, так как при статической отладке обнаружить такой сдвиг все равно невозможно.

Рис. 4.4. Шаги (точки останова) в циклах записи и чтения ISA.

На нулевом шаге (исходное состояние) мы должны проверить отключение платы от магистрали. Первый шаг, в принципе, не обязателен, так как обычно в УС на нем ничего не происходит. На втором шаге проверяется работа селектора адреса. На третьем — контролируется реакция УС на сигнал BALE (он используется довольно редко). Шаги 4 ... 6 (для цикла записи) или четвертый шаг (для цикла чтения) — это проверка выработки внутренних стробов обмена УС и функционирования буферов данных.

Последовательности сигналов (рис. 4.4) могут вырабатываться компьютером нс только с остановками на каждом шаге, но и без остановок (с максимально возможной для обмена компьютера с используемым контроллером скоростью). Это, конечно же, не будет истинным режимом реального, времени, но быстрое периодическое повторение этих циклов облегчает отладку некоторых узлов с помощью осциллографа (уже упоминавшаяся квазидинамическая отладка).

Перед началом отладки проводится проверка отключения отлаживаемой схемы УС от магистрали ISA. То есть УС должно быть пассивно, если к нему нет обращений. Если же обнаруживаются какие-нибудь активные линии, то на экран выводится информация об ошибке с указанием наименований ошибочных сигналов и характера неисправности.

Проверка установки схемы УС в исходное состояние по сигналу магистрального сброса (RESET DRV). Этот сигнал (выходной) формируется контроллером параллельного обмена и требует только два шага статической отладки: сигнал активен, сигнал пассивен. Такая проверка часто является необходимой, так как некоторые схемы УС будут неправильно работать, если их не инициализировать.

Проверка, на какие адреса отвечает УС. В стандарте ISA не существует магистрального сигнала подтверждения, соответствующего ответу УС на обращенный к нему цикл (как, например, в системных магистралях Q-bus или Unibus). Сигнал I/O СН RDY используется только медленными УС, не успевающими выполнить цикл за положенное время, к тому же он очень короткий для статической отладки. Поэтому, если анализировать только канальные сигналы, мы не сможем определить, на какие адреса отвечает наше УС. Здесь возможно два пути. Простейший состоит в том, что мы проводим циклы чтения из всех возможных адресов и проверяем считанную из них информацию. Если в каких-то адресах она отлична от пассивного состояния (FFFF для 16-разрядного УС), то мы считаем, что на эти адреса данное УС отвечает. Понятно, что этот путь ненадежен, так как действительно считанная из УС информация может быть в данный момент как раз равной FFFF.

Далее должна следовать собственно отладка, которая проводится или в статическом, пошаговом режиме (обязательный этап), или в квазидинамическом режиме. В режиме отладки мы проверяем формирование внутренних стробов обмена УС, работу буферов, правильность записываемых и читаемых данных. Функционирование интерфейсной части УС может быть проверено практически всегда полностью. С операционной частью УС дело обстоит сложнее. Однако, если она содержит в себе только входные и выходные порты, как, например, в схеме универсального контроллера параллельного обмена, то и для нее процесс отладки проводится без проблем. Если же в операционной части есть динамические узлы (генераторы, одновибраторы, микропрограммные автоматы и т.д.), то часто может помочь квазидинамический режим с бесконечным повторением циклов обмена и осциллограф.

Помимо перечисленных обязательных функций система отладки может моделировать целые серии циклов обращения к УС, позволяющие легко отлаживать, например, УС с буферным ОЗУ, к которому предусмотрен последовательный доступ. Понятно, что при большом объеме такого ОЗУ произвести пошаговую запись всех его ячеек или пошаговое чтение из них очень непросто, если вообще возможно. Для реализации данной функции в системе отладки должен быть предусмотрен некий специальный язык для задания требуемых последовательностей циклов.

Заключение.

С помощью разработанного универсального контроллера параллельного обмена и соответствующего программного обеспечения можно реализовать практически любой стандартный интерфейс или даже несколько интерфейсов одновременно (Centronics, IEEE 488, RS— 232 и т.д.). Необходимо только учитывать ограничение на быстродействие эмулируемого интерфейса, связанное с быстродействием компьютера. Точно так же можно организовать свой интерфейс, реализующий протокол, наиболее соответствующий решаемой задаче. При этом все УС можно разместить во внешнем конструктиве, а в компьютер установить только разработанный контроллер. Такой подход обеспечивает все преимущества вынесения УС из компьютера: снятие ограничений на сложность и количество УС, снижение наводок и помех и т.д., хотя и увеличивает стоимость системы в целом. По сравнению со стандартными интерфейсами компьютера в данном случае гораздо проще достигается сопряжение с большим количеством УС (все форматы и протоколы мы выбираем самостоятельно).

Шина ISA в настоящее время считается устаревшей. Ее развитие не имеет перспектив. Шина ISA исключена из состава архитектуры современных ПЭВМ по следующим причинам:

1. Шина ISA характеризуется чрезмерно большим количеством проводников при малой разрядности (по отношению к шине PCI), что снижает ее надежность.

2. Частота шины (16 МГц) является очень низкой по современным представлениям.

3. Шина ISA не поддерживает систему PnP, т.е. считается неинтеллектуальной.

4. Разработка устройств сопряжения для шины ISA характеризуется высокой трудоемкостью и малой надежностью этих устройств. Созданная для этих целей шина USB позволяет выполнять разработку УС с гораздо меньшими трудозатратами и большим эффектом.

ISA

Дата добавления: 2015-10-13; просмотров: 1101;