Анализ комбинационных устройств (без памяти)

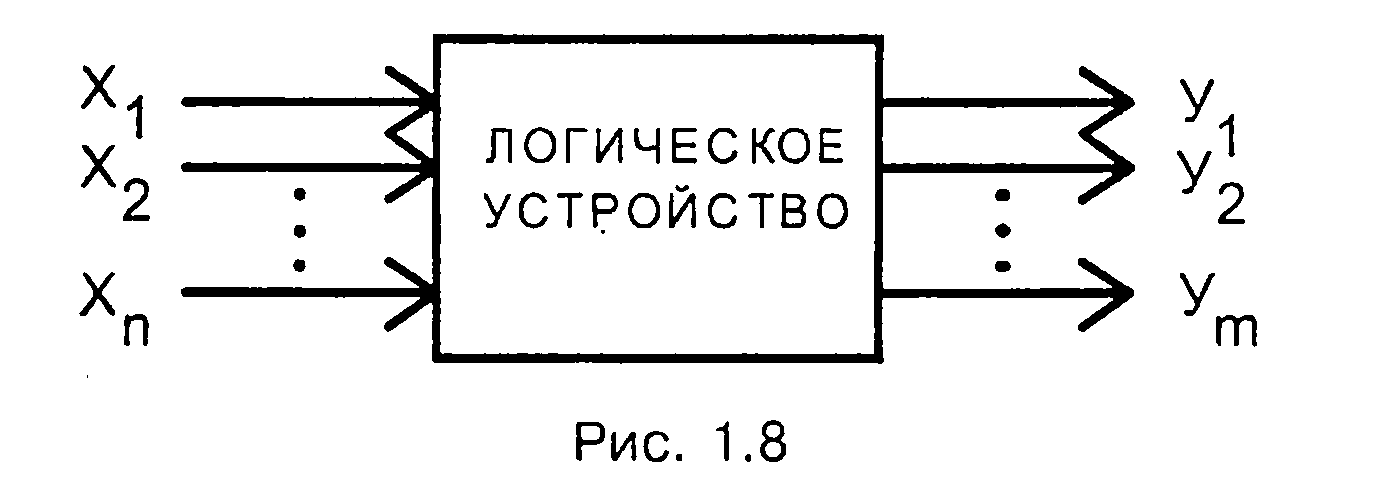

Комбинационные устройства — цифровые устройства, выходные сигналы которых зависят только от входных сигналов, действующих в текущий момент времени, и не зависят от предыдущего внутреннего состояния, предшествующих входных сигналов. Другими словами, комбинационные устройства — это устройства без памяти. Их можно представить в виде многомерного n, т — многополюсника (рис. 1.8).

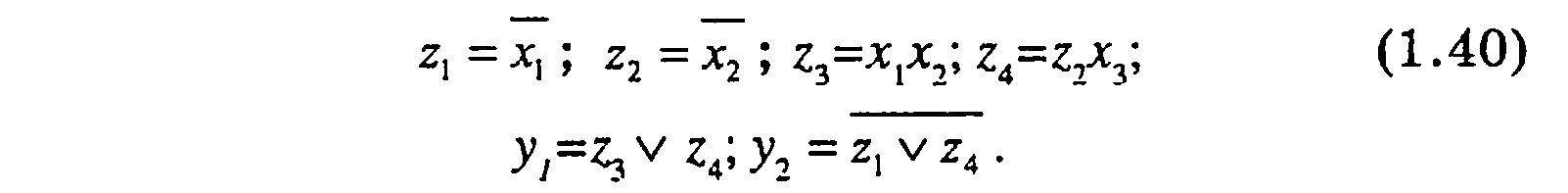

Условия функционирования комбинационного устройства можно представить в виде системы логических функций, называемых функциями выходов

Задача анализа условий функционирования сводится к определению всех функций выхода дискретного устройства по известной принципиальной схеме реального устройства. Результат анализа представляется в виде функций алгебры логики и таблицы истинности. Другими словами, необходимо установить функциональную зависимость между входными переменными х1, х2,... хn комбинационного устройства и значениями выходных сигналов y1, у2,...ут в виде формул алгебры логики или таблиц истинности.

Анализ комбинационного устройства целесообразно проводить в следующей последовательности.

1. На функциональной схеме выходы всех логических элементов (ЛЭ) обозначить символами промежуточных переменных.

2. Определить и записать функции непосредственных связей, устанавливающие зависимости выхода каждого ЛЭ от его входов на основе элементарных логических функций.

3. Путем подстановок исключить все внутренние переменные. Получить зависимости выходов комбинационного устройства у1,..., ут от его входов х1,..., хп, использованием тождеств и соотношений алгебры логики.

4. Составить таблицу истинности.

5. Представить результаты анализа в удобной для пользователя форме.

Последний пятый пункт алгоритма анализа в общем случае уже является переходом к задаче синтеза комбинационного устройства.

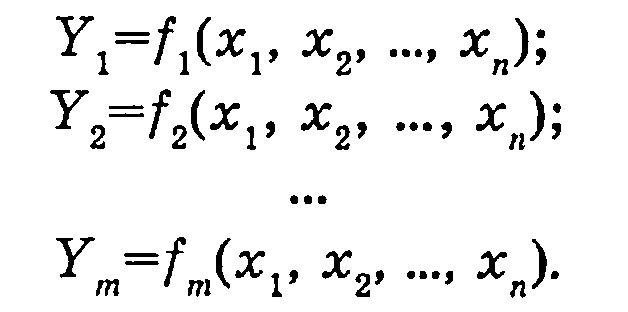

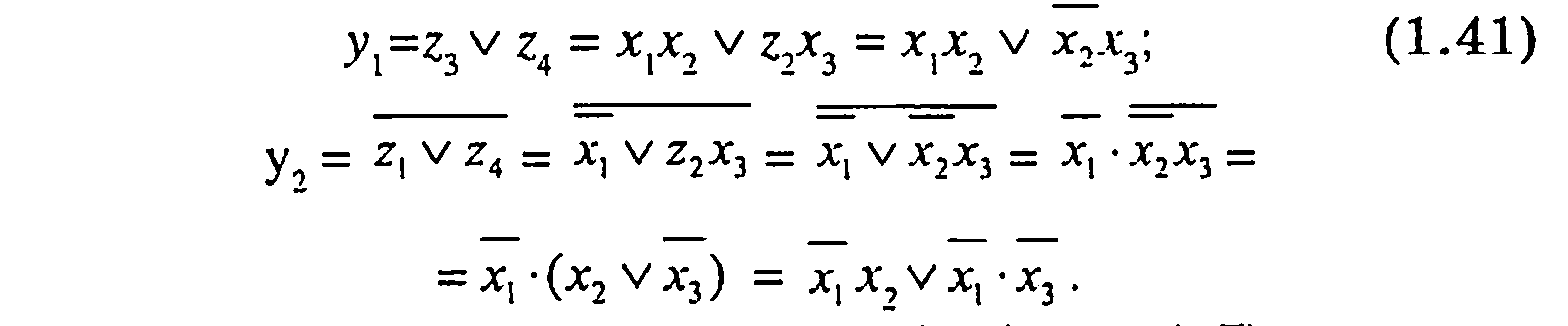

Приведем пример анализа комбинационного устройства без памяти (рис. 1.9). Оно содержит элементы НЕ (DD1, DD2), И (DD3, DD4), ИЛИ (DD5), ИЛИ-HE (DD6).

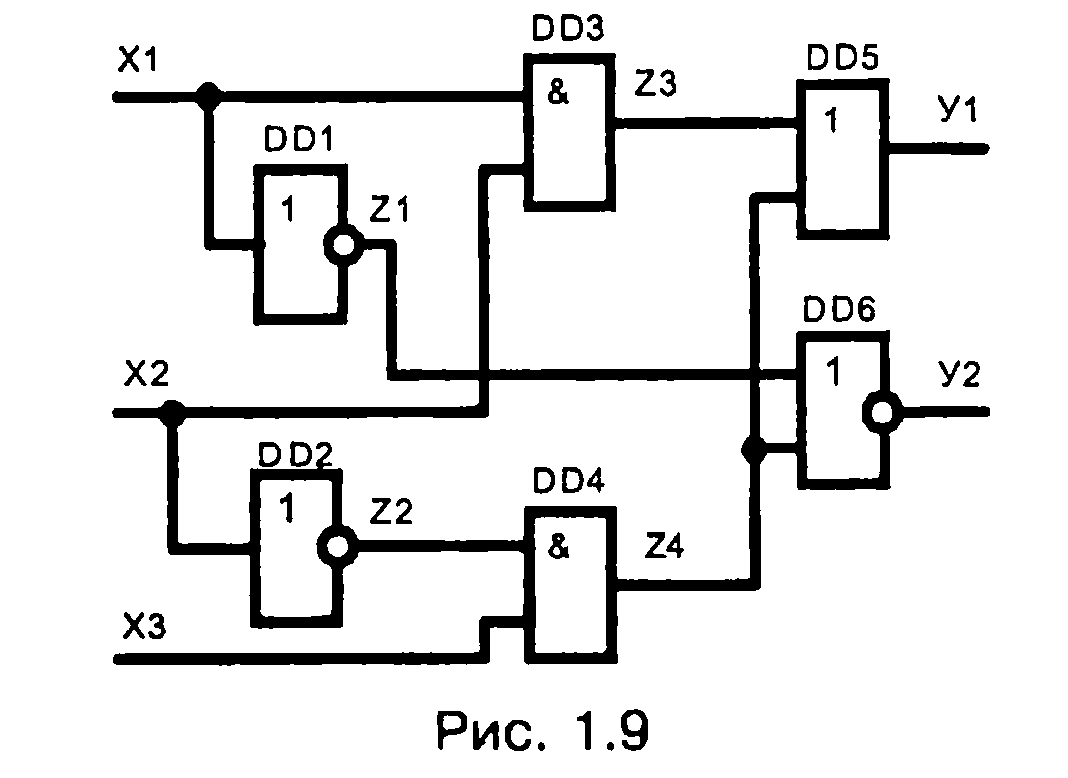

Установим промежуточные переменные z1, z2, z3, z4 и запишем функции связи входов и выходов для каждого ЛЭ.

исключим внутренние промежуточные переменные

исключим внутренние промежуточные переменные

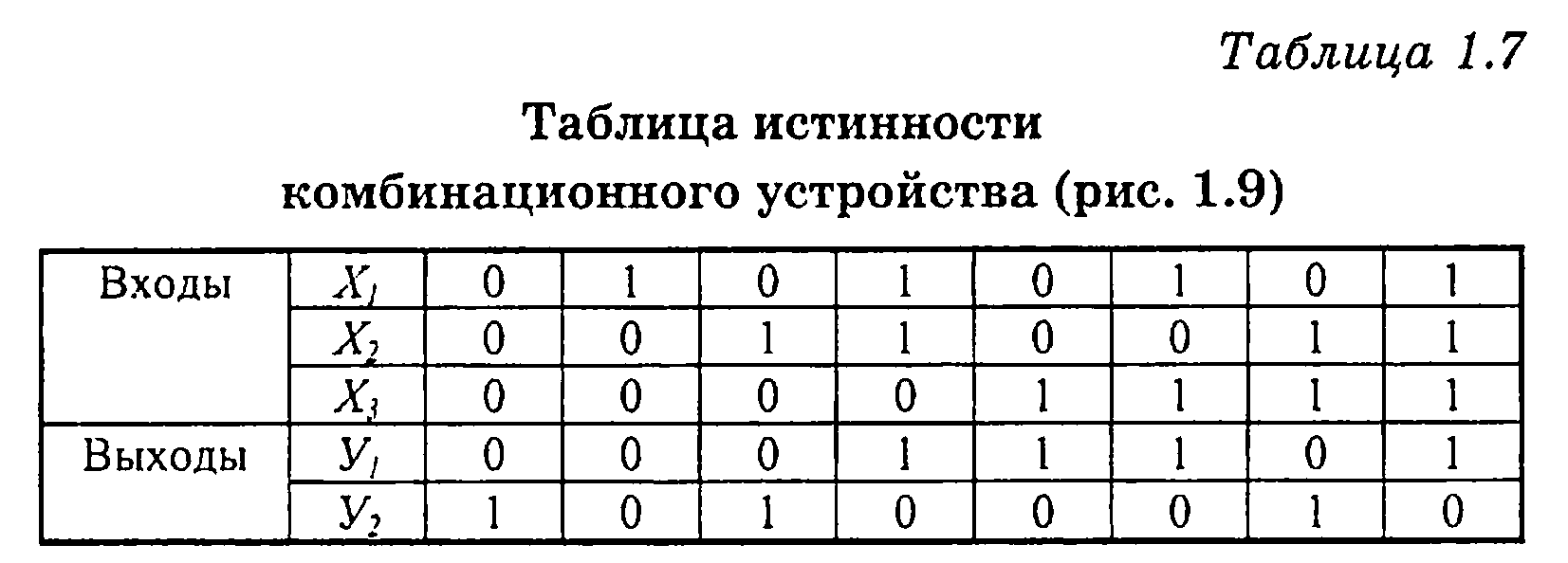

Составим таблицу истинности (таблица 1.7)

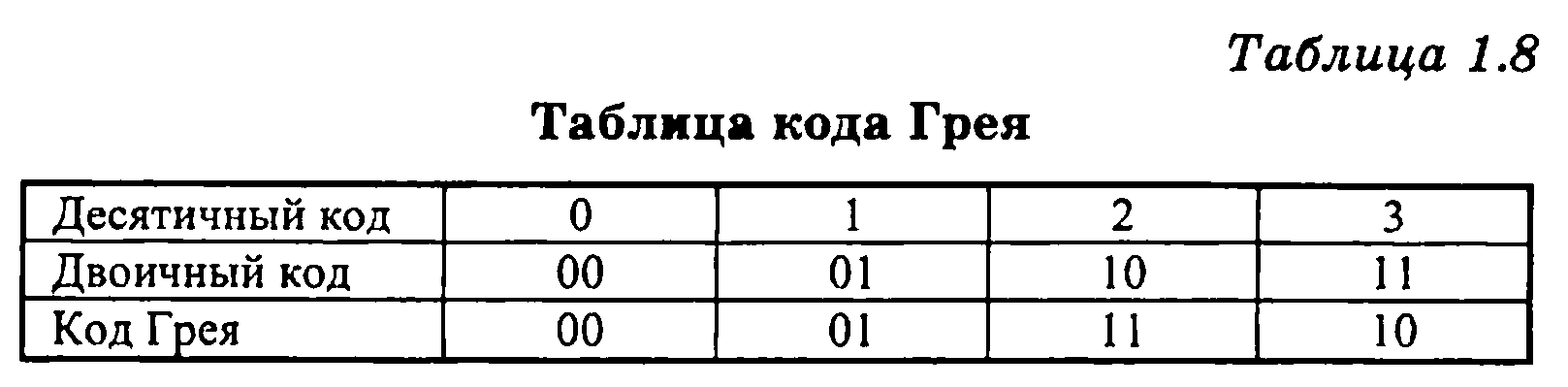

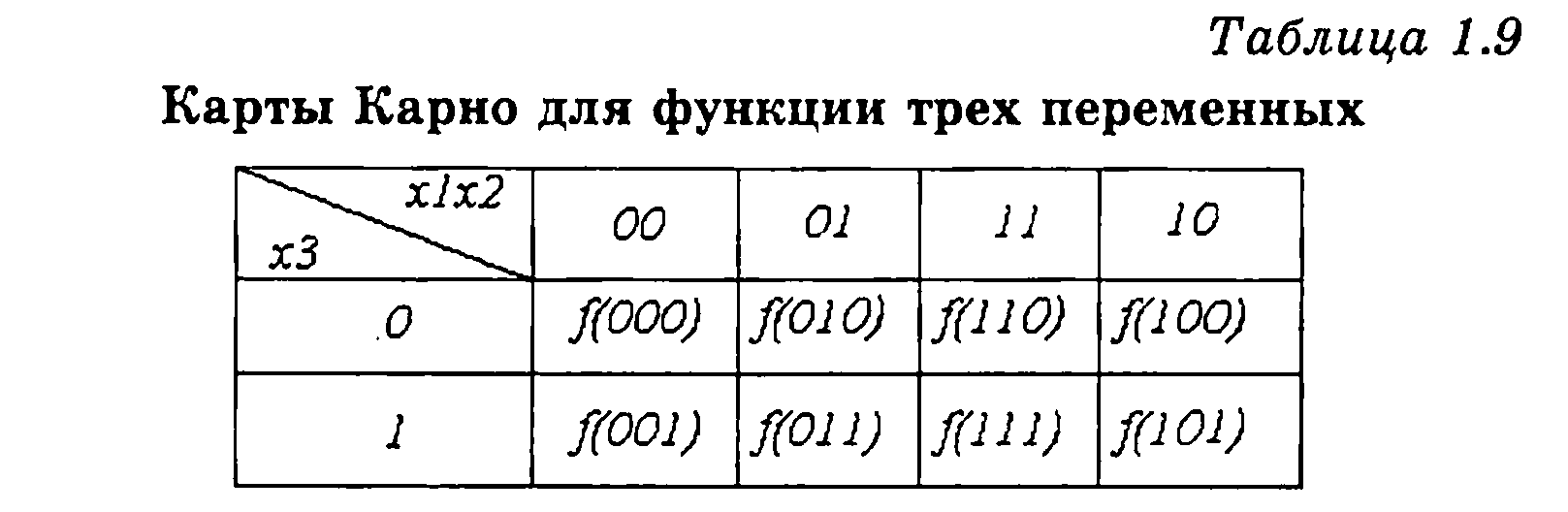

Таблицы истинности могут быть записаны в других формах, которые могут оказаться более удобными в различных случаях: карты Вейча, карты Карно и т. д. Например, при записи таблицы истинности в виде карты Карно аргументы функции (входные переменные) делятся на две группы. Комбинации значений аргументов одной группы приписываются столбцам таблицы, комбинации значений аргументов другой группы — строкам таблицы. Столбцы и строки обозначаются комбинациями, соответствующими последовательности чисел в коде Грея. В коде Грея переход от одной комбинации к другой соседней сопровождается изменением логической переменной только в одном разряде.

В двоичном коде переход от 1 к 2 сопровождается изменением 01—>10 логической переменной сразу в двух разрядах.

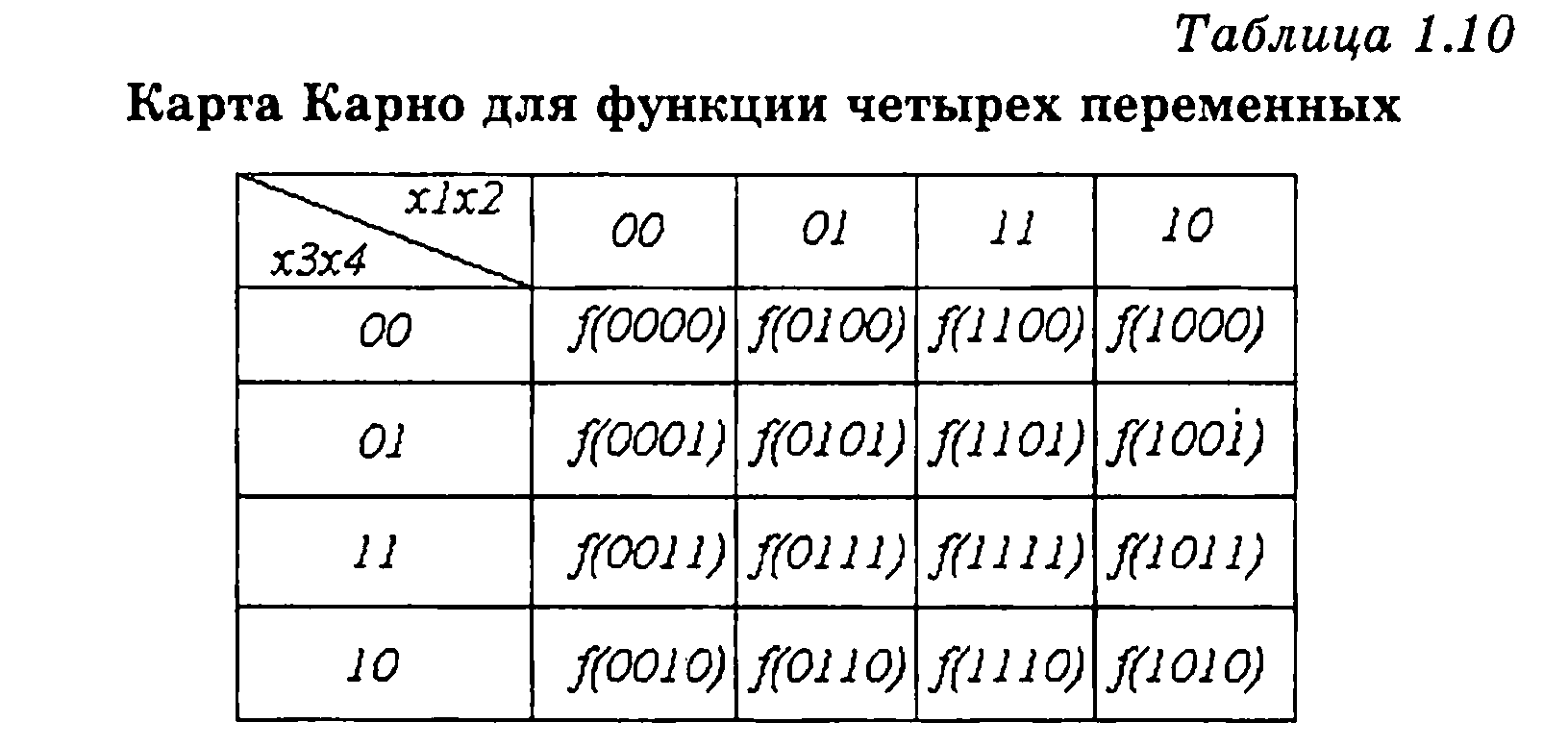

Таблицы 1.9 и 1.10 показывают карты Карно для функций трех и четырех переменных.

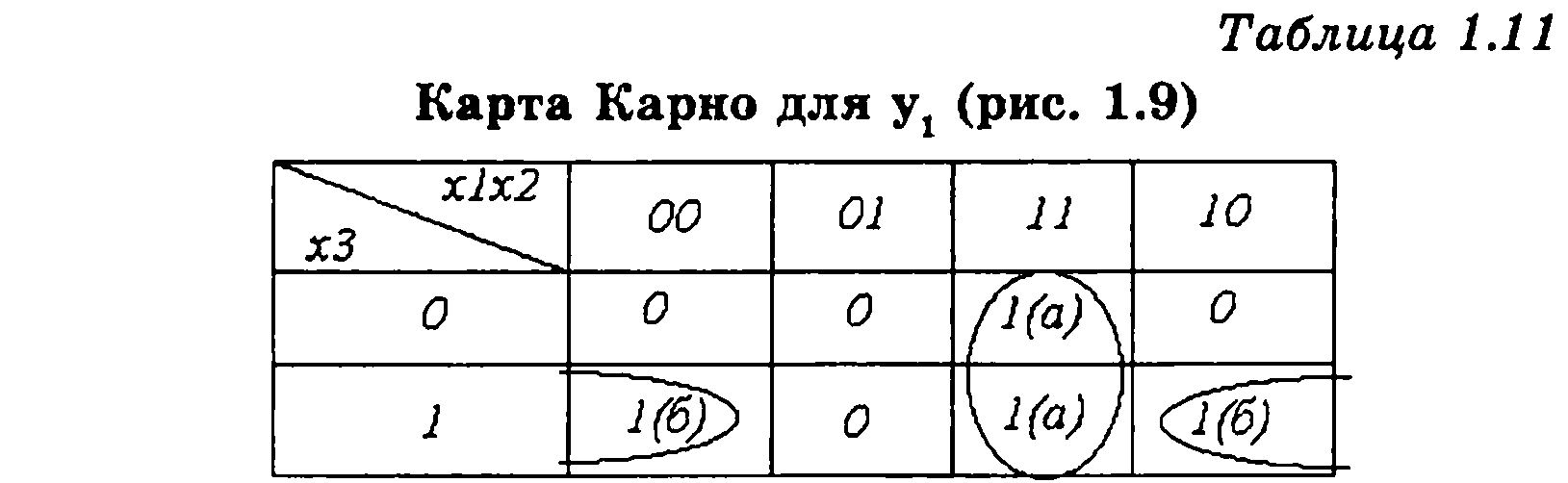

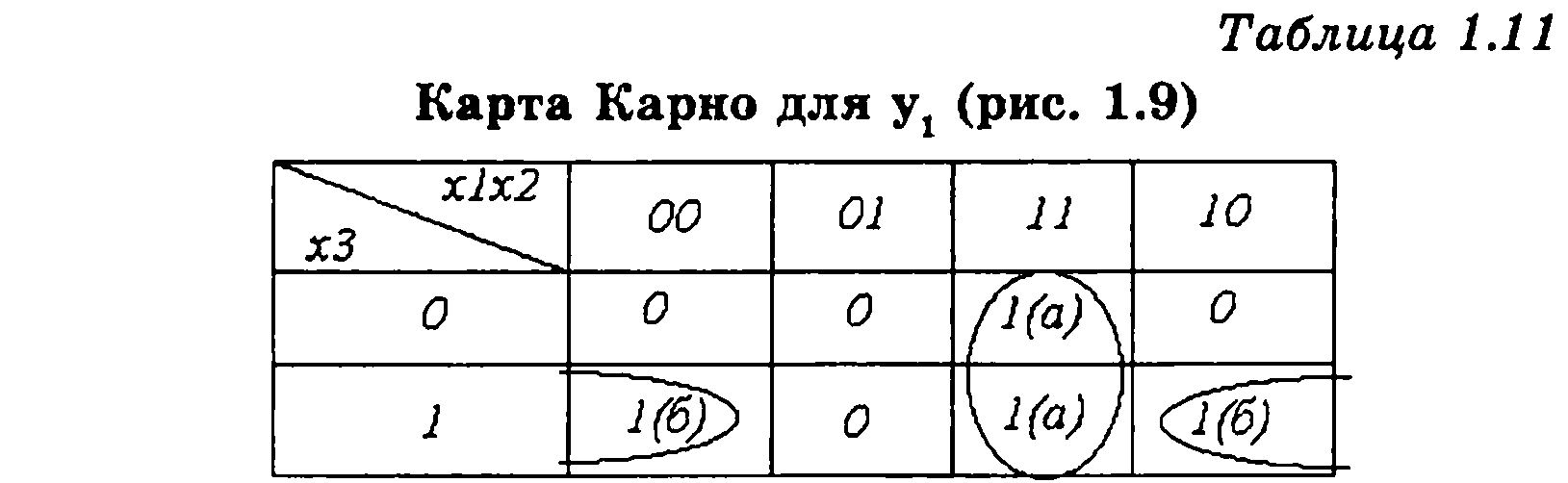

При заполнении карты Карно в ее клетки заносятся значения функции f(x), которые соответствуют набору переменных на пересечении столбца и строки. Запишем пример карты Карно для выхода y1 (Таблица 1.11).

Единичные значения функции у1 соответствуют наборам х1х2х3 = 110, 001, 101, 111.

Представленный алгоритм анализа справедлив при следующих допущениях:

1. переход логического устройства из одного состояния в другое происходит скачкообразно (не учитывается крутизна переднего и заднего фронта сигналов);

2. изменение сигналов в различных участках схемы происходит одновременно (не учитываются задержки в различных элементах схемы).

Ранее в п. 1.1. отмечались три модели логических устройств, учитывающие технические особенности логических элементов:

1) логическая модель;

2) модель с временными задержками;

3) модель с учетом электрических параметров и характеристик.

Для алгоритма анализа первой логической модели достаточно только знания соотношений алгебры логики. Во второй модели учитываются временные задержки логических элементов. Иначе в результате могут возникнуть ситуации, приводящие к ложным срабатываниям. Расчеты по третьей модели являются достаточно сложными, требуют анализа входных и выходных токов каждого ЛЭ. В результате этих расчетов может выясниться, что требуется применение микросхем с более мощными выходами либо включение дополнительных элементов.

Причиной задержек в ЛЭ являются переходные процессы. Переходным процессом называют функционирование дискретного устройства в течение интервала времени, непосредственного следующего за моментом изменения сигналов в схеме.

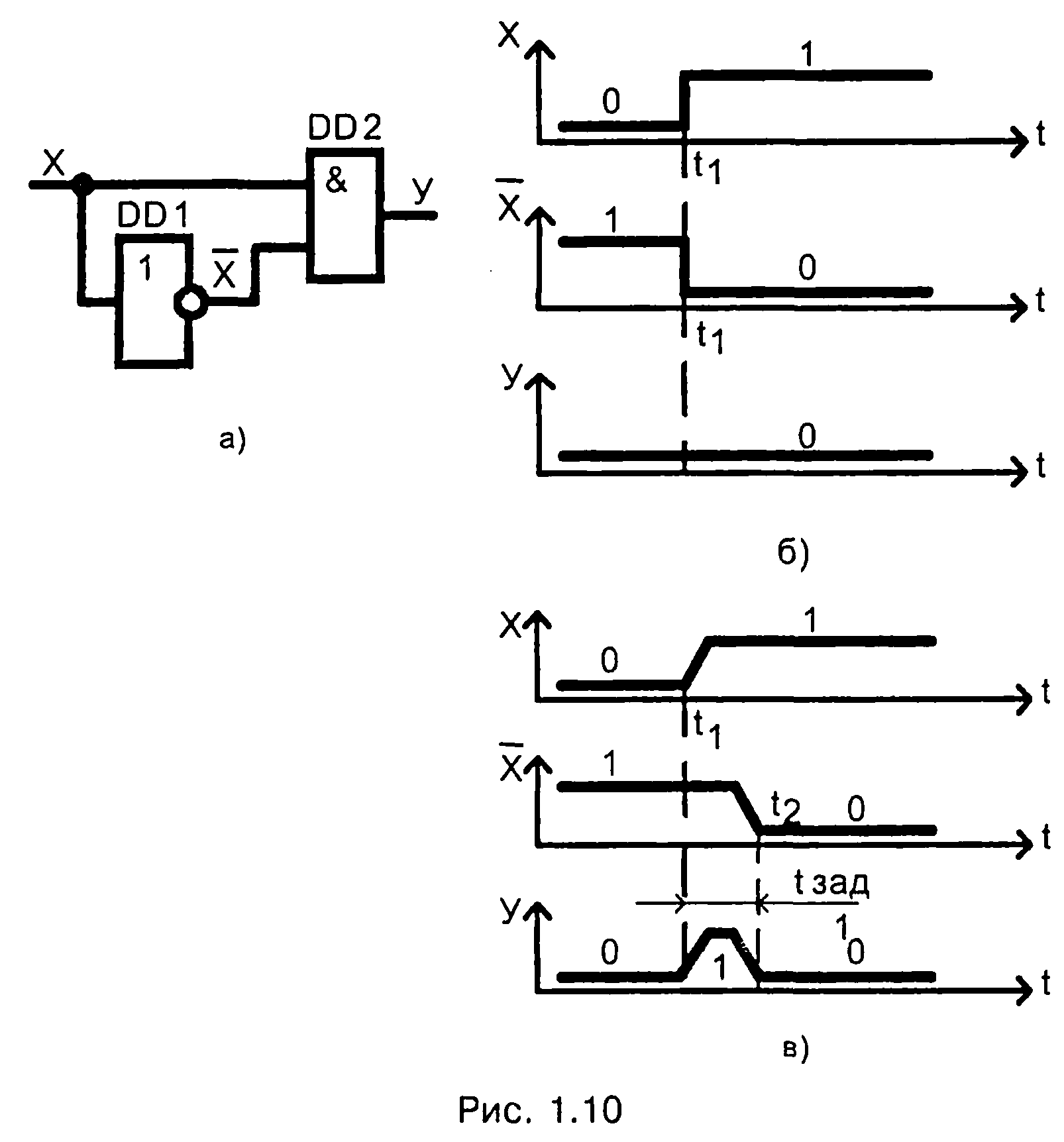

Переходные процессы связаны с конечностью скорости электромагнитных процессов, протекающих в электронных цепях. Входные сигналы, проходя через комбинационную схему, испытывают временную задержку. Максимальная длительность задержки (длительность переходных процессов) определяется числом последовательных включенных ЛЭ. Временные задержки в комбинационных схемах могут привести к кратковременным сбоям, ложным срабатываниям. Рассмотрим пример (рис. 1.10)

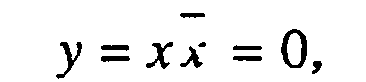

Схема на рис. 1.10, а соответствует логическому выражению (1.16) соотношения с нулем

согласно которому на выходе должен быть постоянно логический ноль. Такой выходной сигнал будет при идеальных ЛЭ (рис. 1.10, б), у которых отсутствует временная задержка. Задержка распространения в элементе НЕ (DD1), равная t3aдl = t2 – t1 приводит к возникновению кратковременного импульса логической единицы (рис. 1.10, в).

Анализ влияния переходных процессов на работу комбинационных устройств проводят с помощью карт Карно:

3. Единичные клетки функции объединяются в контуры.

4. Проверяется наличие соседних единичных клеток, принадлежащих различным контурам.

5. Найденные пары клеток указывают на то, что в схеме возможны сбои либо ложные срабатывания.

В карте Карно (таблица 1.11) для схемы рис. 1.9 выделим два единичных контура: контур (а) для наборов х1х2х3 = (110, 111), контур (б) для наборов х1х2х3= (101, 001)

Эти два контура не пересекаются и имеют две соседние единичные клетки, соответствующие наборам 111-101.

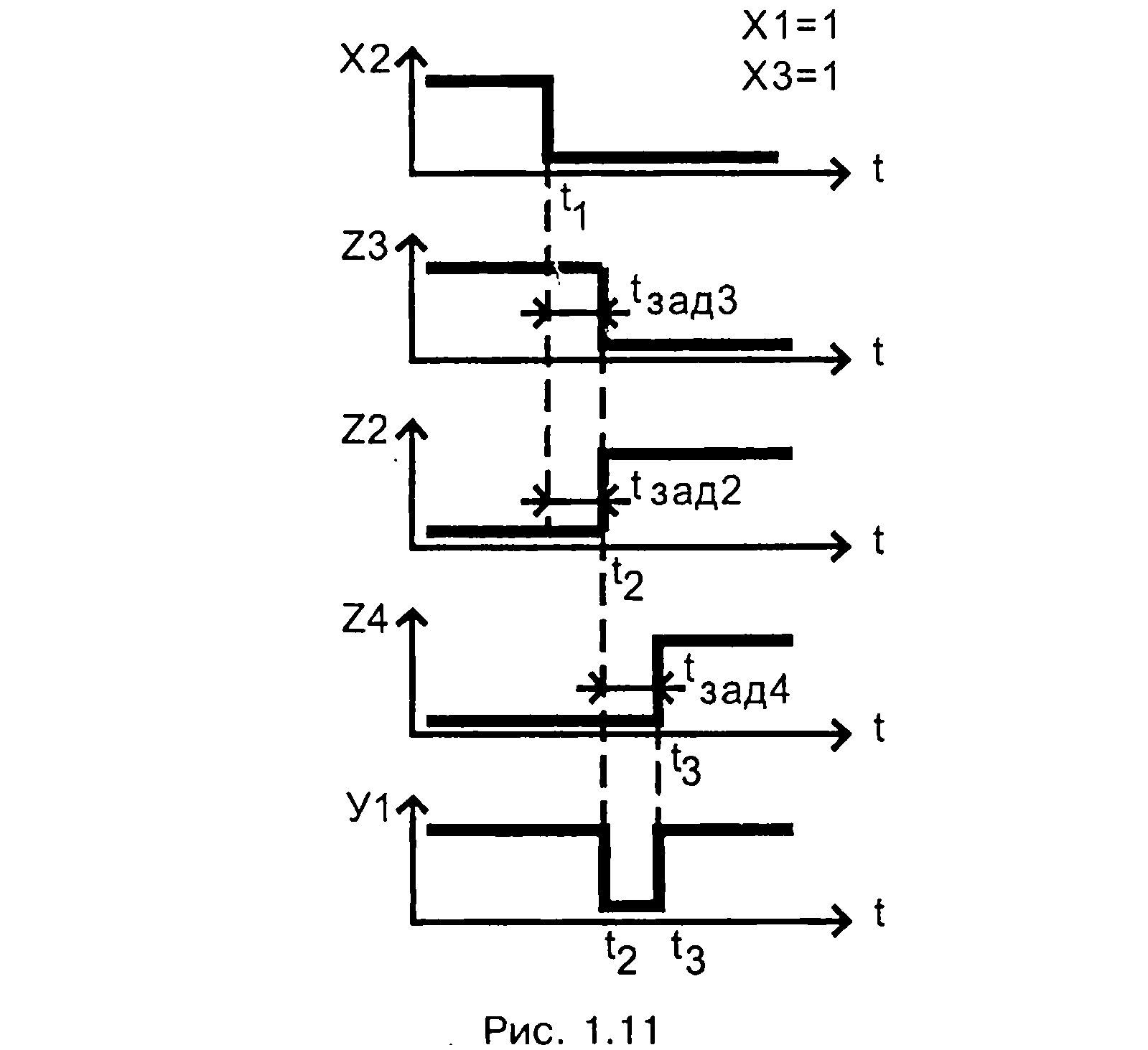

Следовательно, при переходе х1х2х3 = 111—> х1х2х3 = 101 возможен сбой схемы (рис. 1.11).

Согласно логике работы схемы рис. 1.11 при изменении входной комбинации 111—>101 должна сохраняться на выходе логическая единица. Однако ввиду наличия задержек в логических элементах НЕ (DD2) tзад2= t2 — t1 ; И (DD3) t3aд3 = t2- t1; И (DD4) tзad4 = t3 - t2 на выходе y1 в течение короткого интервала времени (t3 – t2) возникает ложный логический ноль. Это происходит из-за разности задержек распространения сигнала х2 к выходу у1 по маршрутам (DD2-DD4-DD5); (DD3-DD5).

Для исключения возможных сбоев в работе цифровых устройств используются два пути:

1. Введение дополнительных элементов, задерживающих сигнал.

2. Запрещение работы схемы (либо ее части) на время переходных процессов.

Таким образом, в задаче анализа проводится учет отличия характеристик реальных цифровых устройств от идеализированных моделей, а также определение необходимых коррекций в схеме.

Дата добавления: 2015-09-29; просмотров: 3901;