ОСНОВЫ ЭЛЕМЕНТНОЙ БАЗЫ ЦИФРОВЫХ АВТОМАТОВ

К основным логическим элементам современных вычислительных устройств относятся электронные схемы, реализующие операции И, ИЛИ, НЕ, И—НЕ, ИЛИ—НЕ и другие, а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера.

Входные и выходные сигналы, соответствующие двум логическим состояниям в логических элементах — 1 и 0 — имеют один из двух установленных уровней напряжения. Например, +5 В и 0 В.

Высокий уровень обычно соответствует значению «истина» («1»), а низкий — значению «ложь» («0»).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию.

Работу логических элементов описывают с помощью таблиц истинности.

Таблица истинности — табличное представление вычислительной (логической) схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

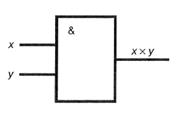

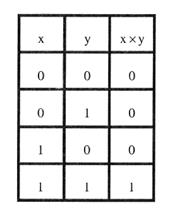

Схема И. Эта схема реализует конъюнкцию двух или более логических значений.

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Операция конъюнкции на структурных схемах обозначается знаком & (читается как амперсэнд), являющимся сокращенной записью английского слова and.

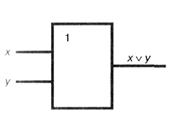

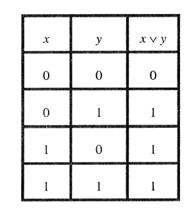

Схема ИЛИ. Эта схема реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы ИЛИ будет единица, на ее выходе также будет единица.

Знак 1 на схеме соответствует обозначению, т. е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1.

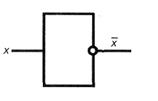

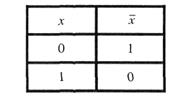

Схема НЕ. Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом х этой схемы и выходом z можно записать соотношением z = х, х, где х читается как «не х» или «инверсия х».

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0.

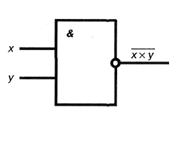

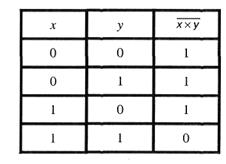

Схема И—НЕ. Схема состоит из элемента И и инвертора и осуществляет отрицание результата схемы И. Связь между выходом Z и входами х и у схемы записывают следующим образом:  , где

, где  , читается как «инверсия х и у».

, читается как «инверсия х и у».

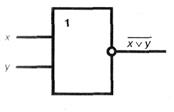

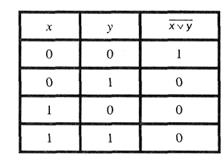

Схема ИЛИ—НЕ. Схема состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ. Связь между выходом z и входами х и у схемы записывают следующим образом:  , где

, где  , читается как «инверсия х и у».

, читается как «инверсия х и у».

Триггер — (от англ. trigger — защелка, спусковой крючок) электронное устройство с двумя устойчивыми состояниями равновесия, чередующимися под воздействием внешних сигналов, предназначенных для записи и хранения 1 бита данных.

Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает «хлопанье».

В отличие от рассмотренных выше логических схем, триггеры — это логические устройства с памятью. Выходные сигналы триггеров в общем случае зависят не только от их входных сигналов, действующих в настоящий момент, но и от сигналов, действовавших на входы до этого.

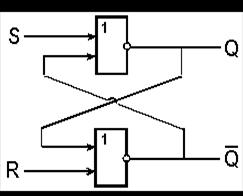

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс).

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс).

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал

, причем выходной сигнал  является логическим отрицанием сигнала Q.

является логическим отрицанием сигнала Q.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов.

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

| S | R | Q |

| |

| запрещено | ||||

| режим очистки | ||||

| режим записи | ||||

| хранение бита |

Реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

Если на входы триггера подать S="1", R="0", то на выходе Q верхнего вентиля появится "0". После этого на входах нижнего вентиля окажется R="0", Q="0" и выход  станет равным "1".

станет равным "1".

Точно так же при подаче "0" на вход S и "1" на вход R на выходе  появится "0", а на Q — "1".

появится "0", а на Q — "1".

Если на входы R и S подана логическая "1", то состояние Q и  не меняется.

не меняется.

Подача на оба входа R и S логического "0" может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел.

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1) цифра ai первого слагаемого;

2) цифра bi второго слагаемого;

3) перенос pi–1 из младшего разряда.

В результате сложения получаются две цифры:

1) цифра ci для суммы;

2) перенос pi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами.

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) может иметь вид:

Лекция 5.

Дата добавления: 2015-08-08; просмотров: 1804;