Основные электрические параметры микросхем

Цифровые микросхемы развивались в следующей последовательности: резистивно-транзисторная логика (РТЛ), диодно-транзисторная логика (ДТЛ), транзисторно-транзисторная логика (ТТЛ), эмиттерно-связанная логика (ЭСЛ), транзисторно-транзисторная логика с диодами Шотки (ТТЛШ), интегрально-инжекционная логика (И2Л). В этих определениях слово “логика” подразумевает понятие “электронный ключ”.

Все перечисленные выше логические микросхемы выполнены на базе биполярных транзисторов. Наряду с ними широкое распространение получили цифровые микросхемы на МОП - структурах (на транзисторах p- и n-типов с обогащенным каналом, КМОП - схемы на дополняющих транзисторах). Серии РТЛ, РЕТЛ промышленностью в настоящее время не выпускаются, но еще используются только для комплектации серийной РЭА. Наиболее широкое распространение в современной аппаратуре получили серии микросхем ТТЛШ, ЭСЛ и схемы на КМОП-структурах, так как они отличаются более высоким уровнем интеграции и обладают большим функциональным разнообразием.

Можно выделить три этапа развития микросхем, входящих в состав стандартных серий для создания цифровых устройств различного назначения.

I этап (1969 - 1975 гг.). В состав стандартных серий входили микросхемы малой степени интеграции, выполняющие простейшие логические функции, например серия К155.

II этап (1976 - 1980 гг.). Появились серии с улучшенными характеристиками, такие как 531, 555, 500, К561, К1561 и другие, что привело к ограниченному применению серий 131, 158, 137, 187.

III этап (1981 - 1987 гг.). Разработка микросхем большой степени интеграции, микропроцессорных комплектов, запоминающих устройств, полузаказных БИС на основе матричных кристаллов.

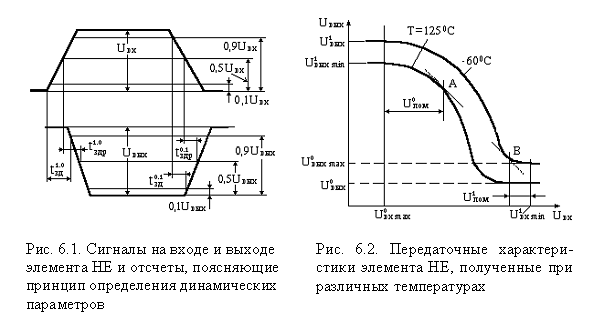

Параметры микросхем конкретной серии в основном определяются параметрами базовых элементов логики. К основным параметрам относятся: быстродействие; потребляемая мощность (Рпот); помехоустойчивость Uпом; коэффициент разветвления по выходу (нагрузочная способность) Краз; коэффициент объединения по входу Коб. Быстродействие определяется динамическими параметрами цифровых микросхем, к которым относятся: t1,0 - время перехода сигнала на выходе микросхемы из состояния логической “1” в состояние логического “0”; t0,1 -время перехода из состояния низкого уровня в состояние высокого уровня; t1,0здр - время задержки распространения при включении; t1,0зд -время задержки включения; t0,1здр - время задержки распространения при выключении; t0,1зд - время задержки выключения; tздрср - среднее время задержки распространения сигнала; fр - рабочая частота. Среднее время задержки распространения tэдрср = 0,5(t1,0здр + t0,1здр) является усредненным параметром быстродействия микросхемы, используемым при расчете временных характеристик последовательно включенных цифровых микросхем. На рис. 6.1 показаны уровни отсчета, определяющие параметры быстродействия цифровых микросхем.

В зависимости от технологии микросхем, мощности, потребляемые при состоянии логического нуля и при состоянии логической “1” могут отличаться. Поэтому, мощность, потребляемая логическими элементами в динамическом режиме, определяется как

Рпотср = 0,5(Р0пот + Р1пот),

где Р0пот - мощность, потребляемая микросхемой при состоянии выхода “0”, Р1пот - мощность при выходном состоянии “1”.

Некоторые логические элементы кроме статической средней мощности характеризуются мощностью, потребляемой на максимальной частоте переключения, когда токи в цепях питания возрастают во много раз. К таким схемам относятся микросхемы КМОП технологии, которые потребляют микроамперы, если нет переключающих сигналов.

Допустимый уровень напряжения помехи логического элемента определяется уровнем входного напряжения, при котором еще не происходит ложное срабатывание микросхемы.

В статическом режиме помехоустойчивость определяется по низкому U0пом и высокому U1пом уровням. Значения U0пом и U1пом определяют с помощью передаточных характеристик (рис. 6.2.). Как следует из рис. 6.2, напряжение помехи по высокому уровню определяется как разность минимального напряжения высокого уровня U1вхmin и напряжения в точке перегиба верхней кривой (точка В). Параметр U0пом определяется как разность напряжения низкого уровня U0вхmax.

Помехоустойчивость в динамическом режиме зависит от длительности, амплитуды и формы импульса помехи, а также от запаса статической помехоустойчивости и скорости переключения логического элемента.

Коэффициент разветвления по выходу Краз определяет число входов аналогичных элементов, которое может быть подключено к выходу предыдущего элемента без нарушения его работоспособности. С увеличением нагрузочной способности расширяются возможности применения цифровых микросхем и уменьшается число корпусов в разрабатываемом устройстве. Однако при этом ухудшаются помехоустойчивость и быстродействие микросхемы и возрастает потребляемая мощность.

Коэффициент объединения по входу Коб определяет максимальное число входов цифровых микросхем.

Вопросы и задания

1.1. Какие виды сигналов используются в информационных системах?

1.2. Числа какой системы счисления используются в вычислительной технике?

1.3. Как связаны законы алгебры логики и работа элементов цифровой логики?

1.4. Как понять смысл “задания” функций АЛ?

1.5. Какие законы АЛ отражают суть понятий о базисе?

1.6. Нарисуйте схему цифрового логического замка в базисе И-НЕ, в которой сигнал на выходе замка принимает значение лог. “1” (Z= 1) при выполнении условия Х1=0; Х2=1; Х3=1; X4=1; X5=0 X6=1.

Вопросы и задания

2.1. Объясните причины возникновения гонок в комбинационных устройствах.

2.2. Синтезируйте схему преобразователя кода для 9 и 13 сегментных индикаторов.

2.3. Можно ли построить полный дешифратор на элементах базиса ИЛИ-НЕ? Составьте аналитическое выражение (функции), описывающее работу дешифратора в базисе И-НЕ.

2.4. Синтезируйте схему мультиплексора 2-1, и на базе синтезированного мультиплексора постройте схему сумматора по модулю два (исключительное ИЛИ).

2.5. Определите информационную площадь (SПЛМ) ПЛМ, ПЗУ при произвольных значениях количества информационных входов. Докажите, что SПЗУ > SПЛМ.

2.6. Нарисуйте схему фрагмента КУ, приведенного на рис. 2.32, в базисе ИЛИ-НЕ.

2.7. Нарисуйте схему четырёхразрядного полного дешифратора на базе дешифраторов 2-4. Базовые дешифраторы имеют один дополнительный вход стробирования.

Вопросы и задания

3.1. Опишите работу RS - триггера, управляемого активным низким уровнем. Сравните временные диаграммы работы асинхронного и синхронного RS - триггеров.

3.2. Почему JK- триггер можно построить только на базе двухступенчатых RS либо D - триггеров?

3.3. Попробуйте синтезировать JK- триггер из D- и Т - триггеров.

3.4. Постройте временные диаграммы четырёхразрядного регис-тра сдвига, работающего в режиме деления чисел (в двоичном коде) и объясните принцип его работы.

3.5. Синтезируйте счетчики обратного счета с Ксч =7 на D - и JK - триггерах.

3.6. Нарисуйте схему делителя частоты с Кдел = 171. В схеме можно использовать ИМС КР1554ИЕ23 (см. приложение, стр. 132) и элементы логики этой же серии.

Вопросы и задания

4.1. Будет ли работать формирователь коротких импульсов, если число элементов задержки четное? Если да, то как будет выглядеть сформированный импульс?

4.2. Попробуйте перечислить функциональные отличия схемы формирователя импульса с удлиняющей RC цепью от схемы с дифференцирующей цепью.

4.3. Какую роль играет в триггерах Шмитта положительная обратная связь?

4.4. На рисунке 4.7 приведены схемы формирователей импульсов от механических контактов. Какие дополнительные схемы и способы можете предложить для формирования импульсов от механических контактов?

4.5. Почему значение частоты генераторов импульсов, построенных с использованием времязадающих RC цепей определяется только приближенными соотношениями (fи @ 1/ 2RC)?

4.6. Можно ли использовать ГЛИН в качестве автогенератора импульсов?

4.7. Можно ли использовать цифровые элементы логики при обработке аналоговых сигналов?

4.8. Какие типы ИМС целесообразнее применять в различных узлах формирователей импульсов?

Вопросы и задания

5.1. Поясните физический смысл основных параметров ЦАП и АЦП. От каких внешних и внутренних факторов они зависят?

5.2. Какие физические ограничения препятствуют бесконечному уменьшению шага квантования в ЦАП и АЦП?

5.3. Нарисуйте схему простейшего 5-ти разрядного ЦАП с резисторной матрицей R - Rn.

5.4. Каким быстродействием должен обладать АЦП для удовлетворительного преобразования в цифровую форму сигналов речи с верхней частотой до 5 кГц?

5.5. Дайте сравнительные характеристики всем типам АЦП. Укажите, какой тип АЦП может преобразовать телевизионные сигналы.

5.6. Нарисуйте схему простейшего АЦП последовательно счета с использованием ЦАП.

5.7. Нарисуйте схемы функциональных ЦАП и расскажите их принцип действия.

Дата добавления: 2015-07-18; просмотров: 2844;