Из-за разницы в площадях переходов имеет место неравенство

Iэо<< Iко,

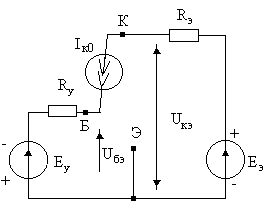

что позволяет для расчетов в режиме отсечки использовать упрощенную модель (рис. 4.19).

Напряжение коллектор-эмиттер запертого транзистора из-за малой величины Iк0 равно

U=Еэ - Rэ Iк0» Еэ.

Рис. 4.19. Упрощенная модель транзистора в режиме отсечки

Рис. 4.19. Упрощенная модель транзистора в режиме отсечки

|

Условием запирания является неравенство (для п-р-п-транзистора) Uбэ<0), ½Uбэ½>>j т, которое сводится к неравенству

½Еу½>IкоRу. (4.11)

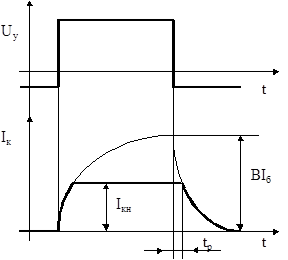

Рис. 4.20. Задержка выключения транзи- стора на время рассасывания избыточных носителей в базе tp

Рис. 4.20. Задержка выключения транзи- стора на время рассасывания избыточных носителей в базе tp

|

Быстродействие ключа является важнейшей его характеристикой, определяющей скорость обработки двоичной информации в цифровой электронике и значение динамических потерь в силовой электронике. Хотя причины инерционности транзистора ключевом и активном режимах одинаковы (паразитные емкости переходов), ключевой режим обладает специфическими характеристиками переходного процесса.

Из-за того, что при насыщении заряды в базу поступают как со стороны коллектора, так и со стороны эмиттера, а при запирании этот заряд “рассасывается” только эмиттерным переходом, в переходном процессе насыщенного ключа имеется характерный отрезок времени, в течение которого транзистор теряет управляемость (время рассасывания tр) (рис. 4.20). Длительность времени рассасывания существенно ограничивает скорость переключения цифровых ключей и тем больше, чем сильнее выполняется условие насыщения (4.10). Поэтому в цифровой электронике используются различные способы, предотвращающие глубокое насыщение.

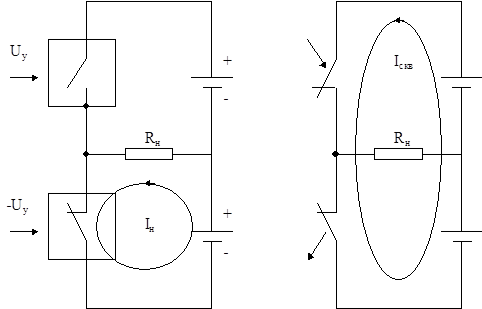

В силовой электронике при построении преобразователей используются схемы последовательного соединения двух ключей, находящихся в противоположных состояниях. Однако за счет процесса рассасывания создается ситуация, когда ранее запертый транзистор уже открылся, а ранее открытый и насыщенный еще находится в стадии рассасывания. В результате через оба транзистора, оказавшиеся одновременно открытыми на некоторое время, течет ничем не ограниченный так называемый сквозной ток, который существенно ухудшает КПД преобразователя и может вывести активные элементы из строя (рис. 4.21).

а) б)

Рис. 4.21. Статическое состояние ключевых элементов (а), состояние при выходе из насыщения ранее открытого транзистора (б)

а) б)

Рис. 4.21. Статическое состояние ключевых элементов (а), состояние при выходе из насыщения ранее открытого транзистора (б)

|

На практике для исключения эффекта сквозного тока используют временную задержку открывания ранее запертого транзистора на момент времени рассасывания насыщенного транзистора.

Дата добавления: 2015-06-17; просмотров: 904;