Структура микропроцессорного устройства (системы)

Структура процессора микро-ЭВМ строится с учетом стремления разработчиков МП объединить на кристалле БИС максимально-возможное количество функций при ограниченном числе внешних контактов корпуса БИС. Реализовать принципиальную схему обычного процессора в виде одной или нескольких БИС практически невозможно. Поэтому необходимо изменять структуру процессора так, чтобы полная принципиальная схема или ее части имели количество элементов и связей, совместимое с возможностями БИС. При этом микропроцессоры приобретают внутреннюю магистральную структуру, т. е. в них к единой внутренней информационной магистрали подключаются все основные функциональные блоки (арифметико-логический, рабочих регистров, стека, прерываний, интерфейса, управления и синхронизации и др.). Наиболее распространенной является схема микропроцессорной системы, имеющая две или три шины, по которым в зависимости от сигналов управления передается информация от тех или иных узлов микропроцессорной системы. Такая организация требует минимального числа внешних контактов, однако обмен информацией между узлами и блоками микропроцессорной системы должен осуществляться в определенной последовательности.

На рисунке 1.2. приведена стандартная структура микропроцессорной системы, предназначенной для обработки данных или управления некоторым процессом. Примерно такую же структуру имеют микро-ЭВМ широкого назначения.

Рисунок 1.2. Структура микропроцессорной системы или микро-ЭВМ

Центральное место в этой структуре занимает микропроцессор, который подобно процессору обычных ЭВМ, выполняет арифметические и логические операции над данными, осуществляет программное управление процессом обработки информации, организует взаимодействие всех устройств, входящих в систему. Работа микропроцессора происходит под воздействием сигналов схемы синхронизации часто выполненной в виде отдельной БИС.

Для микропроцессоров характерна трехшинная структура (рис.1.2), содержащая шину адреса (ША), двунаправленную шину данных (ШД) и шину управления (ШУ). Шина данных осуществляет передачу информации как от процессора к памяти и периферийным устройствам, так и для передачи в обратном направлении.

Память представляет собой единую совокупность ячеек для хранения данных. Каждой ячейке присвоен адрес. Шина для передачи адресов называется шиной адреса и является выходной по отношению к процессору. Если обозначить разрядность шины адреса n, то наибольшее число адресов, к которым можно обращаться по этой шине, равно  .

.

В интерфейсе периферийного устройства имеются области, предназначенные для ввода и вывода данных. Первая из них называется портом ввода, вторая – портом вывода. Для обращения к портам ввода/вывода существуют два способа:

· изолированный ввод/вывод;

· ввод/вывод с отображением на память.

При первом способе память и порты ввода/вывода используются как различные устройства. Порту ввода и порту вывода присваиваются номера, не зависящие от адреса памяти. Для указания номера порта также используются адресные сигналы. Однако, например, если нет необходимости использовать все 16 бит адреса, для этой цели можно взять только восемь младших разрядов. Во втором способе память и порты ввода/вывода используются как одинаковые устройства. Для этого часть адресов, не распределенная в памяти, приписывается портам ввода/вывода. Поэтому эти порты можно считать частью памяти. Для их адресации используются полные адресные сигналы.

Шина управления служит для передачи различных управляющих сигналов. Конкретный состав этих сигналов зависит от типа процессора. Основными сигналами, передаваемыми по этой шине, являются сигналы управления записью/чтением из памяти и сигналы управления вводом/выводом данных из соответствующего порта. Причем, когда применяется способ изолированного ввода/вывода, передаются четыре управляющих сигнала:

1.  - чтение данных из памяти;

- чтение данных из памяти;

2.  - запись данных в память;

- запись данных в память;

3.  - ввод данных из порта ввода;

- ввод данных из порта ввода;

4.  - вывод данных в порт вывода.

- вывод данных в порт вывода.

В случае ввода/вывода с отображением адресов на память можно использовать два сигнала управления  и

и  .

.

Временная диаграмма работы стандартной шины представлена на рисунке 1.3.

Рисунок 1.3. Временная диаграмма

Время осуществления однократного считывания, записи, ввода или вывода данных называется циклом шины. Процессор управляет работой шины синхронно с входной тактовой частотой. В рассматриваемом примере, каждый цикл шины содержит четыре периода тактовой частоты. Сигналы управления, как правило, являются активно низкими (т.е. наличие низкого уровня разрешает работу того или иного устройства).

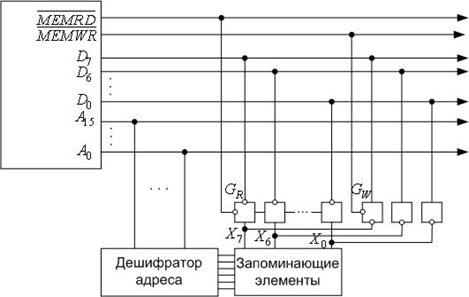

Рассмотрим работу шины в цикле считывания данных из памяти (рисунок 1.4).

Рисунок 1.4. Работа шины в цикле считывания данных из памяти

В начале цикла процессор вырабатывает адресный сигнал, который дешифрируется дешифратором адреса, и указанная ячейка памяти подключается к линиям  . В первой половине такта

. В первой половине такта  сигнал

сигнал  переходит на низкий уровень, а во второй половине такта

переходит на низкий уровень, а во второй половине такта  он возвращается на высокий уровень. Низкий уровень этого сигнала переводит вентиль

он возвращается на высокий уровень. Низкий уровень этого сигнала переводит вентиль  из третьего состояния в активное состояние и сигналы

из третьего состояния в активное состояние и сигналы  поступают на шину данных. По заднему фронту положительного импульса такта

поступают на шину данных. По заднему фронту положительного импульса такта  содержимое шины данных записывается в процессор. Аналогичным образом шина работает в цикле записи данных в память и циклах ввода/вывода информации из портов ввода/вывода. Следует отметить, что порт вывода представляет собой регистр, запись информации в который происходит по тактовому сигналу C. Этот сигнал обычно вырабатывается из младших разрядов адресных сигналов и тактовых сигналов процессора.

содержимое шины данных записывается в процессор. Аналогичным образом шина работает в цикле записи данных в память и циклах ввода/вывода информации из портов ввода/вывода. Следует отметить, что порт вывода представляет собой регистр, запись информации в который происходит по тактовому сигналу C. Этот сигнал обычно вырабатывается из младших разрядов адресных сигналов и тактовых сигналов процессора.

В рассмотренном примере работы шины, данные никогда одновременно не поступают из/в памяти и портов ввода/вывода. Это обстоятельство позволяет осуществить управление работой шины тремя сигналами  ,

,  ,

,  . Сигнал

. Сигнал  указывает какое из устройств (память или порт ввода/вывода) подключено к шине данных. Сигналы

указывает какое из устройств (память или порт ввода/вывода) подключено к шине данных. Сигналы  и

и  указывают, происходит ли чтение данных в процессор или запись данных в память или порт ввода/вывода.

указывают, происходит ли чтение данных в процессор или запись данных в память или порт ввода/вывода.

В рассмотренной выше стандартной временной диаграмме работы шины временные соотношения в циклах записи/считывания полностью задаются процессором. При такой временной диаграмме работы память и порты ввода/вывода должны постоянно находиться в рабочем состоянии, что нежелательно. Для исключения указанной ситуации в систему вводятся дополнительные сигналы управления, позволяющие произвольно увеличивать длительность циклов записи/чтения. Обычно такие сигналы называются  (готовность),

(готовность),  (ожидание), TRANSFER ACNOWLEDGE (подтверждение передачи). Эти сигналы подтверждают окончание цикла.

(ожидание), TRANSFER ACNOWLEDGE (подтверждение передачи). Эти сигналы подтверждают окончание цикла.

Дата добавления: 2015-04-25; просмотров: 1112;