Особенности архитектуры процессоров семейства DSP56800

Семейство DSP56800 - это первая DSP-архитектура от Freescale, разработанная "с нуля" и обеспечивающая интеграцию мощной DSP-архитектуры с возможностями микроконтроллеров. При высокой производительности микропроцессоры этого семейства отличает низкая стоимость. Motorola занимает на рынке уникальную позицию, которая позволяет ей предоставлять как микроконтроллеры (MCUs), так и цифровые сигнальные процессоры (DSPs) путем программно-совместимого перехода и отвечать потребностям заказчиков по мере роста требований к эксплуатационным показателям. Архитектура семейства DSP56800 объединяет традиционные функции управления MCU с эффективностью DSP. Это было сделано во первых для того, чтобы позволить управляемым электроникой моторным системам выполнять усовершенствованные алгоритмы, предоставляя точность, улучшенный КПД и надежность, сейчас такой принцип нашел применение и в целом ряде других приложений.

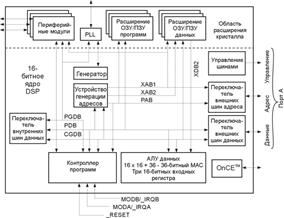

Микропроцессоры данного семейства являются полностью 16-разрядными с длиной команд процессора в 16 бит, что обуславливает их несовместимость с другими семействами. Обобщенная структурная схема процессора семейства DSP568xx представлена на рис.1.

Рис. 1. Структурная схема микропроцессора семейства DSP568xx

DSP56824 имеет ОЗУ программ и данных 13.5Кх16 и возможность адресовать до 64Кх16 внешней памяти данных Х и 64Кх16 внешней памяти программ. В его структуре можно выделить: 16 линий GPIO, последовательные интерфейсы SPI и SSI, порт эмуляции OnCE с 8-и уровневым FIFO-буфером, интерфейс внешней памяти (порт А), таймеры прерывания реального времени. При частоте 70Гц процессор достигает производительности 35 MIPS.

Дата добавления: 2014-12-21; просмотров: 1001;