ЛОГИКА ЦАП

Самые ранние монолитные ЦАП содержали небольшую, если таковая вообще была, логическую схему, и параллельные данные должны были накапливаться на цифровом входе, чтобы сформировать аналоговый выходной сигнал. Сегодня почти все ЦАП имеют входные элементы фиксации состояния (триггеры, latches) и записывают данные только один раз, без процедуры накопления.

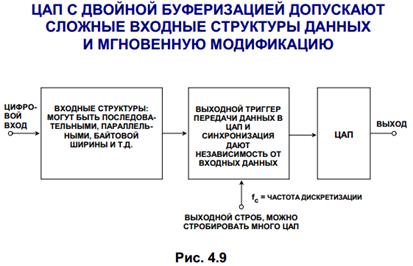

Существует многочисленные разновидности входных структур ЦАП, которые не будут обсуждаться здесь, но в большинстве своем сегодня преобладают устройства "с двойной буферизацией". ЦАП с двойной буферизацией имеет два набора триггеров. Данные первоначально хранятся (защелкиваются) в первом наборе и впоследствии передаются на второй, как показано на рис.4.9.

Существует три причины, по которым это компоновка представляется выгодной:

1) Первая – это то, что она позволяет вводить данные в ЦАП многими различными способами. ЦАП без триггера или с одним триггером должен быть заполнен сразу по всем разрядам, так как иначе его выходной сигнал в течение загрузки может сильно отличаться от тех значений, которые были до преобразования и появятся после преобразования. С другой стороны, ЦАП с двойной буферизацией может быть загружен параллельными данными, последовательными данными, 4-разрядными или 8-разрядными словами или чем-то подобным, и выход его остается неизменным до тех пор, пока новые данные полностью не загрузятся, и на ЦАП не поступит команда модификации выходных данных.

2) Второй особенностью входной структуры этого типа является то, что генератор тактовых импульсов может работать на фиксированной частоте (частоте дискретизации сигнала), в то время как входной триггер может быть загружен асинхронно. Это выгодно в приложениях, где требуется восстановление сигнала в реальном масштабе времени.

3) Третья выгодная особенность структуры с двойной буферизацией состоит в том, что несколько ЦАП могут выполнять преобразования одновременно. Данные загружаются в первый набор каждого ЦАП, и когда преобразования завершатся, выходные буферы всех ЦАП модифицируются одновременно.

Наиболее ранние однокристальные ЦАП с высоким разрешением имели параллельные порты данных для подключения к параллельным шинам передачи данных и дешифраторам адреса. Они отображались в адресном пространстве микропроцессора в виде очень маленьких блоков памяти только для записи (некоторые ЦАП обеспечивали не только запись, но и чтение содержимого – это было выгодно для некоторых приложений, но не очень распространено). ЦАП, подключаемые к параллельной шине данных, уязвимы из-за емкостной связи шины с аналоговом выходом. Поэтому многие ЦАП сегодня имеют последовательные структуры ввода данных.

Другое достижение в технологии ЦАП заключается в возможности исполнения нескольких ЦАП на одном кристалле, что представляется полезным с точки зрения сокращения размеров печатной платы (PCB) и затрат на сборку.

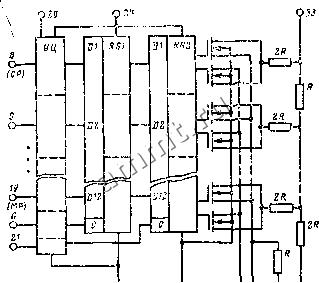

Микросхемы умножающего ЦАП К572ПА2 (А, Б, В) (рисунок 2) или КР572ПА2 (А, Б, В), как и ИС К572ПА1, являются универсальными структурными звеньями для построения микроэлектронных ЦАП, АЦП и управляемых цифровым кодом делителей тока. Они предназначены для преобразования 12-разрядного прямого двоичного кода на цифровых входах в ток на аналоговом выходе, который пропорционален значениям кода и (или) опорного напряжения.

Нумерация и назначение выводов (для ИС КР572ПА2 в скобках): 2(32) – аналоговый выход 2; 4(33) – аналоговая земля; 6(34) – вход регистра 1; 8(35) – 19(6) – цифровые входы 1 – 12; 21(8) – вход регистра 2; 22(9) – цифровая земля; 24(10) – напряжение источника питания U СС2; 30(13) – вывод конечного резистора матрицы; 38(27) – опорное напряжение U REF; 47(28) – вывод резистора обратной связи; 48(31) – аналоговый выход 1; 1, 3, 5, 7, 23, 25 – 29, 31 – 37, 39 – 46 – незадействованные выводы.

Дата добавления: 2014-12-21; просмотров: 1467;