Базовая организация ВЕ48

Среди однокристальных МК отечественного производства следует отметить БИС К1816ВЕ48(ВЕ48)—базовый прибор МПК. Пока в составе комплекта пять элементов [17, 21]: К1816ВЕ48, К1816ВЕ49, К1816ВЕ48, К1816ВЕ35, К1816ВЕ39, отличающиеся функциональными возможностями памяти программ. В К1816ВЕ48/ВЕ49 используется маской программируемое ПЗУ, в К1816ВЕ48—УСППЗУ, а К1816ВЕ35/ВЕ39 представляет модель без ПЗУ.

Семейство ВЕ48 является аналогом семейства iMCS-48. В основу его архитектуры положена организация гарвардского типа, ориентированная на интенсивное использование двух банков рабочих регистров и операций ВВ.

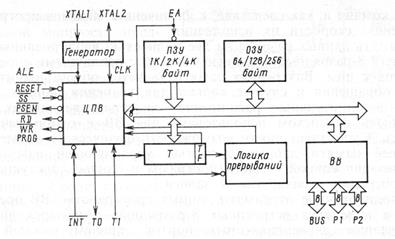

Представленная на рис. 4.2 структурная схема однокристальной вычислительной системы ВЕ48/ВЕ49/ВЕ50 содержит 8-разрядный ЦП, (ЦП48), управляющее ПЗУ, внутреннее ОЗУ 24 линии прямого ВВ, три тестируемых входа, 8-разрядный таймер/счетчик Т и логику одноуровневой системы прерываний с двумя источниками запросов. Благодаря предусмотренным в схеме средствам внешнего расширения возможны вынос за пределы кристалла и (или) прямое увеличение размеров управляющей памяти до 4К байт, добавление дополнительного блока внешнего ОЗУ данных в 256 байт и 16 линий ВВ. Полученная в итоге система называется расширенной. При использовании в дальнейшем стандартной техники переключения банков внешние средства могут быть доведены до требуемого объема сверх норм, предусмотренных расширенной организацией.

Рис. 4.2. Схема однокристальной вычислительной системы BE48/BE49/BE50

Гарвардский принцип организации вычислительной среды предусматривает разделение памяти для хранения программ и данных. Управляющая память допускает только операцию считывания, память данных доступна и для записи, и для считывания.

Изоляция пространств памяти программ и данных позволила минимизировать длину машинных команд, что было очень важным в первых МК с ограниченными объемами ПЗУ. Как показывает практика, объем программного обеспечения МК обычно намного превышает объем памяти, отводимой под данные. Если бы в МК использовалась свойственная многокристальным микроЭВМ архитектура неймановского типа, то большая часть совмещенной памяти программ и данных была бы занята кодами команд. Вместе с тем основные механизмы адресации связаны исключительно с памятью данных. Их потенциальная ориентация на большой объем совмещенной памяти и реальное применение в рамках небольшой свободной от программ области привели бы к неэффективному использованию адресной части команд и, как следствие, к увеличению объемов программ и снижению скорости их исполнения.

Память данных разбита на две полностью изолированные друг от друга 8-разрядные линейные области с различными способами доступа к ним. Внутренняя память является областью интенсивного обращения и служит только для хранения данных, внешняя—дополнительным расширением пространства данных и может быть с успехом использована для ВВ с отображением в память. Существует также возможность физического совмещения внешней памяти данных с частью управляющей памяти для организации единой области программ и данных, доступной как для операции чтения, так и записи.

Изолированное от памяти данных пространство ВВ представлено в виде трех встроенных 8-разрядных и четырех внешних 4-разрядных двунаправленных портов, причем каждый порт адресуется независимо от других. Имеются также три отдельные входные линии, состояние которых может быть проверено специальными командами условного перехода. Средства поддержки режима реального времени представлены двухрежимным 8-разрядным таймером/счетчиком и одноуровневой системой прерываний с двумя источниками запросов. Расширение специальных аппаратных функций может быть выполнено с помощью стандартных периферийных БИС из семейства ВМ80/ВМ85А, области ВВ которых отображаются на внешнюю память данных ВЕ48.

Дата добавления: 2019-02-07; просмотров: 672;