Набор регистров ВЕ48

Набор доступных программисту регистров ЦП ВЕ48 представлен на рис. 4.3. В состав набора входит 8-разрядный аккумулятор А, который выполняет свои обычные функции промежуточного хранения данных. При выполнении ряда операций А является как источником операнда, так и приемником результата операции. Ориентация на аккумулятор, который подразумевает неявную адресацию в большинстве команд различного типа, позволила существенно сократить длину программ и, следовательно, более экономно использовать объем управляющей памяти МС.

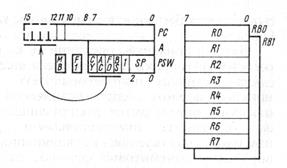

Рис. 4.3. Набор регистров центрального процессора BE48

Среди типовых признаков результата операции—только два: CY—основной перенос из старшего разряда и АС—формируемый командами сложения и используемый командой DAA дополнительный перенос из младшей тетрады в старшую. Если CY представляет основное средство для организации многобайтовых операций, то АС (по аналогии с архитектурой ВМ80) поддерживает десятичную арифметику в 2/10-коде упакованного формата. Оба признака входят в состав 8-разрядного слова состояния программы PSW.

Для повышения вычислительной мощности предназначен набор из восьми рабочих регистров R0—R7 по 8 разрядов каждый. Регистры используются для временного хранения данных, что уменьшает общее число обращений к памяти МС, связанное с дополнительными затратами на ее адресацию. Среди рабочих регистров следует выделить два первых R0 и R1, которые несут дополнительную функциональную нагрузку по адресации памяти данных. По этой причине их называют адресными регистрами или регистрами-указателями.

В общем случае архитектура ВЕ48 содержит два набора или банка рабочих регистров RB0 (Register Bank 0) и RB1, однако в каждый момент времени пользователю доступен только один из них. Выбор банка осуществляется с помощью одноразрядного указателя BS (Bank Select), входящего в состав PSW. Доступ к RB0 организуется при BS = 0, в противном случае разрешается доступ ко второму банку RB1. При начальной установке МК указатель BS сбрасывается, обеспечивая автоматический выбор RB0.

Средства переключения банков рабочих регистров дают возможность быстро менять текущий контекст процессора МС. Так, если RB0 зарезервировать под фоновую задачу, a RB1 применять для реализации процедур обслуживания прерываний, то можно существенно уменьшить время отклика МК на асинхронные запросы внешней среды, тем самым повысив скоростные характеристики прикладной системы. Одновременное использование четырех адресных регистров R0, R1, R0' и R1' обеспечивает быстрый доступ к четырем независимым структурам данных.

Счетчик команд PC имеет длину 12 разрядов, что позволяет обращаться к управляющей памяти емкостью 4К байт. Управляющая память разбита на два независимых банка МВ0 (Memory Bank 0) и МВ1 по 2К байт каждый, которые адресуются с помощью старшего разряда PC. Данный разряд программного счетчика отделен от 11 младших и никогда не изменяет своего значения при последовательной выборке команд. Следовательно, непрерывный переход из одного банка управляющей памяти в другой невозможен, поэтому используются команды передачи управления, которые содержат прямой 11-разрядный адрес внутри банка. Состояние старшего разряда PC определяется содержимым флажка MB (Memory Bank), управляемого индивидуально с помощью отдельных команд выбора RB0. При инициализации МК флажок MB и программный счетчик сбрасываются, обеспечивая обращение к первой команде нулевого банка.

Флажки-признаки операций CY и АС, а также указатель регистрового банка BS упакованы в старшей тетраде 8-разрядного слова состояния программы PSW. Четвертый разряд тетрады занимает флажок общего назначения F0, функциональный смысл которого определяется программистом. Существует ряд команд по его очистке, инвертированию и тестированию с условной передачей управления, позволяющих реализовать эффективную обработку однобитовых данных, различные флажковые и семафорные процедуры. Младшая тетрада PSW занята трехразрядным указателем стека SP.

Наряду с F0 имеется еще один флажок пользователя общего назначения F1. Его функции аналогичны F0, однако, в отличие от последнего, F1, как и флажок MB, не входит в состав PSW и располагается как независимый программно-доступный разряд. Это обстоятельство приводит к невозможности эффективной смены их состояний с возвратом в исходное при очередном переключении контекстов ЦП и ограничивает функциональные возможности F1 по сравнению с F0.

Входящий в состав PSW трехразрядный указатель стека обеспечивает организацию системного стека из восьми двухбайтовых ячеек. Стек служит для промежуточного хранения старшей тетрады PSW и определяемых текущим состоянием PC адресов возврата при обработке прерываний и вызовах подпрограмм. Набор признаков CY, AC, F0, BS совместно с 12-разрядным PC образуют двухбайтовый объект, автоматически загружаемый в стек или выбираемый обратно при очередной операции над ним. При этом старшее 4-разрядное поле объекта состоит из признаков. В отличие от архитектуры ВМ80 стек ВЕ48 заполняется в сторону увеличения адресов и указывает на его первую свободную ячейку. При ограниченной глубине стека допускается до восьми уровней вложения, в противном случае возникает переполнение стека с переходом через границу на его начало. Переход через границу в обратном направлении возможен при попытке получить данные из уже пустого стека. При инициализации SP устанавливается в 0.

Дата добавления: 2019-02-07; просмотров: 637;