Лекция 21. Регистры

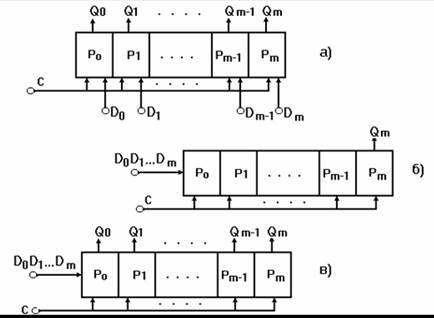

Наиболее распространенным узлом цифровой техники и устройств автоматики являются регистры. Регистры строятся на базе синхронных одно- и двухступенчатых RS и D-триггеров. Регистры могут быть реализованы также на базе JK -триггеров. По способу приема и выдачи информации регистры делятся на следующие группы: с параллельным приемом и выдачей (рис. 1 а); с последовательным приемом и выдачей (рис. 1 б); с последовательным приемом и параллельной выдачей (рис. 1 в); с параллельным приемом и последовательной выдачей (рис. 1 г); комбинированные, с различными способами приема и выдачи (рис. 1 д) и реверсивные.

Регистры хранения (памяти). Регистры с параллельным приемом и выдачей информации служат для хранения информации и называются регистрами памяти или хранения. Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0 . . . Dm новой цифровой комбинации (информации) при поступлении синхросигнала (синхроимпульса) С на вход “С” регистра.

Рис. 1. Функциональные схемы основных видов регистров.

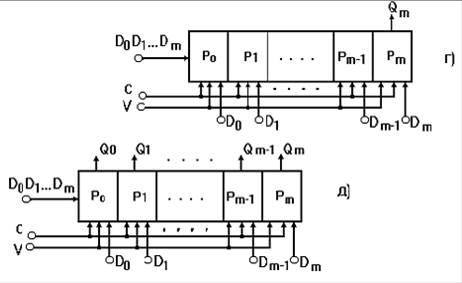

Количество разрядов записываемой цифровой информации определяется разрядностью регистра, а разрядность регистра, в свою очередь, определяется количеством триггеров, образующих этот регистр. В качестве разрядных триггеров регистра памяти используются синхронизируемые уровнем или фронтом триггеры. Регистры памяти могут быть реализованы на D-триггерах, если информация поступает на входы регистра в виде однофазных сигналов и на RS-триггерах, если информация поступает в виде парафазных сигналов. В некоторых случаях регистры могут иметь вход для установки выходов в состояние “0”. Этот асинхронный вход называют входом R “сброса” триггеров регистра. На рис. 2 приведены схемы четырехразрядных регистров памяти на D- и RS-триггерах, синхронизируемых уровнем и фронтом синхроимпульсов (обычно четыре триггера объединены в одном корпусе ИМС).

Регистры сдвига. Регистры с последовательным приемом или выдачей информации называются сдвиговыми регистрами или регистрами сдвига. Регистры сдвига могут выполнять функции хранения и преобразования информации. Они могут быть использованы для построения умножителей и делителей чисел двоичной системы счисления, т.к. сдвиг двоичного числа влево на один разряд соответствует умножению его на два, а сдвиг вправо - делению на два. Регистры сдвига широко используются для выполнения различных временных преобразований цифровой информации: последовательное накопление последовательной цифровой информации с последующей одновременной выдачей (преобразование последовательной цифровой информации в параллельный код) или одновременный прием (параллельный прием) информации с последующей последовательной выдачей (преобразование параллельного кода в последовательный).

а) б) в)

Рис. 2. Регистры хранения, на D – триггерах, синхронизируемых уровнем синроимпульса (а), фронтом (б) и на RS – триггерах, синхронизируемых фронтом (в)

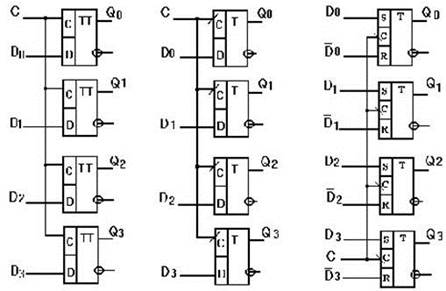

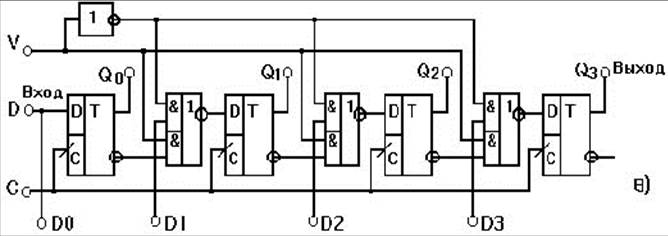

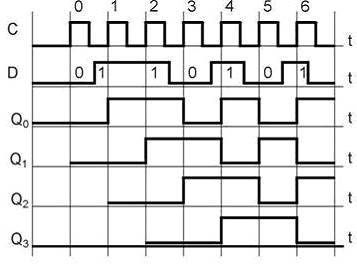

Регистры сдвига могут служить также в качестве элементов задержки сигнала, представленного в цифровой форме. Действительно, регистры с последовательным приемом (вводом) и выводом осуществляют задержку передачи информации на m+1 тактов (m+1 - число разрядов регистра) машинного времени. Регистры сдвига обычно реализуются на D-триггерах (рис. 3 а) или на RS-триггерах (рис. 3 б), где для ввода информации в первый разряд включается инвертор (первый разряд представляет собой D-триггер). Следует отметить, что все регистры сдвига строятся на базе двухступенчатых триггеров или синхронизируемых фронтом синхроимпульса. Разрядность регистров сдвига, как и у регистров хранения, определяется количеством триггеров, входящих в их состав. На рис. 3 приведены схемы четырехразрядных регистров сдвига, реализованных на D- и RS-триггерах, а временные диаграммы, поясняющие работу регистра сдвига, приведены на рис. 4.

Вывод параллельной информации из регистра сдвига (см. рис. 3 в) осуществляется при подключении всех триггеров регистра к отдельным выводам (на рис. 3 а и б эти выводы показаны штриховыми линиями). Как было сказано выше, регистры сдвига синхронизируются фронтом тактирующих импульсов, т.е. запись новой информации в триггеры регистра происходит в течение очень короткого времени - за время длительности фронта синхроимпульса, вернее в момент поступления соответствующего фронта синхроимпульса. Обычно, это “время” значительно меньше времени распространения сигнала, т.е. времени переключения триггера регистра в новое состояние. Работу регистра сдвига рассмотрим на примере схемы, приведенной на рис. 3 а.

Можно предположить, что в начале все триггеры регистра находятся в состоянии логического нуля, т.е. Q0=0, Q1=0, Q2=0, Q3=0. Если на входе D-триггера Т1 имеет место логический 0, то поступление синхроимпульсов на входы “С” триггеров не меняет их состояния.

Как следует из рис. 3, синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 - уровни логического “0”, т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического “0”, а на вход “D” первого триггера, по условию примера, подается “0” из внешнего источника информации. При подаче на вход “D” первого триггера “1”, с приходом первого синхроимпульса, в этот триггер запишется “1”, а в остальные триггеры - “0”, т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 “ещё” присутствовал логический “0”. Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе “D” в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая “1” , с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной “1” с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д. (рис. 4). Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

После поступления m синхроимпульсов (на рис. 3 и рис. 4 m = 4) регистр оказывается полностью заполненным разрядами числа, вводимого через последовательный ввод “D”. В течение следующих четырех синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным (регистр окажется полностью очищенным только при условии подачи на его вход уровня “0” в режиме вывода записанного числа).

Рис. 3. Регистры сдвига на D – триггерах а), RS – триггерах б) и комбинированный регистр на D – триггерах

Рис. 4. Временная диаграмма работы регистра сдвига.

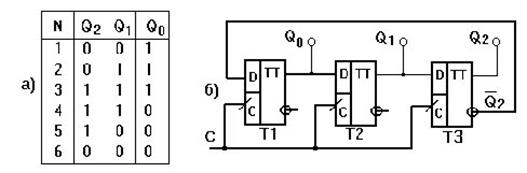

Рис. 5. Таблица состояний а) и схема б) счетчика Джонсона на трехразрядном регистре сдвига

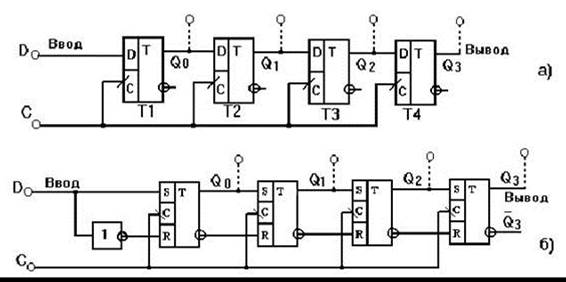

Кольцевые счетчики. На базе регистров сдвига можно построить кольцевые счетчики - счетчики Джонсона. Счетчик Джонсона имеет коэффициент пересчета, вдвое больший числа составляющих его триггеров. В частности, если счетчик состоит из трех триггеров (m=3), то он будет иметь шесть устойчивых состояний. Счетчик Джонсона используется в системах автоматики в качестве распределителей импульсов и т.д.

Таблица состояний счетчика Джонсона (рис. 5) содержит 2m (m - количество триггеров в составе регистра) строк и m-столбцов. Количество разрядов счетчика определяется количеством триггеров (рис. 5). Рассмотрим схему трехразрядного счетчика Джонсона, выполненного на базе D-триггеров (регистр сдвига реализован на D-триггерах). Для построения кольцевого счетчика достаточно соединить инверсный выход последнего триггера регистра (последнего разряда) с входом “D” (с входом, предназначенным для ввода последовательной информации) первого триггера.

Предположим, что вначале все триггеры находятся в состоянии “0”, т.е. Q0= Q1=Q2=0. При этом на входе “D” первого триггера присутствует уровень “1”, т.к  =1. Первым синхроимпульсом в триггер Т1 запишется “1”, вторым - единица запишется в первый триггер, из первого - во второй и т.д. до тех пор, пока на всех выходах регистра не будет “1”. После заполнения регистра единицами, на инверсном выходе триггера Т3 появится

=1. Первым синхроимпульсом в триггер Т1 запишется “1”, вторым - единица запишется в первый триггер, из первого - во второй и т.д. до тех пор, пока на всех выходах регистра не будет “1”. После заполнения регистра единицами, на инверсном выходе триггера Т3 появится  =0 и четвертым синхроимпульсом в Т1 запишется логический “0” (рис. 5 б).

=0 и четвертым синхроимпульсом в Т1 запишется логический “0” (рис. 5 б).

После поступления последующих трех синхроимпульсов регистр обнуляется и на его вход “D” снова подается уровень “1”. Таким образом, цикл повторения состояния кольцевого счетчика состоит из шести тактов синхросигнала. Как видим, при работе в начале от первого триггера до последнего триггера распространяется “волна единиц”, а затем “волна нулей”. Код, в котором работает счетчик Джонсона, называют кодом Либау-Крейга.

В приложениях приведены схемные обозначения и нумерация выводов регистров, выпускаемых в интегральном исполнении.

| <== предыдущая лекция | | | следующая лекция ==> |

| Нормативная ширина колеи | | | Лекция 22. Счетчики |

Дата добавления: 2016-09-20; просмотров: 3886;