Дифференциальный (балансный) усилительный каскад

Дифференциальные и операционные усилители

Дифференциальные усилители

Дифференциальный (балансный) усилительный каскад

При рассмотрении каскада с общим эмиттером обнаружен ряд трудностей, возникающих при создании усилителей. Во-первых, при стабилизации режима покоя с помощью сопротивления RЭ происходит значительное снижение коэффициента усиления каскада в результате действия отрицательной обратной связи. Во-вторых, при связи каскадов друг с другом коэффициент усиления уменьшается за счет потерь на резистивных элементах. В-третьих, в усилителях имеется дрейф нуля. Эти серьезные недостатки частично или полностью исключены в дифференциальном каскаде, который поэтому находит чрезвычайно широкое применение.

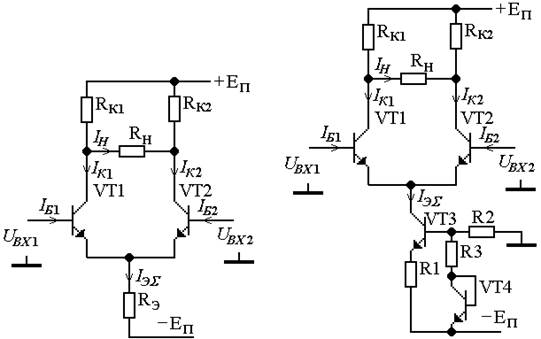

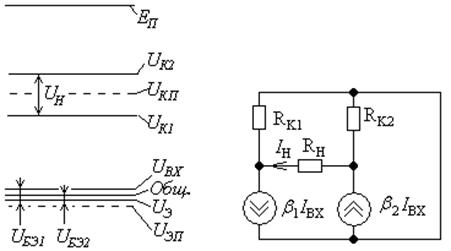

Простейшая схема дифференциального каскада приведена на рис. 3.1, а. Транзисторы VТI, VТ2 и резисторы RК1 и RК2 образуют мост, в одну диагональ которого включаются источники питания +EK и -ЕК, а в другую - нагрузка. Дифференциальный каскад нередко называют также параллельно-балансным каскадом. Высокие показатели каскада могут быть достигнуты только при высокой симметрии (балансировке) моста. В симметричном каскаде RК1 =RК2 = =RК, транзисторы должны быть идентичны по своим параметрам. Последнее достижимо только при изготовлении транзисторов на одном кристалле по одной технологии, поэтому дифференциальные каскады используют в настоящее время только в виде (или в составе) интегральных микросхем.

а) б)

Рис. 3.1 Дифференциальные каскады

Напряжение база-эмиттер транзисторов VT1, VT2 изменяется на сотые доли вольта, поэтому ток резистора RЭ практически неизменен. При нулевых входных сигналах UBX1 = UBX2 = 0 и идентичности транзисторов VT1, VT2 их эмиттерные токи одинаковы и равны

. (3.1)

. (3.1)

Дрейф напряжения нагрузки (при нулевых входных сигналах) равен

При идентичности параметров транзисторов эмиттерные токи покоя равны  , коэффициенты передачи по току равны

, коэффициенты передачи по току равны  , обратные коллекторные токи равны

, обратные коллекторные токи равны  , все параметры транзисторов от температуры меняются одинаково, соответственно, дрейф напряжения равен нулю. Реально полной идентичности параметров транзисторов добиться невозможно, поэтому существует остаточный дрейф.

, все параметры транзисторов от температуры меняются одинаково, соответственно, дрейф напряжения равен нулю. Реально полной идентичности параметров транзисторов добиться невозможно, поэтому существует остаточный дрейф.

Для получения максимального выходного напряжения, эмиттерные токи покоя транзисторов VT1, VT2 выбираются так, чтобы напряжения покоя коллекторов были равны половине напряжения питания

, (3.2)

, (3.2)

приняв  , определим величину эмиттерного сопротивления, учтя что

, определим величину эмиттерного сопротивления, учтя что

и

и  , отсюда

, отсюда

. (3.3)

. (3.3)

Для повышения стабильности суммарного эмиттерного тока и изменения режима покоя при изменении напряжения питания, в эмитерную цепь включают схему, ведущую себя как источник тока (рис. 3.1, б).

Суммарный эмиттерный ток равен

, (3.4)

, (3.4)

Где коэффициент деления делителя  .

.

Входной сигнал может подаваться на один из входов, второй вход должен быть подключен к общей точке, или на оба входа одновременно в противофазе. Входные сигналы обязательно должны быть связаны с общей точкой.

Рассмотрим ситуацию, когда UBX1 > 0, а UBX2 = 0:

, так как

, так как  - то

- то  .

.

Соответственно  .

.

Рассмотренный процесс иллюстрирует рис. 3.2, на котором условно показаны потенциалы в режиме покоя и при UBX1 > 0. За положительное направление тока нагрузки принят ток, текущий по стрелке.

а) б)

Рис. 3.2 а) – Потенциалы в дифференциальном каскаде при UBX1 > 0,

б) – схема замещения каскада

Дата добавления: 2016-04-14; просмотров: 2251;