Дифференциальные усилительные каскады

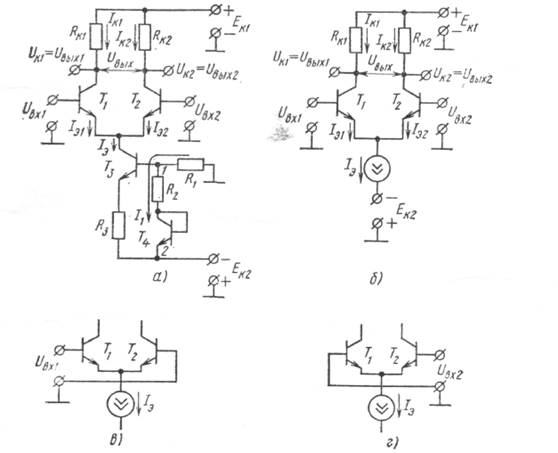

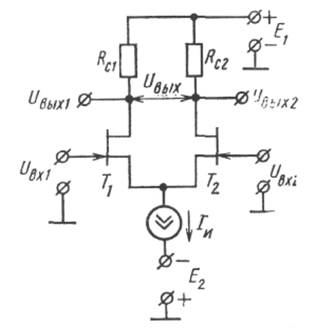

Радикальным средством уменьшения дрейфа УПТ является применение параллельно-балансных (д и ф ф е р е н-ц и а л ь н ы х) каскадов. Одна из наиболее распространенных схем дифференциальных усилительных каскадов представлена на рис. 2.33, а. По этой схеме построены каскады, выпускаемые в виде отдельных микросхем (например, К118УТ1, К122УТ1); она используется также во входных каскадах многих УПТ интегрального исполнения.

Рис. 2.33. Схема (а) и упрощенная схема (б) параллельно- балансного (дифференциального) усилительного каскада; способы подачи дифференциального входного сигнала (в, г)

напряжение- снимается между коллекторами транзисторов (т. е. с диагонали моста) или с коллекторов.

На транзисторе Т3 собрана схема источника стабильного тока Iэ, определяющего сумму эмиттерных токов Iэ1 и Iэ2транзисторов Т1 , Т2. В схему источника стабильного тока входят резисторы R1, R2, R3и источник питания ЕК2. Транзистор Т4в диодном включении предназначен для повышения стабильности тока Iэ в зависимости от изменения температуры (элемент температурной компенсации). Для определения тока Iэ найдем напряжение между точками 1—2 схемы. Если пренебречь током / Iб3, существенно меньшим тока Iэ, и принять Iэ3 ≈ Iк3 = Iэ можно записать

где

|

Из этих уравнений находим

|

Величина I1 R2 в числителе этого выражения существенно больше разности напряжений Uбэтранзисторов Т4, Т3. Поэтому ток Iэ определяется преимущественно сопротивлениями R2, R3 и током I1. Поскольку зависящие от температуры параметры Uбэ4 и Uбэ3входят в выражение в виде разности, зависимость тока от температуры проявляется незначительно. Дальнейшее рассмотрение дифференциального каскада проведем на примере схемы рис. 2.33, б, где источник стабильного тока на транзисторе Т3 заменен источником тока Iэ.

Дифференциальный каскад допускает подачу входных сигналов от двух источников (на оба входа Uвх1, Uвх2) или от одного источника входного сигнала (рис. 2.33, в, г). В последнем случае входной сигнал подается на базу одного из транзисторов или между обеими базами. Входы Uвх1, Uвх2 при схемах соединения по рис. 2.33, в, г называются дифференциальными.

Питание каскада производится от источников .+ Ек1и — Ек2с равными напряжениями. Ввиду последовательного соединения этих источников суммарное напряжение питания схемы Ек = Ек1 + Ек2. С помощью напряжения питания ЕК2 снижают потенциал эмиттеров транзисторов Т1, Т2 относительно общей точки схемы («земли»). Это позволяет подавать сигналы на входы усилителя без введения дополнительных компенсирующих напряжений, что требовалось, в частности, в схеме рис. 2.32, а.

Схема дифференциального каскада требует применения близких по параметрам транзисторов Т1, Т2 и равенства сопротивлений RК1, RК2 (рис. 2.33, б). Благодаря этому при входных сигналах, равных нулю, достигается баланс моста, напряжения на коллекторах обоих транзисторов равны и выходное напряжение, снимаемое с диагонали, Uвых = Uвых1— Uвых2 = 0. Высокая стабильность схемы в отношении изменения напряжения питания, температуры и прочих факторов объясняется тем, что при одинаковом дрейфе по обоим усилительным каналам каскада напряжения на коллекторах изменяются на одну и ту же величину и дрейф на выходе каскада отсутствует, В реальных условиях за счет существующего разброса параметров транзисторов (например, β и Iк0(э)) или их неодинакового изменения во времени некоторый дрейф в каскаде все же имеется. Однако он существенно меньше, чем в предыдущих схемах, поскольку величина дрейфа здесь определяется разностным дрейфом двух близких по параметрам усилительных каналов. Идентичность параметров транзисторов Т1 и Т2легко достигается при интегральном (микросхемном) исполнении, когда их изготовление осуществляется в едином технологическом процессе на общем кристалле полупроводника.

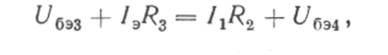

Рис. 2.34. Схема дифференциального

каскада при входном сигнале, равном

нулю (а); потенциальная диаграмма

выходных цепей (б)

Схема дифференциального каскада при Uвх = 0 показана на рис. 2.34, а. Ток Iэ делится поровну между двумя транзисторами, т. е. Iэ1 = Iэ2 = Iэ/2. Значения эмиттерных токов Iэ1, Iэ2 определяются входными токами смещения (базовыми токами покоя): Iбп1 = Iбп2 = Iэ/2(1+ β) = Iвх см. Базовые токи, являющиеся составляющими токов эмиттеров транзисторов, протекают в цепи с источником тока Iэ и напряжением питания Ек2. Равенству эмиттерных токов транзисторов будет соответствовать равенство их коллекторных токов: Iк1 = Iк2 = α Iэ/2 ≈ Iэ/2 и напряжений на коллекторах: IUк1 = IUк2 = α IUэ/2 ≈ Ек1 - Iэ RК /2 (рис. 2.34, б), где RК1 = RК2 = RК(учитываем только абсолютные значения напряжений). Данное состояние схемы характеризует режим баланса каскада или режим покоя.

Рассмотрим работу схемы при наличии входного сигнала, например при подаче его на вход транзистора Т1 (Uвх1на рис. 2.35, а), при этом по-прежнему Uвх2= 0. Предположим, что напряжение входного сигнала имеет положительную полярность.

Под воздействием входного сигнала через входные цепи обоих транзисторов будет протекать входной ток Iвх увеличивающий ток базы транзистора Т1 и уменьшающий ток базы транзистора Т2. При этом токи Iэ1, Iк1 увеличиваются, а токи Iэ2, Iк2 уменьшаются. Изменение токов обоих транзисторов происходит на одну и ту же величину, поскольку сумма токов Iэ1 + Iэ2 = Iэ остается неизменной.

Изменения коллекторных токов вызывают изменение потенциальной диаграммы каскада (рис. 2.35, б). Напряжение Uк1 = ЕК1 — Iк1 RК1 уменьшается, что вызывает приращение напряжения — ΔUк1, противоположное по знаку (проинвертированное) напряжению еГНапряжение

Рис. 2.35. Схема дифференциального каскада при наличии входного сигнала (а); потенциальная диаграмма выходных цепей (б)

Uк2 = ЕК2 — Iк2 RК2 возрастает, что создает соответственно приращение напряжения +ΔUк2 того же знака (непроинвертированного по знаку), что и напряжение входного сигнала.

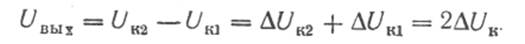

Таким образом, для рассматриваемого способа передачи входного сигнала выход каскада со стороны коллектора транзистора Т1 (Uвых1) является инвертирующим, а со стороны коллектора транзистора Т2 (Uвых2) —неинвертирующим. Сигнал, снимаемый с обоих коллекторов, называется дифференциальным:

Большие значения напряжения на входе вызывают соответственно большие значения выходного напряжения. Изменения выходных напряжений схемы под воздействием сигнала на входе прекращаются, когда под влиянием входного 'тока ток базы одного из транзисторов (в рассматриваемом случае ток Iб2) становится равным нулю, а ток Iэ протекает только через один из транзисторов (Т1). Выходные напряжения каскада при этом составляют:

Подобно описанным, но с иными знаками приращений, протекают процессы в схеме при изменении полярности подводимого входного напряжения или при подключении входного сигнала по схеме рис. 2.33, г.

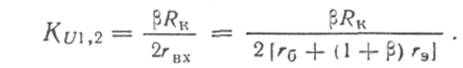

Определим коэффициенты усиления по напряжению дифференциального каскада.

Входной ток каскада при одинаковых параметрах обоих транзисторов

|

где rвх — входное сопротивление транзистора.

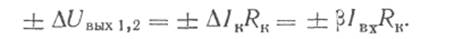

Входной ток создает приращения коллекторных токов ±ΔIк = ± β Iвх и напряжений на коллекторах:

|

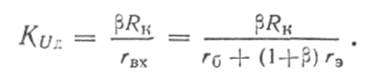

После подстановки сюда выражения для тока Iвх и деления на еГопределяем коэффициенты усиления по напряжению каскада (по обоим выходам Uвых1, Uвых2):

При RГ = 0 это выражение принимает вид

|

Коэффициент усиления каскада по дифференциальному выходу (Uвых ) при Rн=∞находят из соотношения

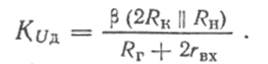

|

С учетом сопротивления Rн

При Rн=∞ и RГ = 0

|

Соотношения (2.131), (2.134) используют для оценки коэффициентов усиления дифференциального каскада. Коэффициенты усиления по выходам Uвых1 и Uвых2при Rн=∞ и RГ = 0 близки к KU/2 для одиночного каскада ОЭ [ср. выражения (2.25) и (2.131)]. Это объясняется тем, что при RГ = 0 к участку база — эмиттер каждого транзистора в дифференциальном каскаде прикладывается половина напряжения источника входного сигнала еГ/2. Поскольку приращения сигналов между коллекторами обоих транзисторов суммируются, коэффициент усиления по дифференциальному выходу KUдблизок к значению KUдлятого же каскада [ см.(2.25), (2.134) ].

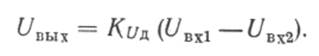

Как указывалось, схема дифференциального усилительного каскада допускает подачу входных сигналов одновременно на оба входа (см. рис. 2.33, б). Дифференциальное входное напряжение при сигналах Uвх1, Uвх2 неодинаковой полярности будет равно Uвх = Uвх1 + Uвх2, а дифференциальное выходное напряжение Uвых = KUд (Uвх1 + Uвх2).

Представляет интерес также подключение входных напряжений одинаковой полярности, т. е. двух совпадающих по фазе (синфазных) сигналов. Дифференциальный каскад позволяет решать часто встречающуюся на практике задачу сравнения с высокой степенью точности значений напряжений входных сигналов или увеличения их разности. Это, в частности, объясняет название «дифференциальный каскад». При наличии двух синфазных входных сигналов дифференциальное выходное напряжение пропорционально разности Uвх1 - Uвх2

При подаче на входы двух сигналов одинаковой полярности необходимо учитывать возможность появления на выходах Uвых1, Uвых2 так называемой выходной синфазной ошибки. Она обусловливается наличием на обоих входах одинакового постоянного напряжения (постоянной составляющей), равного наименьшему из напряжений Uвх1, Uвх2. Если, например, Uвх1 > Uвх2, то напряжение Uвх1 можно рассматривать как синфазное напряжение Есинф, приложенное одновременно к обоим входам, а разность Uвх1 — Uвх2 = еГ – как дифференциальное входное напряжение между входами. При RГ1 = RГ2 =0 появление выходной синфазной ошибки можно показать на примере схемы рис. 2.36, а.

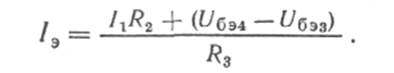

|

Рис. 2.36. Схема дифференциального каскада при наличии синфазного входного напряжения (а); потенциальная диаграмма выходных цепей (б)

В дифференциальном каскаде рис. 2.36, а с идеальным источником стабильного тока Iэ при еГ = 0 и общем напряжении Есинфнапряжение баланса Uбал = Uк1 = Uк2 не должно изменяться. Однако наличие синфазного напряжения Есинфприводит к повышению напряжения Uкэтранзистора Т3 (см. рис. 2.33, а), используемого в схеме в качестве источника стабильного тока, что при неидеальности источника вызывает некоторое увеличение тока Iэ. Это обусловливает положительные приращения токов эмиттера и коллектора транзисторов Т1 и Т2 и уменьшение на ΔUбал напряжения баланса Uбал (рис. 2.36,б). При подаче синфазной э. д. с. отрицательной полярности уровень баланса увеличивается на ΔUбал. При еГ > 0 напряжения на коллекторах получают приращения относительно напряжения (Uбал ± ΔUбал. Иными словами, ± ΔUбал проявляется на выходах Uвых1, Uвых2 как величина синфазной ошибки при усилении. При одинаковых параметрах транзисторов Т1, Т2 наличие синфазной э. д. с. не вызывает появления синфазной ошибки на дифференциальном выходе каскада. Учет синфазных ошибок усиления важен в многокаскадных УПТ с дифференциальным каскадом на входе.

Синфазную ошибку усиления оценивают коэффициентом синфазной передачи каскада Ксинф = ΔUбал / Есинф, который обычно много меньше единицы. Качество дифференциального каскада характеризуется отношением Ксинф/ KUд, показывающим способность каскада различать малый дифференциальный сигнал на фоне большого синфазного напряжения. Выражение 201g (Ксинф/ KUд) характеризует коэффи циент ослабления синфазного сигнала (КОСС) дифференциального каскада. В современных дифференциальных усилительных каскадах величина КОСС может составлять от —60 до —100 дБ.

Для дифференциальных усилительных каскадов, а также УПТ на их основе важным параметром является входное сопротивление. Сопротивление Rвх, равное сумме входных сопротивлений транзисторов Т1, Т2 (Rвх = 2rвх) использовалось ранее при расчете входных токов [см. выражение (2.128)]. Величина Rвх определяет сопротивление нагрузки для источника входного сигнала, поэтому сопротивление Rвх целесообразно иметь возможно большим. Поскольку входная характеристика транзистора нелинейна (см. рис. 1.28, б), высокому входному сопротивлению будет соответствовать выбор малых базовых токов в режиме покоя (токов смещения) и соответственно малых токов Iэ. При этом достижимые значения входного сопротивления составляют десятки и сотни килоом.

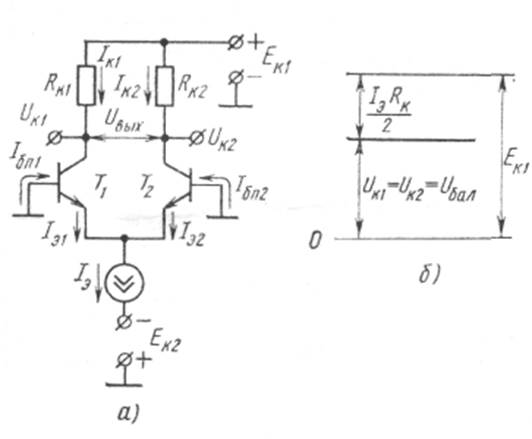

Существенное повышение (до десятков мегом) входного сопротивления дает выполнение дифференциального каскада на полевых транзисторах (рис. 2.38).

|

Рис. 2.38. Схема дифференциального каскада на полевых транзисторах

По принципу действия эта схема не отличается от схемы рис. 2.33, а. Аналогично выполняется источник стабильного суммарного тока истоков Iи. В настоящее время техника усиления электрических сигналов базируется на интегральной электронике. Как известно, реактивные элементы трудны в интегральной реализации. Учитывая это, подавляющее большинство усилителей различного назначения выполняют на основе УПТ с непосредственной связью. По такому принципу, в частности, создают усилители звуковых частот, усилители высокой частоты, широкополосные и линейные импульсные усилители, узкополосные (избирательные) усилители. На базе УПТ с непосредственной связью выполняют также генераторы синусоидальных колебаний и многие импульсные схемы

Дата добавления: 2016-04-02; просмотров: 3027;