КОМБИНАЦИОННЫЕ СХЕМЫ. ДЕШИФРАТОРЫ

РЕГИСТРЫ

Регистрами называют функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации. В зависимости от способа записи информации (кода числа) различают параллельные, последовательные и параллельно - последовательные регистры.

Параллельные регистры. В параллельных регистрах запись двоичного числа (слова) осуществляется параллельным кодом, т.е. во все разряды регистра одновремено. Их функция сводится только к приему, хранению и передаче информации (двоичного числа). В связи с этим параллельные регистры часто называют регистрами памяти.

Параллельный N-разрядный регистр состоит из N триггеров, каждый из которых имеет число входов, соответствующих количеству источников информации. Если источник цифровой информации один, то каждый триггер имеет один вход. При двух и трех параллельных каналах информации триггер разряда выполняется на два и три входа. Запись цифровой информации того или иного канала в регистр осуществляется по цепи управления регистром.

Принцип построения параллельных регистров иллюстрируется их структурной схемой (рис. 3.50) при одном канале четырехразрядной цифровой информации. Обозначения на рисунке: Т1 — триггер младшего разряда; Т4 — триггер старшего разряда; Э1 — Э4 — элементы, предназначенные для управления записью информации в регистр; Э5 — Э8 — элементы, служащие для управления считыванием информации из регистра.

Рис. 3.50. Структурная схема параллельных регистров

Перед записью двоичного числа все триггеры устанавливают в состояние «0» подачей импульса по входу «Установка нуля». Для записи в регистр входной информации подают импульс записи, открывающий входные элементы И. Код входного числа записывается в регистр. Если, например, на входе присутствует код 1011, что соответствует числу 11, то это же число будет записано в регистр. По окончании операции записи информация, записанная в регистр, сохраняется, несмотря на то что входная информация (число) может изменяться. Для считывания информации подают импульс по входу «Считывание». На выходные шины регистра передается код числа, записанный в регистр. При этом число, записанное в регистр, сохраняется.

Для получения новой информации описанные операции повторяются.

Последовательные регистры (регистры сдвига). Последовательные регистры (регистры сдвига) характеризуются записью числа последовательным кодом. Регистр состоит из последовательно соединенных двоичных ячеек памяти, состояния которых передаются (сдвигаются) на последующие ячейки под действием тактовых импульсов. Тактовые импульсы управляют работой регистра. Регистры сдвига могут управляться одной последовательностью тактовых импульсов. В этом случае регистры называют однотактными. При управлении двумя, тремя, четырьмя и т. д. последовательностями тактовых импульсов регистры соответственно относят к двух-, трех- и четырехтактным, а в общем случае — к многотактным.

Частота следования тактовых импульсов обычно неизменна.

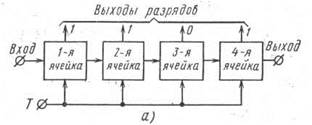

Однотактные регистры сдвига выполняют по структурной схеме рис. 3.52а, показанной для четырех разрядов Первая ячейка регистра относится к его младшему разряду, а четвертая — к старшему. При таком расположении разрядов запись числа в регистр производится начиная с его старшего разряда. При обратном расположении разрядов в регистре запись числа должна начинаться с его младшего разряда.

Тактовые импульсы подаются на все триггеры ячеек одновременно. Их воздействие направлено на переключение триггеров из состояния «1» в состояние «О» с записью единицы в триггер следующей ячейки. На рис. 3.52б приведены временные диаграммы, иллюстрирующие процесс записи информации в регистр.

Рис. 3.52. Структурная схема последовательных однотактных регистров (а) и их временные диаграммы (б)

В качестве примера взят код 1011, соответствующий числу 11. Перед записью информации регистр устанавливают в состояние «0». Для этого в отсутствие сигнала на входе подается серия тактовых импульсов с числом импульсов, равным количеству разрядов в регистре. При записи информации одновременно с поступлением кода числа подаются тактовые импульсы. Тактовыми импульсами осуществляется продвижение информации от младшего разряда регистра к старшему. В результате после четвертого тактового импульса ячейки регистра принимают состояния, соответствующие коду принятого четырехразрядного числа.

Операция считывания информации из последовательного регистра может быть проведена в параллельном или последовательном коде. Для передачи информации в параллельном коде используют выходы разрядов регистра. Таким образом, последовательный регистр позволяет осуществить операцию преобразования последовательного кода в параллельный. Считывание информации в последовательном коде реализуется подачей серии тактовых импульсов.

В последовательном регистре записанное число может быть сдвинуто тактовыми импульсами на один или несколько (k) разрядов. Операции сдвига соответствуют умножению числа на 2k. Например, сдвиг кода 0010 числа 2 на один разряд дает код 0100 (число 4), на два разряда — код 1000 (число 8).

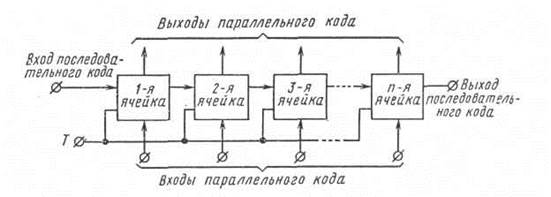

Параллельно-последовательные и реверсивные регистры. В параллельно - последовательных регистрах сочетаются свойства регистров параллельного и последовательного действия. Они позволяют осуществлять запись информации как в последовательном, так и параллельном коде, в связи с чем могут быть использованы для преобразования кодов из последовательного в параллельный и обратно. Эти регистры допускают однотактный (рис. 3.55) и многотактный принципы построения.

Рис. 3.55. Структурная схема параллельно-последовательных регистров

Для преобразования последовательного кода в параллельный серией тактовых импульсов в регистр записывается информация (число) последовательного кода. Выходы разрядов регистра при этом представляют ту же информацию в параллельном коде. Для обратного преобразования информация в регистр вводится по входам параллельного кода. Посредством серии тактовых импульсов с выхода последнего разряда регистра информация считывается в последовательном коде.

Реверсивные регистры предназначены для осуществления сдвига кода числа в сторону как старшего, так и младшего разрядов. Регистр содержит связи последовательной передачи информации в направлении от младших разрядов к старшим, а также от старших разрядов к младшим. Прямой или обратный сдвиг кода осуществляют управляющим сигналом, вводящим в действие либо прямую, либо обратную связи между разрядами.

КОМБИНАЦИОННЫЕ СХЕМЫ. ДЕШИФРАТОРЫ

При разработке различного рода цифровых управляющих устройств часто необходимо решать задачу, когда управляющее воздействие определяется значениями входных сигналов только в данный момент времени и не зависит от их значений в предыдущие моменты времени. Иными словами, выходной сигнал, характеризующий управляющее воздействие, здесь зависит только от наличия соответствующей комбинации сигналов на входах устройства. Такой принцип построения используют, в частности, для управления позиционными исполнительными механизмами, осуществления контроля, сигнализации и защиты, реализации программного управления последовательностью операций по заданному алгоритму и т. д.

Устройства, предназначенные для решения подобных задач, называют комбинационными схемами или автоматами с нулевой памятью.

Принцип проектирования комбинационных схем заключается в следующем. По требуемому алгоритму работы схемы находят управляющее воздействие (функцию) от входных сигналов (переменных). Затем по найденной функции синтезируют логическую схему ее реализации. Задачу нахождения функции связывают с необходимостью построения схемы с минимальным содержанием в ней логических элементов. Для этого функция предварительно проходит стадию минимизации, т. е. приведения ее к наиболее простому виду. Математическим аппаратом анализа и синтеза комбинационных схем служит алгебра логики. Примером комбинационных схем являются дешифраторы.

Дешифратором называют комбинационную логическую схему, в. которой каждой из комбинаций сигналов на входах соответствует сигнал только на одном из его выходов. Они находят применение в управляющих системах для выдачи управляющих воздействий в те или иные цепи в зависимости от комбинации сигналов на входах. Широко распространены дешифраторы для преобразования кодов, например двоичного или двоично-десятичного в десятичный.

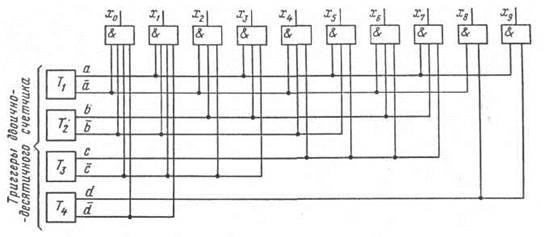

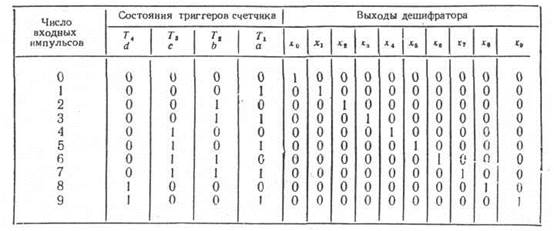

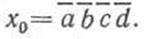

На рис. 3.56 приведена схема дешифратора, предназначенного для перевода показаний двоично-десятичного счетчика (см. рис. 3.47) с модулем счета 10 в десятичную систему счета. Сигнал «1» на соответствующем выходе дешифратора определяет число, записанное в счетчик. Так, при нулевом показании счетчика сигнал «1» присутствует только на выходе хо дешифратора (табл. 3.6). При кодах чисел 1, 2, 3, ..., 9, записанных в счетчик, дешифрация характеризуется наличием сигнала «1» соответственно только на одном из выходов x1, х2, х3, ..., х9.

Рис. 3.56. Схема дешифратора для перевода показаний двоично-десятичного счетчика в десятичную систему счета

Таблица 3.6

|

Значения сигналов а, b, с, d на выходах счетчика и требуемые при этом показания дешифратора могут быть использованы для определения элементов схемы дешифратора. Так, при нулевом показании счетчика сигнал «1» присутствует на инверсных выходах его триггеров (см. табл. 3.6), в связи с чем реализуемая каналом хо

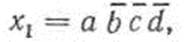

Аналогично, из табл. 3.6 для канала х1 имеем

|

|

а для канала х9

Логические функции могут быть реализованы с помощью четырехвходовых логических элементов И.

Дата добавления: 2016-04-02; просмотров: 2615;