Состояние сигналов на выходах дешифратора

| УГО сумматора | Вход CRP | Двоичные числа на входах | Код на выходах | Выход CRG | |||||||

| A1 | A2 | A3 | В1 | В2 | В3 | ||||||

5.5 Сводка основных формул (методики расчета)

Триггером (от англ. trigger – спусковой крючок) называется устройство, обладающее двумя состояниями устойчивого равновесия, и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала.

Триггеры являются базовыми элементами цифровой техники и представляют собой усилители постоянного тока с положительной обратной связью. В современной электронике триггеры выполняются, как правило, в виде микросхем, построенных на основе логических элементов И-НЕ и ИЛИ-НЕ. Пример реализации триггеров на этих элементах приведен на рисунке 5.3.

Рис. 5.3. Схемы (а, в) и УГО (б, г) асинхронных RS-триггеров

Рассмотренный триггер называют RS-триггером. Вход S называется установочным (от англ. set – устанавливать), а вход R – входом сброса (от англ. reset– вновь устанавливать).

Допустим, что на входах R и S (рис. 5.3 б) сигналы равны «0» (R=0, S=0), а на прямом выходе Q сигнал равен «1» (Q = l). Тогда на инверсном выходе  сигнал равен «0», так как на одном из входов (соединенном с Q) логического элемента ИЛИ-НЕ сигнал равен «1». На обоих входах элемента Э1сигнал «0», поэтому Q = l. Очевидно, при R = 0, S = 0 возможно и второе устойчивое состояние, при котором Q = 0,

сигнал равен «0», так как на одном из входов (соединенном с Q) логического элемента ИЛИ-НЕ сигнал равен «1». На обоих входах элемента Э1сигнал «0», поэтому Q = l. Очевидно, при R = 0, S = 0 возможно и второе устойчивое состояние, при котором Q = 0,  = l. Нетрудно видеть, что при S = l, R = 0триггер оказывается в первом устойчивом состоянии (Q = l,

= l. Нетрудно видеть, что при S = l, R = 0триггер оказывается в первом устойчивом состоянии (Q = l,  = 0), а при S = 0, R = l – во втором устойчивом состоянии (Q = 0,

= 0), а при S = 0, R = l – во втором устойчивом состоянии (Q = 0,  = l). Комбинация S = l, R = 1недопустима. При S = 1 триггер устанавливается в состояние "1" (Q = l,

= l). Комбинация S = l, R = 1недопустима. При S = 1 триггер устанавливается в состояние "1" (Q = l,  = 0), при R = 1 – сбрасывается в состояние "0" (Q = 0,

= 0), при R = 1 – сбрасывается в состояние "0" (Q = 0,  = 1).

= 1).

Аналогично работает RS-триггер на элементах И-НЕ (рис. 5.3 в)с той разницей, что он должен иметь инверсные входы, т. е. устанавливаться в состояние «1» при S = 0 и сбрасываться в состояние «0» при R = 0. Запрещенная комбинация входных сигналов для этой схемы – «0», «0».

Триггеры классифицируются по способу организации логических связей на триггеры с раздельной установкой состояний сигналов "0" и "1" на выходах (RS-триггеры); триггеры со счетным входом (Т-триггеры); универсальные триггеры (JK-триггеры); триггеры с приемом информации по одному входу (D-триггеры).

Регистром (от англ. register – журнал записей) называется устройство, предназначенное для записи и хранения дискретного "слова" – двоичного числа или другой кодовой комбинации. Регистры состоят из последовательно соединенных триггеров – по одному триггеру для каждого двоичного разряда регистра. Запись информации в регистр и считывание её может осуществляться в параллельном и последовательном кодах.

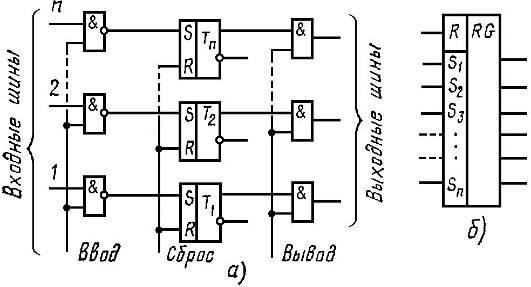

На рисунке 5.4 приведена схема и условное обозначение n-разрядного регистра на RS-триггерах. Информация в ячейки регистра записывается по команде "Ввод" (логическая "1" на входе "Ввод"). Тогда сигналы п входов установят в соответствующие состояния триггеры Т1 - Тп. На выходе регистра информация появится по команде "Вывод", в её отсутствие на выходах – логические нули. При считывании информация, записанная в регистре, сохраняется. Рассмотренный регистр запоминает и выдает информацию в параллельных кодах, когда каждому разряду соответствует отдельная линия.

Рис. 5.4. Схема (а) и условное графическое обозначение (б) регистра

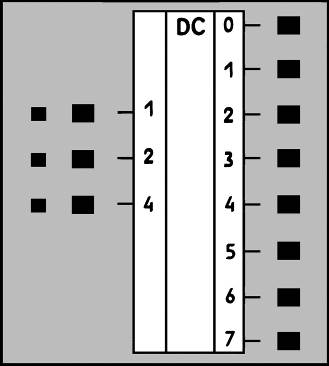

В работе исследуется 4–разрядный регистр с последовательным (вход 0→) и параллельным (входы 0, 1, 2, 3) вводом информации (рис. 5.5). На вход С подаются тактовые импульсы для продвижения информации на выходы 0, 1, 2, 3. Вход EWR служит для переключение с последовательного на параллельный ввод информации и наоборот. Вход R служит для подачи импульса для сброса информации ("обнуление" регистра).

Если на входе EWR логическая "1", то через вход 0→ с помощью тактовых импульсов на входе С осуществляется последовательный ввод информации. При наличие на входе EWR логического "0" через входы 0, 1, 2, 3 подаются сигналы ("0" и "1") кода двоичного числа и после поступления на вход С тактового импульса происходит параллельная загрузка регистра.

Рис. 5.5. УГО 4-разрядного сдвигающего регистра

с параллельным и последовательным вводом информации

Цифровым счетчиком импульсов называется устройство, выполняющее счет числа входных импульсов и фиксирующее это число в каком либо коде.

Счетчики импульсов строятся на основе триггеров, поэтому счет импульсов ведется в двоичной системе счисления.

Простейший двоичный четырехразрядный счетчик, схема которого показана на рисунке 5.6, а диаграмма работы – на рисунке 5.7, состоит из четырех последовательно соединенных Т-триггеров, входы R которых объединены для установки в состояние логического "0".

а) б)

Рис. 5.6. Двоичный четырехразрядный нереверсивный

счетчик импульсов по основанию 2

Рис. 5.7. Временная диаграмма работы четырехразрядного

нереверсивного счетчика импульсов по основанию 2

Счетчики бывают реверсивные и нереверсивные. Нереверсивные счетчики могут быть суммирующими, показания которых увеличиваются на единицу с приходом каждого последующего импульса, и вычитающими, показания которых соответственно уменьшается на единицу. Реверсивные счетчики могут работать одновременно как суммирующие и как вычитающие.

Дешифратором(декодером) называют устройство, предназначенное для распознавания различных кодовых комбинаций (слов).

Дешифратор преобразует кодированную информацию регистров и счетчиков в управляющие сигналы, которые подаются на исполнительные элементы вычислительного устройства, в устройство отображения информации и т.п.

Преобразование информации заключается в переводе двоичной кодовой комбинации в кодовую комбинацию какой-либо другой системы счисления. Каждому слову на входе дешифратора соответствует логическая "1" на одном из его выходов. Дешифратор, схема которого на сменной панели показана на рисунке 5.8, преобразует двоичный код в восьмеричный.

Рис. 5.8. Сменная панель ПС-9 дешифратора

Дешифраторы выпускаются в виде микросхем. Например, трехразрядный дешифратор К500ИД162М (преобразует двоичный код в восьмеричный) применяется в большинстве карманных микрокалькуляторов.

Сумматор предназначен для суммирования двоичных чисел и является основным узлом арифметико-логического устройства (АЛУ) микропроцессора.

Суммирование многоразрядных двоичных чисел выполняется многоразрядным сумматором, который строится на основе одноразрядных.

Каждый одноразрядный сумматор суммирует коды соответствующих разрядов слагаемых, прибавляет к ним значения переноса из младшего разряда и при необходимости формирует единицу переноса в следующий старший разряд.

Исследуемый в работе сумматор, сменная панель которого показана на рисунке 5.9, позволяет суммировать два трёхразрядных двоичных числа, вводимые через входы А1, А2, А3 и В1, В2, В3. Сумма двух двоичных чисел образуется на выходах 1, 2, 3. Сумматор имеет вход CRP для ввода единицы подсуммирования к младшему разряду суммы и выход CRG – для вывода единицы переноса в старший разряд суммы.

Рис. 5.9. Сменная панель ПС-10 сумматора

Дата добавления: 2016-03-20; просмотров: 2063;