Регистры приема, хранения и передачи информации.

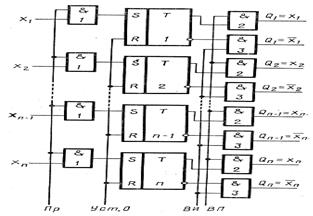

Схема двухтактного регистра, осуществляющая прием, хранение и передачу информации, приведена на рисунке 2.10. В этой схеме используются RS-триггеры, группа входных И1 и выходных И2, И3 элементов. Информация в регистр заносится по шинам X1, X2, … Xn-1, Xn только в том случае, когда на шину Пр подан управляющий сигнал приема информации.

Рисунок 2.10  – Схема двухтактного регистра

– Схема двухтактного регистра

При этом через схемы И1 проходят сигналы установки триггеров в состояние 1 только в тех разрядах, где X1 = 1.

Чтобы в остальных разрядах был записан 0, необходимо предварительно все разряды устанавливать в нулевое состояние. Записанный в регистр код слова будет храниться в нем до тех пор, пока не будет снова подан сигнал установки регистра в состояние 0.

Прямой код хранимого в регистре слова будет выдан при наличии на шине ВП управляющего сигнала «Выдача прямого кода». При этом код слова с прямых выходов триггеров регистра пройдет через группу схем И2 и в каждом разряде на выходе будет выработан сигнал Qi = Xi .

Сигнал выдачи инверсного кода ВИ позволяет через группу схем И3 получить инверсное значение кода, хранимого в регистре; при этом в каждом его разряде вырабатывается значение кода Qi = Xi. Установка триггеров регистра в состояние 0, прежде чем записать в них информацию, ведет к затратам времени.

Дешифраторы

Дешифратор — логическая схема, содержащая преобразующая входное n- разрядное двоичное слово в соответствующий управляющий сигнал, который возникает только на одном из его выходов.

Полный дешифратор – дешифратор, имеющий столько выходов m, сколько различных комбинаций может иметь n разрядное двоичное число на его входах, т. е. m = 2n.

В таблице 2.6 отражены возможные состояния дешифратора на три входа (n = 3) и восемь выходов.

Выходы дешифратора имеют нумерацию, совпадающую с десятичным представлением двоичного числа от 0 до п-1. Если, например, слово на входе имеет код 101, то единичный сигнал будет только на пятом выходе дешифратора, т.е. Y5= 1. Действительно, если на элемент И5 поступает код

X1X2X3, то есть X1 = 1, X2 = 0, X3 = 1, на всех выходах дешифратора, кроме Y5, будут логические 0.

X1X2X3, то есть X1 = 1, X2 = 0, X3 = 1, на всех выходах дешифратора, кроме Y5, будут логические 0.

Таблица 2.6− Состояния выходов дешифратора

| X1 | X2 | X3 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

Логические формулы, согласно которым строится таблица истинности и схема дешифратора, имеют следующий вид:

Y0 = X1 ^ X2 ^ X3,

Y0 = X1 ^ X2 ^ X3,  Y1 = X1 ^ X2 ^ X3,

Y1 = X1 ^ X2 ^ X3,  Y2 = X1 ^ X2 ^ X3,

Y2 = X1 ^ X2 ^ X3,  Y3 = X1 ^ X2 ^ X3,

Y3 = X1 ^ X2 ^ X3,

|  |  |  |

Y4 = X1 ^ X2 ^ X3, Y5 = X1 ^ X2 ^ X3 , Y6 = X1 ^ X2 ^ X3 , Y7 = X1 ^ X2 ^ X3

На рисунке 2.11 приведена схема линейного дешифратора на три входа, у которого число выходов m = 23 = 8, условное графическое обозначение дешифратора на рисунке 2.12.

На рисунке 2.11 приведена схема линейного дешифратора на три входа, у которого число выходов m = 23 = 8, условное графическое обозначение дешифратора на рисунке 2.12.

Рисунок 2.11−Схема линейного дешифратора Рисунок 2.12−Условное

на 3 входа графическое обозначение

Каждый выход дешифратора принимает значение, равное единице, только при одном определенном наборе входных переменных х1 – х3.

Мультиплексоры

Назначение мультиплексоров (от англ, multiplex — многократный) — коммутировать в желаемом порядке информацию, поступающую с нескольких входных шин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. Мультиплексор аналогичен бесконтактному многопозиционному переключателю.

Мультиплексоры имеет две группы входов и одним выходам.

Одни входы информационные, а другие служат для управления. К ним относятся адресные и разрешающие (стробирующие) входы. Если мультиплексор имеет п адресных входов, то число информационных входов будет 2n. Разрешающий вход управляет одновременно всеми информационными входами независимо от состояния адресных входов.

На рисунке 2.13 показаны принципиальные схемы двух простейших мультиплексоров-селекторов вида «две линии к одной» (2:1). Вариант а) обеспечивает коммутацию информационных цепей с помощью механических устройств (переключателей, реле и т. п.) без вмешательства в управляемые цепи. Переключатель S играет роль адресного устройства, положение контактов которого определяет, какие входные сигналы, х1 или х2, будут поступать на выход. Добавлением логических элементов И можно увеличить число входных информационных шин.

В варианте б для переключения входных цепей используется один внешний сигнал, когда А = 0, F = Х2; при А=1, F = X1.

Добавлением второго логического элемента И—ИЛИ (либо И—ИЛИ—НЕ, показан штриховыми линиями) можно получить распределитель сигналов, который часто применяется на практике. Здесь при А=1, F1 =Х1, F2 = Х2; при А = 0, F1 = Х2, F2 = Х1..

а) б)

Рисунок 2.13 − Мультиплексор – селектор вида 2 : 1, управляемый

а) механическими контактами; б) электронными сигналами

Эти же принципы положены в основу построения и более сложных схем мультиплексоров. Рисунок 2.14отражает логическую структуру реального

мультиплексора <четыре линии к одной» (4:1). Она содержит четыре информационных входа DO—D3, два адресных входа А и В и разрешающий вход V.

Это следует из таблицы истинности рассматриваемого мультиплексора (таблица 2.7) и из следующей логической формулы:

F = V ( B · A· D0 v B · A · D1 v B · A · D2 v B · A · D3).

Таблица 2.7 − Состояние выходных шин мультиплексора 4 :1

| Входы | Выход F | ||

| V | A | B | |

| x | x | D0 D1 D2 D3 |

Дата добавления: 2016-02-24; просмотров: 1369;