Защита памяти в процессорах второго и последующих поколений

В составленной программе, как правило, имеются ошибки. Ошибочный переход к области данных может привести их к уничтожению. Еще более опасна запись в область программы. При разрушении области операционной системы (ОС) обычно возникает системный отказ. Для предотвращения таких ситуаций в 16-разрядных процессорах второго поколения введена защита памяти. Кроме этого, в этих процессорах внедрена поддержка режима виртуальной памяти (ВП) и мультипрограммного режима. Для реализации этих нововведений в микропроцессорах используется устройство управления памятью (УУП).

Для осуществления защиты памяти кроме базового адреса вводится указатель размера и атрибут сегмента. В этом случае ситуация, когда величина смещения превышает размер сегмента, считается аварийной, т.к. возможно проникновение в область соседнего сегмента. Атрибуты сегментов могут быть самыми разными. Наиболее широко применяются следующие:

§ разделение на системную область и область пользователя;

§ разделение на область программ и данных;

§ в случае работы с областью программы производят разделение ее на участки, допускающие только считывание данных или также и запись.

Процессор в каждом цикле вырабатывает сигналы состояния, показывающие, является ли данный цикл считыванием или записью. УУП при каждом обращении к памяти сравнивает атрибуты сегментов с этими сигналами. Если в размере сегмента или в его атрибуте обнаруживается ошибка, УУП выдает в ЦП сигнал сегментной ошибки, вызывающий специальное прерывание.

Для хранения базового адреса, размера и атрибута сегмента в УУП введены специальные регистры – дескрипторы сегментов. Число таких регистров определяется количеством используемых сегментов. При этом если номер сегмента является n–разрядным, то возможно использовать 2n регистров. С целью ускорения поиска регистра они строятся на принципах ассоциативной памяти. Для этого в составе каждого регистра имеется схема сравнения искомого номера регистра с хранящимся в регистре его номером.

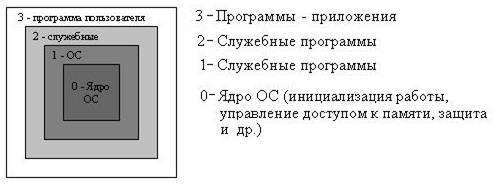

Для защиты памяти также введена система привилегий (PL), с помощью которой осуществляется защита сегментов. Система привилегий регулирует доступ к тому или иному сегменту, в зависимости от уровня его защищенности и от степени важности (привилегированности) запроса. В МП Intel х286 и всех последующих моделях установлены четыре уровня привилегий PL, которые задаются номерами от 0 до 3 (рисунок 6.6). Наиболее привилегированным является уровень с меньшим номером. Степень защищенности сегмента также имеет четыре уровня, которые схематически представляются в виде вложенных колец защиты. В процессорах фирм Motorola (МС68000) и Zilog (Z8001) предусмотрено два уровня привилегий: в системном и пользовательском режимах.

|

| Рисунок 6.6 - Уровни привилегий и защиты |

В соответствии с уровнями привилегий и защищенности установлены следующие правила доступа для сегментов программ и данных:

1) Данные из сегмента, имеющий уровень привилегий могут быть выбраны программой такого или более высокого уровня привилегий.

2) Сегмент программ, имеющий уровень защиты PL, может быть вызван программой, имеющий такой или более низкий уровень привилегий.

3) Уровень защиты и привилегий определяется двумя битами, значение которых указывает номер кольца защиты или уровня. Эти биты размещаются в байте доступа дескриптора (для привилегий дескриптора) или в селекторе (уровня привилегий запроса).

4) Выполнение команды ветвления ограничивается сегментами в пределах одной программы. В командах вызова и перехода допускается переход в сегменты другой программы при условии, что уровень ее привилегий равен текущему уровню.

Следует заметить, что процессор разрешает менее привилегированной процедуре вызвать более привилегированную, но ограничивает доступ разрешенными точками входа. Допустимые точки входа идентифицируются специальными дескрипторами, называемыми шлюзами вызова. Привилегия в шлюзе задается достаточно низкой, что позволяет обращаться в точку входа операционной системы. Размер смещения в шлюзе не учитывается.

Дескрипторы сегментов располагаются в памяти ПЭВМ. Из четырех слов дескриптора одно не используется. Формат дескриптора сегмента процессора 8086 показан на рисунке 6.7.Оно зарезервировано для последующего поколения процессоров (386 и т.д.). В дескрипторе содержится 24-разрядный базовый адрес, 16 разрядов размера сегмента, 3 разряда типа, определяющие атрибут сегмента.

Дескрипторы сегментов располагаются в памяти ПЭВМ. Из четырех слов дескриптора одно не используется. Формат дескриптора сегмента процессора 8086 показан на рисунке 6.7.Оно зарезервировано для последующего поколения процессоров (386 и т.д.). В дескрипторе содержится 24-разрядный базовый адрес, 16 разрядов размера сегмента, 3 разряда типа, определяющие атрибут сегмента.

Кроме них имеются битовые поля: Р – присутствие в основной памяти; А– обращение к сегменту; DPL – уровень привилегий дескриптора; S – бит системного сегмента. S=0 — системный; S=1 — сегмент программы или данных. В поле "Тип" указывается, кодовый это сегмент или данных, разрешена запись в него или запрещена, расширение сегмента осуществляется вниз (для стека) или обычное.

Существуют 4 уровня привилегий сегмента: 0 – высший; 3 – низший. Процессор разрешает менее привилегированной процедуре вызвать более привилегированную, но ограничивает доступ разрешенными точками входа. Допустимые точки входа идентифицируются в процессоре специальными дескрипторами, называемыми шлюзами вызова. Привилегия в шлюзе задается достаточно низкой, что позволяет обращаться в точке входа к операционной системе.

Группа дескрипторов сегментов, расположенных в глобальном адресном пространстве называется глобальной таблицей дескрипторов (GTD), а сегментов, расположенных в локальном адресном пространстве – локальной таблицей дескрипторов (LDT).

Если число задач, выполняемых ЭВМ, равно N, то и число локальных адресов также равно N и соответственно количество LDT также равно N.

GTD и N-LTD располагаются в глобальном адресном пространстве (рис.6.8).

Следует помнить, что сама LDT также представляет собой отдельный сегмент и для его описания требуется дескриптор. Дескриптор LDT хранится в GTD.

Дата добавления: 2016-02-09; просмотров: 1210;