Простейшие ЛЭ имеют следующие характеристики. 2 страница

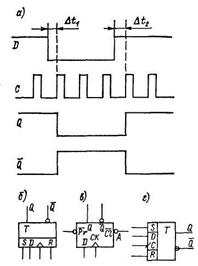

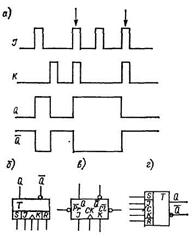

Рис. 8. D-триггер: а — временная диаграмма; б, в и г — условное графическое обозначение триггера с записью информации по фронту тактового импульса в болгарской, американской и советской литературе. Входы S и R (Рr и Сl) — установочные.

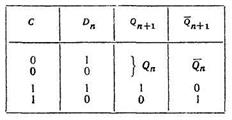

Таблица 2. Состояния D- триггера

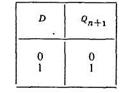

В этом случае на выходе DD4 — напряжение высокого уровня, поскольку в отсутствие тактового импульса на входе А будет напряжение высокого и на входе В — низкого уровня. С приходом тактового импульса (С=1) на входе А возникает напряжение низкого, а входе В — высокого уровня.

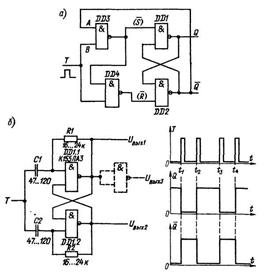

Рис. 9. D-триггер на логических элементах И—НЕ

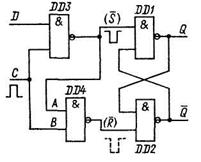

Рис. 10. Временные диаграммы работы D-триггера.

Если на вход D подано напряжение низкого уровня, на выходе DD3 будет напряжение высокого уровня, а тактовый импульс (показан на рисунке штрихами), инвертированный логическим элементом DD4, действует подобно  сигналу. Вследствие этого триггер примет состояние Q = 0 и

сигналу. Вследствие этого триггер примет состояние Q = 0 и  = 1.

= 1.

D-триггер имеет следующую таблицу состояний:

Выход Q у D-триггера принимает то же состояние, что и на входе D, в момент появления тактового импульса на входе С.

D-триггер можно собрать из четырех элементов И—НЕ.

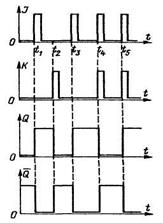

JK-триггеры.Действие JK-триггера поясняет рис. 1.4. Эти триггеры могут быть синхронными или асинхронными. Из временных диаграмм работы асинхронного JK-триггера следует, что при поочередном поступлении импульсов на входы J и К этот триггер действует подобно RS-триггеру (см. рис. 1.2, а), но отличается от него при одновременной подаче импульсов на оба входа: выходное состояние меняется на противоположное предшествующему. На рис. 1.4, а это относится к импульсам, помеченным стрелкой.

Рис. 11. УК-триггер: a— временная диаграмма; б, в и г — условное графическое обозначение триггера с записью информации по фронту тактового импульса в болгарской, американской и,, советской литературе. Входы S и R (Рr и Сl) —установочные.

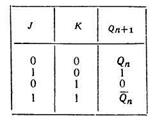

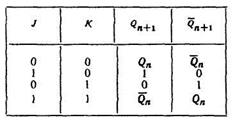

Таблица 3. Состояния JK-триггера

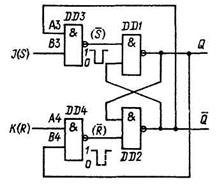

JK-триггер на логических элементах И—HЕ. С помощью

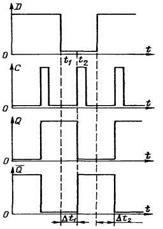

логических элементов И-НЕ К155ЛАЗ, К555ЛАЗ (ТТЛ) или К561ЛА7 (КМОП) нетрудно организовать JK-триггер. Для этого потребуется четыре логических элемента. Схема JK-триггера (рис. 2.10) отличается от схемы RS-триггера только тем, что элементы DD3 и DD4 используются по прямому назначению И—НЕ, а не как инверторы. Вход A3 соединен с выходом  , а вход В4 — с выходом Q. Действие его поясняют временные диаграммы. Если JK-триггер пребывает в нулевом состоянии (Q=0 и

, а вход В4 — с выходом Q. Действие его поясняют временные диаграммы. Если JK-триггер пребывает в нулевом состоянии (Q=0 и  =1, время до момента t1)и на вход J поступит сигнал указанной на диаграмме полярности, то за счет связи между выходом

=1, время до момента t1)и на вход J поступит сигнал указанной на диаграмме полярности, то за счет связи между выходом  и входом A3 сигнал на выходе элемента DD3 будет иметь вид с 0 на 1и действовать подобно сигналу

и входом A3 сигнал на выходе элемента DD3 будет иметь вид с 0 на 1и действовать подобно сигналу  на входе

на входе  -триггера, образованного элементами DD1 и DD2, т. е. вызовет смену состояния триггера. (В это время на входе К напряжение низкого уровня, на входе В4, связанном с выходом Q, тоже низкий уровень, в результате чего на выходе DD4 напряжение высокого уровня). Если JK-триггер находится в единичном состоянии (Q=l и

-триггера, образованного элементами DD1 и DD2, т. е. вызовет смену состояния триггера. (В это время на входе К напряжение низкого уровня, на входе В4, связанном с выходом Q, тоже низкий уровень, в результате чего на выходе DD4 напряжение высокого уровня). Если JK-триггер находится в единичном состоянии (Q=l и  =0 — до момента t1) и сигнал поступит на вход К, то, рассуждая аналогичным образом, можно убедиться, что на выходе DD4 появится сигнал низкого уровня (на схеме показан штрихами), который действует как сигнал

=0 — до момента t1) и сигнал поступит на вход К, то, рассуждая аналогичным образом, можно убедиться, что на выходе DD4 появится сигнал низкого уровня (на схеме показан штрихами), который действует как сигнал  , т. е. состояние триггера изменится снова. (При этом на выходе DD3 напряжение высокого уровня). Когда одновременно на обоих входах — J и К напряжение низкого уровня, состояние JK-триггера сохраняется.

, т. е. состояние триггера изменится снова. (При этом на выходе DD3 напряжение высокого уровня). Когда одновременно на обоих входах — J и К напряжение низкого уровня, состояние JK-триггера сохраняется.

Рис. 12. JK-триггер на логических элементах И—НЕ.

Рис. 13. Временная диаграмма работы JK-триггера.

Как видим, до сих пор действие JK- и RS-триггеров полностью совпадало. При этом вход J соответствовал входу S, а К — входу R.

Когда на обоих входах — J и К одновременно появляется напряжение высокого уровня, то в зависимости от предшествующего состояния триггера возможны два случая.

1. JK-триггер был в единичном состоянии (Q=l и  = 0 — после момента t3). Поскольку на входе A3 действует сигнал

= 0 — после момента t3). Поскольку на входе A3 действует сигнал  = 0, на выходе DD3 сохраняется напряжение высокого уровня, независимо от того что на входе ВЗ элемента DD3 возникло напряжение высокого уровня J=1. При этом на выходе логического элемента DD4, который действует как И—НЕ, за счет оединения входа В4 с выходом Q (Q=l) появится сигнал

= 0, на выходе DD3 сохраняется напряжение высокого уровня, независимо от того что на входе ВЗ элемента DD3 возникло напряжение высокого уровня J=1. При этом на выходе логического элемента DD4, который действует как И—НЕ, за счет оединения входа В4 с выходом Q (Q=l) появится сигнал  и триггер

и триггер  -типа, образованный элементами DD1 и DD2, изменит свое состояние. Уровень напряжения на выходе Q станет низким, а на выходе

-типа, образованный элементами DD1 и DD2, изменит свое состояние. Уровень напряжения на выходе Q станет низким, а на выходе  — высоким (начиная с момента t4).

— высоким (начиная с момента t4).

2. JK-триггер был в нулевом состоянии (Q= 0 и  =1 — после момента t4). Рассуждая аналогичным образом, нетрудно убедиться, что на выходе DD4 сохраняется напряжение высокого уровня, а на выходе DD3— низкого, которое действует как сигнал

=1 — после момента t4). Рассуждая аналогичным образом, нетрудно убедиться, что на выходе DD4 сохраняется напряжение высокого уровня, а на выходе DD3— низкого, которое действует как сигнал  , переключающий

, переключающий  -триггер (напряжение на выходе Q станет высоким, а на выходе

-триггер (напряжение на выходе Q станет высоким, а на выходе  — низким — после момента t5).

— низким — после момента t5).

Таким образом, в обоих случаях JK-триггер меняет свое состояние. В этом как раз и состоит различие между JK- и RS-триггерами.

Работа JK-триггера определяется следующей таблицей состояний:

Триггер можно собрать из логических элементов И-НЕ.

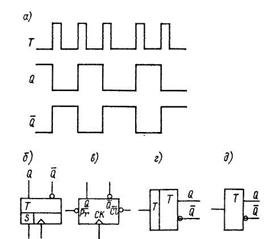

T-триггеры.Эти триггеры — асинхронные, имеют только один информационный вход, и каждый импульс, поступающий на него, ведет к смене выходного состояния (рис. 1.5).

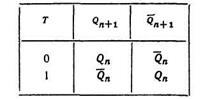

Часто для иллюстрации действия триггеров пользуются не временными диаграммами, а таблицами состояний (табл. 1.1... 1.4). В таблицах индексом п обозначено состояние триггера до момента воздействия сигнала на информационном входе, а индексом п+1 — после этого момента.

Рис. 14. T-триггер: а — временная диаграмма; б, в и г, д — условное графическое обозначение в болгарской, американской и советской литературе.

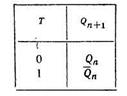

Таблица 4. Состояния T-триггера

Т-триггер на логических элементах И—НЕ.Из уже упоминавшихся логических элементов в интегральном исполнении типа К155ЛАЗ, К555ЛАЗ (ТТЛ) либо типа К176ЛА7, К561ЛА7 (КМОП) легко собрать Т-триггер. Для этого потребуется четыре логических элемента И—НЕ. Схема приведена на рис. 2.9, а.

В отличие от D-триггера (см. рис. 2.8) вход А логического элемента DD3 постоянно соединен с выходом  . Действие этого триггера легко понять. Когда Q=l, на другом выходе

. Действие этого триггера легко понять. Когда Q=l, на другом выходе  = 0. Так как вход А соединен с выходом

= 0. Так как вход А соединен с выходом  , то и А=0. После поступления тактового импульса на вход Т на выходах установится Q=0 и

, то и А=0. После поступления тактового импульса на вход Т на выходах установится Q=0 и  =l. На выходе А при поступлении следующего тактового импульса уже будет напряжение высокого уровня и произойдет очередная смена состояния.

=l. На выходе А при поступлении следующего тактового импульса уже будет напряжение высокого уровня и произойдет очередная смена состояния.

Рис. 15. Т-триггер на логических элементах И—НЕ: а — на четырех элементах; б — на двух элементах с RС-цепочками.

Работа Т-триггера характеризуется следующей таблицей состояний:

Смена состояния Т-триггера происходит после поступления на вход очередного импульса.

Т-триггер можно собрать из логических элементов И—НЕ.

У всех рассмотренных триггеров смена состояний происходит по фронту импульса. Существуют триггеры, для которых активным может быть срез (спад) импульса. В дальнейшем эти случаи будут специально оговариваться.

Установочные входы служат для предварительной установки триггера в одно определенное состояние. Это состояние может быть как нулевым, так и единичным. Поэтому обычно триггеры имеют два установочных входа, чтобы обеспечить обе возможности.

Литература:

1. М. Димитрова «33 схемы на триггерах», стр: 5-11, 19-28.

2. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования» стр: 82-90.

3. Э.В. Евреинов «Цифровая и вычислительная техника» стр: 97-109.

ЗАНЯТИЕ 1.1.3 Основные функции регистров: прием и хранение информации, передача информации из регистра в регистр, сдвиг информации.

ВОПРОСЫ ЗАНЯТИЯ:

1. Общие сведения о регистрах, классификация регистров.

2. Сдвигающие регистры.

3. Многорежимный буферный регистр.

ПЕРВЫЙ ВОПРОС.

При выполнении различных арифметических и логических операций возникает необходимость хранения кода числа в течении некоторого времени. Иногда нужно сдвинуть этот код вправо или влево, подсчитать количество импульсов, выбрать заданные комбинации кодов и т.п. такие операции выполняют специальные узлы цифровой техники: регистры, счетчики, дешифраторы.

Регистр – последовательное цифровое устройство, предназначенное для приема и хранения n-разрядного слова (кода), а также для выполнения определенных микроопераций над этим словом (кодом).

Элементами структуры регистров являются асинхронные и синхронные D-, RS- или JK-триггеры с динамическим или статическим управлением и вспомогательные логические элементы. Число разрядов в регистре называется его длиной. В n-разрядный регистр можно записать 2n разрядных слов, т.е. регистр может находиться в 2n различных состояниях.

Занесение информации в регистр называют операцией ввода или записи. Выдача информации к внешним устройствам характеризует операцию вывода или считывания.

Наиболее распространенными микрооперациями регистров являются:

1. установка исходного состояния (например, в ноль);

2. прием (запись) слова;

3. поразрядное логическое сложение двух слов;

4. поразрядное логическое умножение двух слов;

5. поразрядная сумма двух слов по модулю два;

6. сдвиг слова на j разрядов вправо или влево;

7. инвертирование разрядов слова;

8. выдача слова в прямом, обратном, парафазном кодах;

9. преобразование последовательного кода слова в параллельный и обратно.

Синтез регистров сводится к выбору типа триггеров и синтезу комбинационной схемы (на основе ЛЭ), формирующей функции возбуждения триггеров при выполнении заданных микроопераций.

Регистры используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки и т.п.

Основным классификационным признаком, по которому различают регистры, является способ записи информации или кода числа в регистр. По этому признаку можно выделить регистры трёх типов: параллельные, последовательные и параллельно-последовательные.

В параллельные регистры запись числа осуществляется параллельным кодом, т.е. во все разряды одновременно. Последовательные регистры характеризуются последовательной записью кода числа, начиная с младшего или старшего разряда, путем последовательного сдвига кода тактирующими импульсами. Регистры параллельно-последовательного типа имеют входы как для параллельной, так и для последовательной записи кода числа.

В зависимости от числа каналов по которым поступает (выводится) информация на входы(выходы) разрядов регистра, различают регистры парафазного и однофазного вида. Парафазные регистры характеризуются тем, что информация на каждый разряд поступает(выводится) по двум каналам (прямому и инверсному). В однофазных регистрах информация поступает (выводится) только по одному каналу (прямому или инверсному). Парафазные регистры выполняются, как правило, с применением RS-триггеров, а однофазные – на основе D-триггеров.

В зависимости от типов триггеров, применяемых для построения регистров, и способа их тактировки, различают регистры многотактного и однотактного действия.

В зависимости от типа выполняемых в регистре микроопераций различают следующие типы регистров:

- с параллельным приемом и выдачей информации (регистры памяти);

- с последовательным приемом и выдачей информации (регистры сдвига);

- с последовательным приемом и параллельной выдачей информации;

- с параллельным приемом и последовательной выдачей информации.

Регистры характеризуются числом разрядов и быстродействием, определяемым максимальной тактовой частотой приема, передачи и сдвига информации.

ВТОРОЙ ВОПРОС.

Сдвигающие регистры предназначены для выполнения операции сдвига слова информации, т. е. для перемещения всех цифр слова в направлении от старших к младшим разрядам (сдвиг вправо) или от младших к старшим разрядам (сдвиг влево). Сдвиг кода влево на один разряд будет соответствовать умножению кода числа на основание системы счисления, а сдвиг вправо — делению. Это объясняется тем, что вес каждого разряда кода для позиционной системы счисления определяется его позицией в коде.

В регистрах, как правило, сдвиг числа на k разрядов осуществляется за k тактов или за k микроопераций сдвига. Микрооперация сдвига — сдвиг числа на один разряд вправо или влево относительно принятой разрядной сетки.

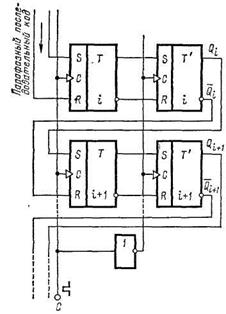

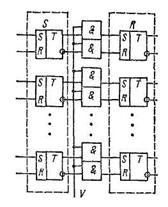

Сдвигающий регистр содержит такие же шины передачи по входам, как и регистры приема и передачи информации, но триггеры сдвигающих регистров обязательно должны быть сложными, свнутренним запоминанием. Если в сдвигающем регистре используются простые триггеры, например RS-триггеры, то необходимо использовать еще один дополнительный регистр для промежуточного запоминания слова в процессе сдвига. Фактически это приводит к тому, что каждый разряд регистра будет состоять из двух триггеров (рис. 1).

Рис. 1. Схема двух разрядов

сдвигающего регистра на RS-триггерах.

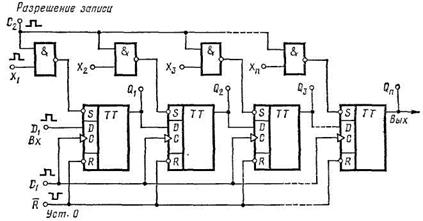

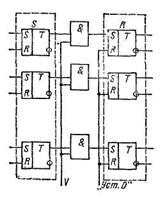

Сдвигающий регистр можно использовать не только для сдвига кода, но и для преобразования параллельного кода, принятого в регистр, в последовательный. Для этого достаточно принятый код сдвигать до тех пор, пока весь он не будет выдвинут из регистра. Выход из крайнего разряда используется в качестве выходной шины последовательного кода. Сдвигающий регистр может выполнять функцию также преобразования последовательного кода в параллельный, С точки зрения уменьшения количества связей и оборудования, сдвигающие регистры целесообразно строить на D-триггерах (рис. 2).

Рис. 2. Схема сдвигающего регистра на D-триггерах.

Установка этого регистра в состояние 0 выполняется отрицательным импульсом, подаваемым на вход R («Уст.0»). Параллельный код поступает на входы хi—хп. Запись параллельного кода осуществляется положительным импульсом, подаваемым на вход С1. Последовательный код поступает на вход D1.

Часто требуются более сложные сдвигающие регистры: с параллельной синхронной записью информации, реверсивные, реверсивные с параллельной синхронной записью информации. Такие регистры называют универсальными.

Примером сдвигающего регистра с синхронной записью информации является микросхема 155ИР1, выполненная на основе четырех RS-триггеров (рис. 3).

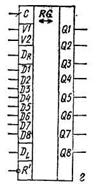

Рис. 3. Условное графическое обозначение

микросхемы К155ИР1.

Входы D1—D4 предназначены для параллельной записи информации, вход D для последовательной записи. Вход V является управляющим. При V = 0 схема работает как сдвигающий регистр по отрицательному перепаду (с 1 на 0) сигнала С1, а при V = 1 схема работает в режиме синхронной записи в регистр значений сигналов D1—D4 по отрицательному перепаду сигнала С2.

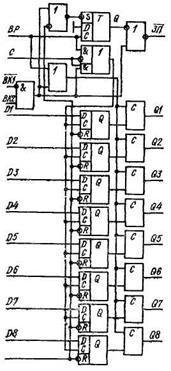

Микросхема 155ИР13 представляет собой восьмиразрядный реверсивный сдвигающий регистр с параллельной синхронной записью информации (рис. 4). При V1 = 0 и V2 = 1 происходит сдвиг информации вправо, при V1 = 1 и V2 = 0 — влево, а при V1 — V2 = 1 — запись информации в регистр. Асинхронный потенциальный вход R предназначен для установки нулевого состояния регистра. Входы DR и Dl служат для сдвига информации соответственно вправо и влево по перепаду синхроимпульсов С.

Рис. 4. Условное графическое обозначение

микросхемы К155ИР13.

ТРЕТИЙ ВОПРОС.

При построении интерфейса микропроцессорных устройств и других устройств с шинной организацией используются регистры памяти, выходные каскады которых, помимо состояний логического нуля и логической единицы, могут находиться в третьем состоянии. К таким регистрам относится, например, многорежимный буферный регистр К589ИР12, условное обозначение которого показано на рис. 3, а функциональная схема — на рис. 4. Это восьмиразрядный регистр на основе D-триггеров. Он имеет встроенную логику для управления режимами работы. Запись информации осуществляется по входам D1—D8, а выдача информации — по выходам Q1 — Q8. Управляющие входы ВК1 и ВК2 служат для выбора ИМС (выбор кристалла).

Рис. 5. Условное обозначение многорежимного

буферного регистра К589ИР12.

Выбор кристалла производится при единичном значении сигнала на входе ВК2 и нулевом значении сигнала на входе ВК1.

С — сигнал синхронизации, обеспечивающий формирование стробирующе-го сигнала на входах триггеров; ВР — сигнал выбора режима. При ВР — 1 стробирование осуществляется сигналом ВК,, а при ВР = О — сигналом С.

Выдача информации из регистра производится по сигналам ВК, или ВР.

Рис. 6. Функциональная схема многорежимного

буферного регистра K589ИP12.

Если выбор кристалла не производится (ВК = 0) и ВР = 0, С = 0, то происходит хранение информации. Выходы регистра при этом не нагружаются, что обеспечивается вентильными ИМС С, показанными на рис. 4. В нулевое состояние регистр устанавливается независимой подачей на вход  сигнала низкого логического уровня.

сигнала низкого логического уровня.

Многорежимный буферный регистр содержит дополнительные логические элементы, формирующие сигнал запроса прерывания ЗП. Этот сигнал информирует другие устройства о том, что им необходимо прервать свою работу и принять информацию, записанную в регистре. Принято считать, что сигнал ЗП= 1 (  = 0) свидетельствует о наличии информации в регистре и запроса на прерывание.

= 0) свидетельствует о наличии информации в регистре и запроса на прерывание.

Запрос на прерывание всегда происходит в течение действия сигнала выбора кристалла (ВК = 1) вне зависимости от состояния специального триггера. При записи информации по стробирующему сигналу С = 1 этот триггер устанавливается в нулевое состояние (  =l), свидетельствующее о наличии запроса на прерывание (ЗП = 1). После окончания стробирующего импульса С триггер своего состояния не изменяет и запрос на прерывание не прекращается.

=l), свидетельствующее о наличии запроса на прерывание (ЗП = 1). После окончания стробирующего импульса С триггер своего состояния не изменяет и запрос на прерывание не прекращается.

Установка специального триггера в единичное состояние, свидетельствующее об отсутствии запроса на прерывание, производится по входу S триггера.

Специальный триггер устанавливается в состояние, свидетельствующее об отсутствии запроса на прерывание, сигналом  = 0 очистки содержимого многорежимного буферного регистра.

= 0 очистки содержимого многорежимного буферного регистра.

Если установка специального триггера в единичное состояние произошла за счет сигнала ВК = 1 выбора кристалла, то в течение всего времени действия этого сигнала запрос прерывания (ЗП = 0) будет поддерживаться на выходе ИМС. Лишь после завершения действия сигнала выбора кристалла запрос на прерывание прекратится.

Литература:

1. В.В. Стрыгин «Основы вычислительной, микропроцессорной техники и программирования» стр: 92-95.

2. Э.В. Евреинов «Цифровая и вычислительная техника» стр: 109-112, 113-115, 118-122.

3. Б.Я. Лихтциндер «Микропроцессоры и вычислительные устройства в радиотехнике» стр: 65-69.

ЗАНЯТИЕ 1.1.4 Построение регистров приема и хранения информации.

ВОПРОСЫ ЗАНЯТИЯ:

1. Регистры памяти.

2. Передача информации из регистра в регистр.

3. Выполнение поразрядных операций в регистрах.

ПЕРВЫЙ ВОПРОС.

Регистры памяти — это устройства, предназначенные для записи, хранения и выдачи информации, представленной в виде двоичных кодов. Для хранения каждого двоичного разряда в регистре используется одна триггерная ячейка. Следовательно, для хранения n-разрядного двоичного кода регистр должен иметь п триггеров.

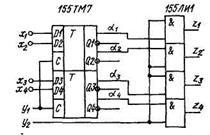

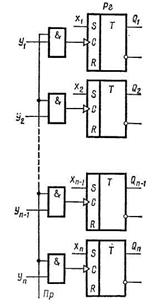

На рис. 1 показана схема четырехразрядного регистра памяти, выполненного на ИМС типов 155ТМ7 и 155ЛИ1.

Рис. 1. Схема четырехразрядного регистра

памяти с потенциальным управлением.

При подаче управляющего сигнала у1 = 1 информация по входам Х1—Х4 записывается в соответствующие разряды четырех D-триггеров (αi = xi). При у1 = у2 =0 информация хранится в регистре памяти, а при у2 = 1 происходит параллельное считывание информации (выходные сигналы zi = αiy2).

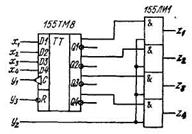

Для построения регистров памяти, управляемых спадом импульса, можно использовать синхронные D-триггеры, например ИМС типа 155ТМ8. Схема подобного четырехразрядного регистра изображена на рис. 2.

Рис. 2. Схема четырехразрядного регистра памяти

с управлением по спаду импульса.

Установка регистра в нулевое состояние осуществляется подачей сигнала у3, соответствующего уровню логического нуля. Информация хi , поступающая на каждый из входов регистра, передается на соответствующий выход Qi, в момент перехода тактирующего сигнала у1 изсостояния логической единицы в состояние логического нуля; при этом сигнал сброса у3 должен соответствовать уровню логической единицы (у3 = 1). При у2 = 1 происходит считывание информации, записанной в регистр (zi = Qi,). Этот регистр обладает лучшей помехозащищенностью по сравнению с рассмотренным ранее, так как запись информации в ИМС типа К155ТМ8 осуществляется лишь во время спада импульса y1.

ВТОРОЙ ВОПРОС.

Регистры находят применение при выполнении различных временных преобразований информации. Регистры сдвига используются в схемах умножения и деления: сдвиг числа влево или вправо на один разряд соответствует его умножению или делению на два. Регистры можно использовать для задержки передаваемой информации на п тактов. В сложных ПЦУ, состоящих из большого числа регистров, возникает необходимость передачи слов с одного регистра на другой. Это можно осуществить с помощью специальной микрооперации передачи слова. Два регистра соединяются друг с другом с помощью КЦУ, реализующего управляемую схему передачи. Передачу слова из регистра S в регистр R можно записать в виде микрооперации передачи R:=S.

Передача слова может осуществляться в парафазном и однофазном кодах. При парафазной передаче микрооперация передачи R:=S выполняется по сигналу управления V. По этому сигналу триггеры регистра R устанавливаются в состояния, соответствующие состояниям триггеров регистра S. При этом состояние регистра S не изменяется (рис. 3).

Рис. 3. Схема передачи информации из регистра

в регистр в парафазном коде.

Передачу слов между регистрами можно выполнять с помощью однофазного кода. В этом случае передача слова осуществляется в два такта. На первом также регистр R устанавливается в нулевое состояние, т. е. выполняется микрооперация «Установить 0» (R: = 0). По сигналу «Уст. 0» все триггеры регистра R переводятся в состояние 0. Во втором также выполняется микрооперация передачи R:=S (рис. 4).

Рис. 4. Схема передачи информации из регистра

в регистр в однофазном коде.

В этой схеме существенно экономится оборудование для реализации схемы передачи, однако при этом увеличивается время передачи информации.

Очень часто возникает необходимость передавать информацию с одного регистра ПЦУ на другой в обратном коде. Для выполнения микрооперации перадачи обратных кодов вида R:=S в схеме на рис. 3 нулевые и единичные выходы триггеров регистра при подключении к схеме передачи меняются местами или нулевые выходы триггеров регистра S подключаются к схеме передачи (рис. 4).

ТРЕТИЙ ВОПРОС.

Схема регистра для выполнения поразрядной операции сложения по модулю 2 показана на рис. 5.

Дата добавления: 2015-12-08; просмотров: 2444;