Запись в порт

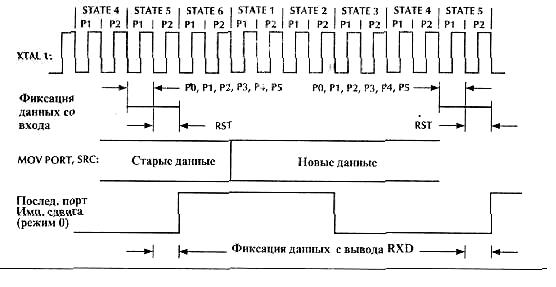

При выполнении инструкции, которая изменяет значение в защелке порта, новое значение записывается в защелку (рис. 2.2) в фазе State6.Phase2 последнего цикла команды (рис. 2.5). Однако, выходной буфер порта копирует значение защелки только в фазе Phase1 каждого такта периода (В фазе Phase2 выходные буферы поддерживают значение, зафиксированное во время предыдущей фазы - Phase1). Поэтому новое значение защелки появится на выходе порта только в фазе State1.Phase1 следующего машинного цикла.

Более полная информация приведена в разделе "Руководящие технические материалы CPU".

При переходе состояния защелки из "0" в "1", в портах Р1-Р5 на время фаз State1.Phase1 и State1.Phase2, открывается дополнительный pull-up транзистор (в цикле, в котором этот переход происходит). Это увеличивает скорость перехода. Дополнительный pull-up транзистор обеспечивает ток примерно в 100 раз больше, чем обычный pull-up транзистор. Внутренними pull-up транзисторами являются полевые транзисторы (нелинейные резисторы) — Схема pull-up элемента показана на рис. 2.4.

Pull-up элемент состоит из трех рМОП транзисторов Т1-Т3. Заметьте, что n-канальный МОП транзистор (nМОП) открывается когда к затвору приложена логическая "1"и запирается, когда к затвору приложен "0", р-канальный МОП (pМОП) транзистор работает наоборот.

Рис.2.5. Работа порта. Здесь обозначено: P1 – Phase1, P2 – Phase2

Транзистор Т1 открывается на 2 периода осциллятора(генератора) после перехода состояния защелки из "0" в "1". "1" на выводе порта через инвертор открывает транзистор ТЗ ( слабый pull-up транзистор). Инвертор и ТЗ образуют триггер, который удерживает состояние вывода в "1", после того как транзистор P1 закрывается.

Если вывод порта находится в "1", отрицательная помеха на этом выводе от некоторого внешнего источника способна запереть транзистор Т3, заставив вывод перейти в 3-е состояние. Для предотвращения подобной ситуации служит транзистор Т2 (очень слабый pull-up транзистор), который открывается всякий раз, когда транзистор n запирается, в традиционном CMOS (Complemantary Metal Oxyd Semiconductor) стиле. Его мощность составляет 1/10 часть от мощности транзистора Т3.

Порты Р1-Р5 являются 8-битовыми квазидвунаправленными портами ввода-вывода с мощным внутренним резистором, обеспечивающим быстрое установление на выходах портов логической "1". Резистор подключается к выходному каскаду на 2 периода тактового генератора для перевода вывода в данное состояние и затем отключается. Вывод данного порта, находящийся в состоянии логической "1", имеет высокий потенциал за счет внутреннего резистора и может использоваться в этом состоянии как вход. В отличие от порта 0, входные линии портов 1-5 снабжены входными триггерами Шмидта. Почти все выводы портов имеют альтернативное назначение (табл. 2.2). При сбросе выводы порта 3 устанавливаются в состояние "1", а все остальные - в "0".

Альтернативные функции выводов портов 0-5

Таблица 2.2

| Вывод порта | Обозначение | Альтернативная функция |

| Р0.0-Р0.7 | AD0-AD7 | Мультиплексированная шина адреса/данных |

| Р1.0 | Т2 | Вход тактирования Т/С 2, частотный выход |

| Р1.1 | Т2ЕХ | Управление Т/С 2 |

| Р1.2 | ЕС1 | Внешнее тактирование РСА |

| Р1.3 | СЕХ0 | Модуль 0 РСА. Вход фиксации. Выход сравнения, PWM |

| Р1.4 | СЕХ1 | Модуль 1 РСА. Вход фиксации. Выход сравнения, PWM |

| Р1.5 | СЕХ2 | Модуль 2 РСА. Вход фиксации. Выход сравнения, PWM |

| Р1.6 | СЕХЗ | Модуль 3 РСА. Вход фиксации. Выход сравнения, PWM |

| Р1.7 | СЕХ4 | Модуль 4 РСА. Вход фиксации. Выход сравнения, PWM |

| Р2.0-Р2.7 | А8-А15 | Старший байт адреса внешней памяти |

| РЗ.0 | RXD | Вход последовательного порта |

| Р3.1 | TXD | Выход последовательного порта |

| Р3.2 | INT0 | Внешнее прерывание 0 |

| РЗ.З | INT1 | Внешнее прерывание 1 |

| Р3.4 | Т0 | Вход тактирования Т/С0 |

| Р3.5 | Т1 | Вход тактирования Т/С1 |

| Р3.6 | WR | Строб записи в ВПД |

| Р3.7 | RD | Строб чтения из ВПД |

| Р4.0 | SEPCLK | Выход частоты для SEP |

| Р4.1 | SEPDAT | Вход/выход данных SEP |

| Р4.2 | ECU | Внешнее тактирование РСА1 |

| Р4.3 | С1ЕХ0 | Модуль 0 РСА 1. Вход фиксации. Выход сравнения, PWM |

| Р4.4 | С1ЕХ1 | Модуль 1 РСА 1. Вход фиксации. Выход сравнения, PWM |

| Р4.5 | С1ЕХ2 | Модуль 2 РСА 1. Вход фиксации. Выход сравнения, PWM |

| Р4.6 | С1ЕХЗ | Модуль 3 РСА 1. Вход фиксации. Выход сравнения, PWM |

| Р4.7 | С1ЕХ4 | Модуль 4 РСА 1. Вход фиксации. Выход сравнения, PWM |

| Р5.0 | - | |

| Р5.1 | - | |

| Р5.2 | INT2 | Внешнее прерывание 2 |

| Р5.3 | INT3 | Внешнее прерывание 3 |

| Р5.4 | INT4 | Внешнее прерывание 4 |

| Р5.5 | INT5 | Внешнее прерывание 5 |

| Р5.6 | INT6 | Внешнее прерывание 6 |

| Р5.7 | INT7 | Внешнее прерывание 6 |

Дата добавления: 2015-10-09; просмотров: 813;