Функционирование портов ввода-вывода

Все шесть портов в 8XC5IGB двунаправленные. Каждый из них состоит из регистра-защелки (SFRs Р0–Р5), выходного драйвера и входного буфера. Все порты, за исключением порта Р0, имеют на выходе триггер Шмидта. Выходные драйверы портов Р0 и Р2 и входные буферы порта PC используются аналогично рассмотренному базовому кристаллу. Если порты Р0 и Р1 не используются для обращения к внешней памяти, то выводы порта Р2 продолжают имитировать содержимое SFR P2.

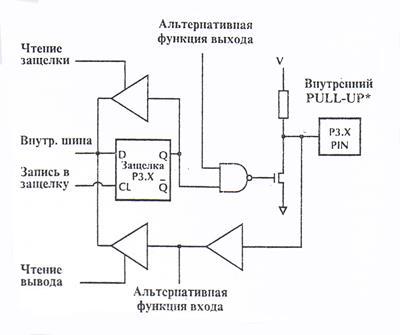

Все выводы портов Р1, РЗ, Р4 и большинство выводов порта Р5 многофункциональны (рис. 2.1, 2.2, 2.3, 2.4). Они не только являются выводами портов I/O, но и имеют альтернативные функции, которые приведены в табл. 2.2.

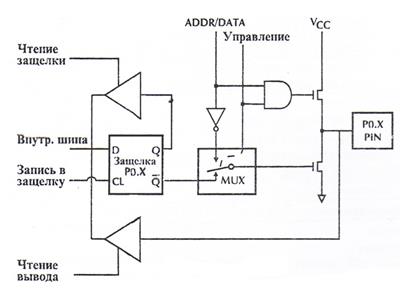

Рис. 2.1. Упрощенная схема одного разряда порта

Битовая защелка порта представлена в виде D-триггера. Данные с внутренней шины записываются в защелку по сигналу "запись в защелку". Выход "Q" D-триггерах подключается на внутреннюю шину в ответ на сигнал "чтение защелки". Непосредственное значение с вывода порта может быть считано на внутреннюю шину по сигналу "чтение порта". Некоторые команды чтения порта используют сигнал "чтение защелки", другие "чтение порта". Первые из них являются командами чтение-модификация-запись.

Рис. 2.2. Схема интерфейсной части одного разряда порта Р0

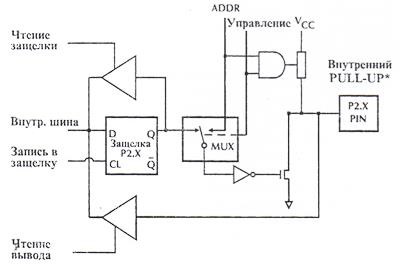

Рис. 2.3. Схема интерфейсной части одного разряда порта Р2

Рис. 2.4. Схема интерфейсной части одного разряда портов Р1, Р3, Р4 и Р5

Выходные драйверы портов Р0 и P2 могут подключаться к внутренней шине ADDRESS и ADDRESS/DATA благодаря внутреннему сигналу управления при обращениях к внешней памяти. Во время доступа к внешней памяти, содержимое защелок порта Р2 не изменяется, а в защелки порта Р0 предварительно записываются "1".

Если защелки портов Р1, Р3, Р4, Р5 содержат "1", то выходные уровни могут управляться сигналом "альтернативная функция выхода". Уровень сигнала, присутствующий на выводе порта всегда доступен альтернативной функции входа.

Порты Р1-Р5 имеют внутренние подтягивающие pull-up элементы, подключенные к источнику питания. Выходы порта Р0 являются выходами с открытым стоком. Каждая линия порта может быть индивидуально использована как вход или как выход (Порты Р0 и Р2 не могут быть использованы как порты I/О общего назначения, если они используются как шина ADDRESS/DATA). Чтобы настроиться на вход, защелка должна содержать "1", которая запирает выходной pull-down транзистор. Высокий уровень на выводах порта P1-P5 поддерживается внутренним pull-up элементом, однако мощный внешний источник может принудительно установить вывод в логический "0".

При сбросе, порты P1, Р2, Р4 и Р5 устанавливаются в низкое состояние. В это время выводы этих портов могут потреблять большой ток. Если во время сброса они используются как входы и управляются извне высоким уровнем, то пользователю необходимо использовать интерфейс с открытым коллектором или буферизовать входы (запомнить значения входов).

Порт Р0 отличается от других тем, что не имеет внутренних pull-up элементов. Транзистор, выполняющий роль pull-up элемента в выходном драйвере, открыт только тогда, когда вывод имитирует "1" при обращениях к внешней памяти. В любом другом случае транзистор заперт. Поэтому линии порта Р0, которые используются как выходы, являются выходами с открытым стоком. Запись "1" в защелку оставляет pull-down транзистор запертым и переводит вывод в высокоимпедансное состояние, что позволяет использовать его в качестве высокоомного входа. Так как порты P1-P5 имеют фиксированные внутренние pull-up элементы, их называют квазидвунаправленными портами.

Когда порты P1-P5 настроены на вход (pull-down транзистор зарыт), они поддерживают на выходе высокий уровень. При установке внешним источником низкого уровня, порты становятся источниками тока (I1L). Когда порт Р0 настроен на вход, его выходы находятся в высокоимпендансном состоянии, поэтому его называют двунаправленным.

Во время сброса в защелки портов Р0 и РЗ записываются "1", Если впоследствии в защелку записывается "0", порт можно переустановить на вход путем записи в него "1".

Дата добавления: 2015-10-09; просмотров: 1073;