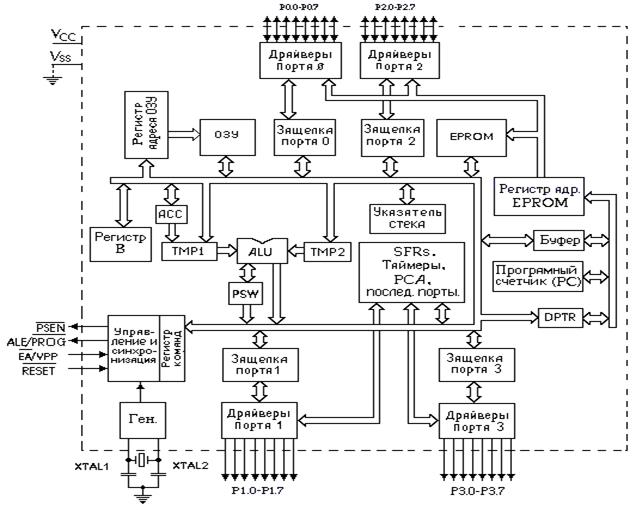

Структурная схема

Структурная схема контроллера представлена на рис.1.1 и состоит из следующих основных функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, блока последовательного интерфейса и прерываний, программного счетчика, памяти данных и памяти программ. Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. По такой схеме построены практически все представители семейства MCS-51. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов).

Блок управления и синхронизации (Timing and Control) - предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков ОЭВМ во всех допустимых режимах ее работы. В состав блока управления входят:

устройство формирования временных интервалов;

логика ввода-вывода;

регистр команд;

регистр управления потреблением электроэнергии;

дешифратор команд, логика управления ЭВМ.

Рис. 1.1. Структурная схема контроллера I8051.

Устройство формирования временных интервалов предназначено для формирования и выдачи внутренних синхросигналов фаз, тактов и циклов. Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды ОЭВМ выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Обозначим частоту задающего генератора через Fг. Длительность машинного цикла равна 12/Fг или составляет 12 периодов сигнала задающего генератора. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода Р0-Р3.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды.

Регистр управления потреблением (PCON) позволяет останавливать работу микроконтроллера для уменьшения потребления электроэнергии и уменьшения уровня помех от микроконтроллера. Еще большего уменьшения потребления электроэнергии и уменьшения помех можно добиться, остановив задающий генератор микроконтроллера. Этого можно достичь при помощи переключения бит регистра управления потреблением PCON. Для варианта изготовления по технологии n-МОП (серия 1816 или иностранных микросхем, в названии которых в середине отсутствует буква 'c') регистр управления потреблением PCON содержит только один бит, управляющий скоростью передачи последовательного порта SMOD, а биты управления потреблением электроэнергией отсутствуют.

Арифметико-логическое устройство (ALU) представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛУ состоит из:

регистров аккумулятора, регистров временного хранения TMP1 и TMP2;

ПЗУ констант;

сумматора;

дополнительного регистра (регистра В);

аккумулятора (ACC);

регистра состояния программ (PSW).

Регистр аккумулятор и регистры временного хранения - восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Эти регистры программно не доступны.

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Параллельный восьмиразрядный сумматор представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций сложения, умножения, неравнозначности и тождественности.

Регистр B - восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный сверхоперативный регистр.

Аккумулятор - восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига

Блок последовательного интерфейса и прерываний (ПИП) предназначен для организации ввода - вывода последовательных потоков информации и организации системы прерывания программ. В состав блока входят:

буфер ПИП;

логика управления;

регистр управления;

буфер передатчика;

буфер приемника;

приемопередатчик последовательного порта;

регистр приоритетов прерываний;

регистр разрешения прерываний;

логика обработки флагов прерываний и схема выработки вектора.

Счетчик команд (Program Counter) предназначен для формирования текущего 16-разрядного адреса внутренней памяти программ и 8/16-разрядного адреса внешней памяти программ. В состав счетчика команд входят 16-разрядные буфер РС, регистр РС и схема инкремента (увеличения содержимого на 1).

Память данных (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы.

Порты P0, P1, P2, P3 являются квазидвунаправленными портами ввода - вывода и предназначены для обеспечения обмена информацией ОЭВМ с внешними устройствами, образуя 32 линии ввода- вывода.

Регистр состояния программы (PSW) предназначен для хранения информации о состоянии АЛУ при выполнении программы.

Память программ (EPROM) предназначена для хранения программ и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах применяются масочные, стираемые ультрафиолетовым излучением или FLASH ПЗУ.

Регистр указателя данных (DPTR) предназначен для хранения 16 - разрядного адреса внешней памяти данных.

Указатель стека (SP) представляет собой восьмиразрядный регистр, предназначенный для организации особой области памяти данных (стека), в которой можно временно сохранить любую ячейку памяти.

1.3 Назначение выводов микроконтроллера 8051 (рис. 1.2)

· Uss — потенциал общего провода ("земли");

· Ucc — основное напряжение питания +5 В;

· X1,X2 — выводы для подключения кварцевого резонатора;

· RST — вход общего сброса микроконтроллера;

· PSEN — разрешение внешней памяти программ, выдается только при обращении к внешнему ПЗУ;

· ALE — строб адреса внешней памяти;

· ЕА — отключение внутренней программной память; уровень 0 на этом входе заставляет микроконтроллер выполнять программу только из внешнего ПЗУ; игнорируя внутреннее(если последнее имеется);

Рис. 1.2. Назначение выводов 8051.

· P1 — восьмибитный квазидвунаправленный порт ввода/вывода, каждый разряд порта может быть запрограммирован как на ввод, так и на вывод информации, независимо от состояния других разрядов;

· P2 — восьмибитный квазидвунаправленный порт, аналогичный Р1, выводы этого порта используются для выдачи адресной информации при обращении к внешней памяти программ или данных (если используется 16-битовая адресация последней). Кроме того, выводы порта используются при программировании для ввода в микроконтроллер старших разрядов адреса;

· РЗ — восьмибитный квазидвунаправленный порт, аналогичный Р1, выводы этого порта могут выполнять ряд альтернативных функций, которые используются при работе таймеров, порта последовательного ввода-вывода, контроллера прерываний, и внешней памяти программ и данных;

· P0 — мультиплексируемый восьмибитный двунаправленный порт ввода-вывода информации, через этот порт в разные моменты времени выводятся младший байт адреса и данные.

Дата добавления: 2015-10-09; просмотров: 1097;