АДРЕСНАЯ ПАМЯТЬ

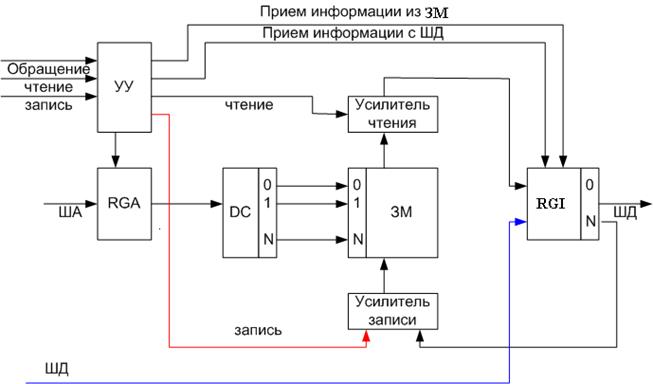

В такой памяти размещение и поиск информации в ЗУ основаны на использовании адреса байта или слова. Адресом служит порядковый номер ячейки ЗМ, в которой это слово размещается. Структурная схема адресной памяти объемом N n-разрядных слов имеет следующий вид

При каждом обращении к ЗУ необходимо указывать номер (адрес) ячейки памяти, в которой размещается нужная информация. Для приема адреса А служит регистр адреса RGA. Этот адрес дешифруется дешифратором адреса DC, который формирует сигнал на одном из своих выходов. При этом номер этого выхода равен самому адресу А. Таким образом, дешифратор DC указывает номер ячейки памяти, к которой происходит обращение. При чтении информации из ЗУ устройство управления формирует управляющий сигнал «чтение», под действием которого прочитанное из ЗУ слово поступает в усилители чтения, а оттуда в регистр информации RGI.

Занесение прочитанного слова в RGI происходит под действием управляющего сигнала “Прием информации из ЗМ”. Аналогично происходит запись информации в ЗМ. При этом записываемое слово поступает с ШD в регистр RGI, а оттуда через усилитель записи под действием сигнала «запись» в выбранную ячейку ЗМ. Любой цикл обращения к памяти инициируется поступлением сигнала «обращение». На УУ поступают также сигналы «чтение» и «запись», которые указывают вид выполняемой в ЗУ операции (запись или чтение).

Для построения адресной памяти используются микросхемы памяти, в состав которых кроме ЗМ входят также усилители чтения и записи, а также дешифратор памяти.

Дата добавления: 2015-08-14; просмотров: 1831;