Раздел 2. Машинно-зависимые свойства операционных систем

Тема 2.1. Архитектурные особенности модели микропроцессорной системы

Упрощенная архитектура типовой ЭВМ. Структура оперативной памяти. Адресация. Основные регистры. Форматы данных и команд. Операционная система как средство управления ресурсами типовой ЭВМ

Основные регистры процессора Регистры – это ячейки внутренней быстродействующей памяти микропроцессора. Они используются для временного хранения единицы информации (машинного слова) при прохождении данных через блок микропроцессора. В реальных микропроцессорах количество регистров может быть разным. Количество допустимой в системе оперативной памяти определяется регистром адреса. Количество регистров в реальных микропроцессорах может отличаться, но 8 типов регистров присутствуют всегда: 1. Аккумулятор – является промежуточной памятью при выполнении арифметических и логических операций в АЛУ. Любая из операций над двумя байтами предполагает размещение одного из них в аккумуляторе. Результат обычно помещается туда же. Может использоваться для изменения (инвертирования, сдвига). Доступен программисту. 2. Буферные регистры - используются для накопления исходных данных с шины. Недоступны. 3. Регистр состояния – каждый разряд этого регистра устанавливается в 0 или 1, если происходит определенное событие. Например, в результате получился 0 или отрицательное число. Доступен для просмотра и из команд. 4. Счетчик команд – содержит адрес ячейки памяти, в которой содержится следующая команда программы. Недоступен.5. Регистр команд – содержит команду, которую нужно выполнять на определенном шаге. Недоступен. 6. Регистр адреса – содержит адрес той команды программы, которая выполняется сейчас. Недоступен. 7. Указатель стека – содержит адрес вершины стека. 8. Регистры общего назначения – доступны программисту и предназначены для временного хранения данных. Процессоры «Мозгом» компьютера является центральный процессор (CPU — Central Processing Unit). Он выбирает из памяти команды и выполняет их. Обычный цикл работы центрального процессора выглядит так: он читает первую команду из памяти, декодирует ее для определения ее типа и операндов, выполняет команду, затем считывает, декодирует и выполняет последующие команды. Для каждого центрального процессора существует набор команд, который он в состоянии выполнить. Например, процессор Pentium не может обработать программы, написанные для SPARC, а процессор SPARC не может выполнить программы, написанные для Pentium. Поскольку доступ к памяти для получения команд или наборов данных занимает намного больше времени, чем выполнение этих команд, все центральные процессоры содержат внутренние регистры для хранения ключевых переменных и временных результатов. Кроме основных регистров, используемых для хранения переменных и временных результатов, большинство компьютеров имеет несколько специальных регистров, видимых для программиста. Один из них называется счетчиком команд (PC, program counter), в нем содержится адрес следующей, стоящей в очереди на выполнение команды. После того как команда выбрана из памяти, регистр команд корректируется и указатель переходит к следующей команде. Еще один регистр процессора называется указателем стека (SP, stack pointer). Он содержит адрес вершины стека в памяти. Стек содержит по одному фрейму (области данных) для каждой процедуры, которая уже начала выполняться, но еще не закончена. В стековом фрейме процедуры хранятся ее входные параметры, а также локальные и временные переменные, не хранящиеся в регистрах.Следующий регистр называется PSW (Processor Status Word — слово состояния процессора). Этот регистр содержит биты кода состояний, которые задаются командами сравнения, приоритетом центрального процессора, режимом (пользовательский или режим ядра), и другую служебную информацию. Операционная система должна знать все обо всех регистрах. При временном мультиплексировании центрального процессора операционная система часто останавливает работающую программу для запуска (или перезапуска) другой. Каждый раз при таком прерывании операционная система должна сохранять все регистры процессора, чтобы позже, когда программа продолжит свою работу, их можно было восстановить. В целях улучшения характеристик центральных процессоров их разработчики давно отказались от простой модели, в которой за один такт может быть считана, декодирована и выполнена только одна команда. Многие современные CPU обладают возможностями выполнения нескольких команд одновременно. Например, у процессора могут быть раздельные модули, занимающиеся выборкой, декодированием и выполнением команд, и во время выполнения команды с номером п он может декодировать команду с номером n + 1 и считывать команду с номером п + 2. Подобная организация процесса называется конвейером, три его стадии продемонстрированы на рис. а. Часто встречаются и более длинные конвейеры. В большинстве конвейерных конструкций считанная команда должна быть выполнена, даже если в предыдущей команде был принят условный переход.

Структура оперативной памяти. Форматы данных и команд.

Структура оперативной памяти

ОП состоит из ячеек, в каждой из которых может находиться единица информации – машинное слово. Каждая ячейка имеет две характеристики: адрес и содержимое. Через регистр адреса микропроцессора можно обратиться к любой ячейке памяти. Количество ячеек памяти зависит от разрядности регистра адреса:

К=2n,

Где К – количество ячеек памяти, n – разрядность регистра адреса.

Например, имея 8-ми разрядный регистр адреса можно адресовать 256 ячеек памяти. Если принять, что машинное слово – 1 байт, то следовательно максимальная оперативная память не может превышать 256 байт.

Посчитайте, с ОП какого максимального размера может работать МП, если регистр адреса 16-разрядный и машинное слово – 1 байт.

Ответ - 64 Кбайта

А если регистр адреса – 32 разрядный и машинное слово – байт?

Ответ – 4 Гб.

Иначе говоря, 32 разрядный МП может адресовать 1 Гб ОП.

Формат команд и методы адресации

Команды 32-разрядных процессоров содержат одно- или двухбайтный код инструкции, за которым могут следовать несколько байт, определяющих режим исполнения команды, и операнды. Команды могут использовать до трех операндов (или ни одного). Операнды – данные для выполнения команды. Например, команда сложения должна содержать 2 операнда – 2 числа, которые нужно просуммировать.

Операнды могут находиться в памяти, регистрах процессора или непосредственно в команде.

Если операнд находится в команде (задан константой), то такая адресация данных называется непосредственной.

При прямой (регистровой) адресации операнд находится в каком-либо регистре процессора, а в теле команды указывается имя этого регистра. При косвенной адресации операнд находится в ячейке ОП, а адрес этой ячейки содержится в регистре, указанном в команде.

Примеры:

1. Add R1,28

На то, какой именно метод адресации используется, указывают старшие два двоичных разряда операнда.

Тема 2.2. Обработка прерываний

Электр.пособие- Основы информатики и программирования под Windows. К.А.Молоков,2007г.

(Роль прерываний ЭВМ при запуске системы. Порядок выполнения любого прерывания-стр.70)

Понятие прерывания. Последовательность действий при обработке прерываний. Классы прерываний. Рабочая область прерываний. Вектор прерывания. Стандартные программы обработки прерываний. Приоритеты прерываний. Вложенные прерывания

Прерывания подразделяются на аппаратные (маскируемые и немаскируемые), вызываемые электрическими сигналами на входах процессора, и программные, выполняемые по команде INT xx. Программные прерывания, строго говоря, прерываниями не являются — это лишь своеобразный способ вызова процедур, но процессором они обрабатываются как разновидность прерываний.

Прерывания и исключения нарушают нормальный ход выполнения программы для обработки внешних событий или сообщения о возникновении особых условий или ошибок.

Аппаратные прерывания подразделяются на маскируемые и немаскируемые. Процессор может воспринимать прерывания после выполнения каждой команды, длинные строковые команды имеют для восприятия прерываний специальные окна. Аппаратные прерывания вызываются электрическими сигналами на входах INTR и NMI.

Маскируемые прерывания вызываются переходом в высокий уровень сигнала на входе INTR (Interrupt Request) при установленном флаге разрешения (IF=1). В этом случае процессор сохраняет в стеке регистр флагов, сбрасывает флаг IF и вырабатывает два следующих друг за другом (back to back) цикла подтверждения прерывания, в которых генерируются управляющие сигналы INTA# (Interrupt Acknowledge). Высокий уровень сигнала INTR должен сохраняться по крайней мере до подтверждения прерывания. Первый цикл подтверждения холостой, по второму импульсу внешний контроллер прерываний передает по шине номер вектора, обслуживающего данный тип аппаратного прерывания. Прерывание с полученным номером вектора выполняется процессором так же, как и программное. Обработка текущего прерывания может быть в свою очередь прервана немаскируемым прерыванием, а если обработчик установит флаг IF, то и другим маскируемым аппаратным прерыванием.

Немаскируемые прерывания выполняются независимо от состояния флага IF по сигналу NMI (Non Mascable Interrupt). Высокий уровень на этом входе вызовет прерывание с типом (вектором) 2, которое выполняется так же, как и маскируемое. Его обработка не может прерываться под действием сигнала на входе NMI до выполнения команды IRET.

В защищенном режиме, помимо перечисленных видов прерываний существуют так называемые исключения (exceptions). Исключение происходит в результате нештатной ситуации выполнения программы, которую возможно необходимо обработать определенным образом. Исключения подразделяются на отказы, ловушки и аварийные завершения.

Отказ (fault) — это исключение, которое обнаруживается и обслуживается до выполнения инструкции, вызывающей ошибку. После обслуживания этого исключения управление возвращается снова на ту же инструкцию (включая все префиксы), которая вызвала отказ. Отказы, использующиеся в системе виртуальной памяти, позволяют, например, подкачать с диска в оперативную память, затребованную страницу или сегмент.

Ловушка (trap) — это исключение, которое обнаруживается и обслуживается после выполнения инструкции, его вызывающей. После обслуживания этого исключения управление возвращается на инструкцию, следующую за вызвавшей ловушку. К классу ловушек относятся и программные прерывания.

Аварийное завершение (abort) - это исключение, которое не позволяет точно установить инструкцию, его вызвавшую. Оно используется для сообщения о серьезной ошибке, такой как аппаратная ошибка или повреждение системных таблиц.

Тема 2.3. Планирование процессов

Понятия: задание, процесс, планирование процесса. Состояния существования процесса. Диспетчеризация процесса. Блок состояния процесса. Алгоритм диспетчеризации. Способ выбора процесса для диспетчеризации. Понятие события. Блок состояния события. Механизм установления соответствия между процессом и событием

Уровни планирования

Планирование использования процессора применяется в качестве краткосрочного планирования процессов. Оно проводится, к примеру, при обращении исполняющегося процесса к устройствам ввода-вывода или просто по завершении определенного интервала времени. Поэтому краткосрочное планирование осуществляется, как правило, не реже одного раза в 100 миллисекунд. Выбор нового процесса для исполнения оказывает влияние на функционирование системы до наступления очередного аналогичного события, т. е. в течение короткого промежутка времени, чем и обусловлено название этого уровня планирования – краткосрочное.

В некоторых вычислительных системах бывает выгодно для повышения производительности временно удалить какой-либо частично выполнившийся процесс из оперативной памяти на диск, а позже вернуть его обратно для дальнейшего выполнения. Эта процедура называется swapping. Когда и какой из процессов нужно перекачать на диск и вернуть обратно, решается дополнительным промежуточным уровнем планирования процессов – среднесрочным.

Критерии планирования и требования к алгоритмам

Выбор конкретного алгоритма определяется классом задач, решаемых вычислительной системой, и целями, которых мы хотим достичь, используя планирование. К числу таких целей можно отнести следующие:

Справедливость – гарантировать каждому заданию или процессу определенную часть времени использования процессора в компьютерной системе, стараясь не допустить возникновения ситуации, когда процесс одного пользователя постоянно занимает процессор, в то время как процесс другого пользователя фактически не начинал выполняться.

Эффективность – постараться занять процессор на все 100% рабочего времени, не позволяя ему простаивать в ожидании процессов, готовых к исполнению. В реальных вычислительных системах загрузка процессора колеблется от 40 до 90%.

Сокращение полного времени выполнения (turnaround time) – обеспечить минимальное время между стартом процесса или постановкой задания в очередь для загрузки и его завершением.

Сокращение времени ожидания (waiting time) – сократить время, которое проводят процессы в состоянии готовность и задания в очереди для загрузки.

Сокращение времени отклика (response time) – минимизировать время, которое требуется процессу в интерактивных системах для ответа на запрос пользователя.

Независимо от поставленных целей планирования желательно также, чтобы алгоритмы обладали следующими свойствами.

Были предсказуемыми. Одно и то же задание должно выполняться приблизительно за одно и то же время. Применение алгоритма планирования не должно приводить, к примеру, к сортировке массива за сотые доли секунды при одном запуске и за несколько суток – при втором запуске.

Были связаны с минимальными накладными расходами. Если на каждые 100 миллисекунд, выделенные процессу для использования процессора, будет приходиться 200 миллисекунд на определение того, какой именно процесс получит процессор в свое распоряжение, и на переключение контекста, то такой алгоритм, очевидно, применять не стоит.

Равномерно загружали ресурсы вычислительной системы, отдавая предпочтение тем процессам, которые будут занимать малоиспользуемые ресурсы.

Обладали масштабируемостью, т. е. не сразу теряли работоспособность при увеличении нагрузки. Например, рост количества процессов в системе в два раза не должен приводить к увеличению полного времени выполнения процессов на порядок.

Многие из приведенных выше целей и свойств являются противоречивыми. Улучшая работу алгоритма с точки зрения одного критерия, мы ухудшаем ее с точки зрения другого. Приспосабливая алгоритм под один класс задач, мы тем самым дискриминируем задачи другого класса.

Параметры планирования

Для осуществления поставленных целей разумные алгоритмы планирования должны опираться на какие-либо характеристики процессов в системе, заданий в очереди на загрузку, состояния самой вычислительной системы, иными словами, на параметры планирования. В этом разделе мы опишем ряд таких параметров, не претендуя на полноту изложения.

Все параметры планирования можно разбить на две большие группы: статические параметры и динамические параметры. Статические параметры не изменяются в ходе функционирования вычислительной системы, динамические же, напротив, подвержены постоянным изменениям.

Тема 2.4. Обслуживание ввода-вывода

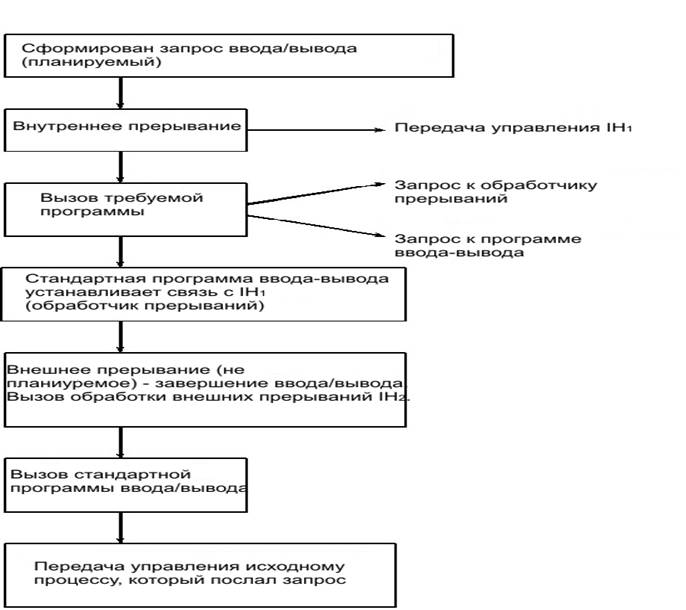

На многих ЭВМ пользовательский процесс (проблемная задача) запрашивает обслуживание ввода/вывода посредствам команды вызова супервизора (SVC) (планируемое прерывание), т.е. инструкция "ввод".

Эта команда приводит к внутреннему прерыванию и передаче управления обработчику прерываний SVC (IH1).

Обработчик прерываний SVC будет вызывать требуемую программу ввода/вывода или процесс, "будить" его или посылать сообщение (например, вставкой в очередь).

При этом:

а) элементы запроса должны быть переданы из пользовательского

процесса обработчику прерываний SVC для того, чтобы:

- он нашел правильную стандартную программу ввода/вывода;

б) элементы запроса должны быть переданы программе ввода/вывода

так, чтобы:

- была определена правильная команда ввода/вывода.

Стандартная программа ввода/вывода в свою очередь должна передавать свой идентификатор (помещая его в некоторую заранее известную ячейку памяти) обработчику прерываний.

По окончании работы устройства - внешнее прерывание, сигнализирующее о завершении операции ввода/вывода, вызывает обработчик прерываний (IH2).

Этот обработчик определит необходимый процесс ввода/вывода (стандартную программу), которую нужно вызвать ("разбудить").

Стандартная программа ввода/вывода может вернуть или послать сигнал пробуждения обработчику прерываний SVC, который, в конце концов, передает управление исходному запрашивающему процессу.

На рисунке приведены блок-схема обслуживания ввода-вывода.

Тема 2.5. Управление реальной памятью

Механизм разделения центральной памяти. Разделение памяти на разделы. Распределение памяти с разделами фиксированного размера. Распределение памяти с разделами переменного размера. Аппаратные и программные средства защиты памяти. Способы защиты памяти. Проблема фрагментации памяти и способы ее разрешения

Дата добавления: 2015-07-14; просмотров: 2960;