Задача (ТБС)

Определить вторичные параметры коаксиального кабеля антенно-фидерного тракте BTS системы мобильной радиосвязи в направлении Down Link стандарта GSM-1800, если известные следующие данные:  ,

,  , D=1,5 мм,

, D=1,5 мм,  ,

,  ,

,  ,

,  . Тип изоляции - сплошная полиэтиленовая, тип проводника-медь

. Тип изоляции - сплошная полиэтиленовая, тип проводника-медь

Многопозиционная модуляция: nФМ, квадратурная амплитудная модуляция (КАМ) и амплитудно-фазовая модуляция (АФМ)

Многопозиционная фазовая модуляция.

Как было показано ранее, скорость модуляции в канале определяется шириной спектра канала:

Канал ТЧ имеет спектр 0,3 - 3,4 к Гц. D Fтч =3,1 к Гц.

Таким образом, максимальная скорость модуляции, которую теоретически можно достичь в кТЧ 6,2 Бод (передача одной боковой) 3,1 кБод (при передаче двух боковых).Реально же в модемах используются скорости модуляции обычно 1200 и 2400 Бод.Если для передачи использовать двухпозиционный сигнал, то скорость передачи информации будет такой же низкой R=B=2400 Бит/сек.Такие скорости сегодня не устраивают потребителя.Выходом в данном случае является использование сигналов переносящих более чем 1 бит информации (то есть многопозиционных сигналов).Многопозиционный сигнал имеет более чем две значащих позиции

| Число значащих позиций | информационная емкость элемента |

| 1 бит | |

| 2 бит | |

| 3 бит |

Применение данного принципа к относительно фазовой модуляции называется многопозиционной ОФМ.

Рассмотрим простейший случай Двукратная ОФМ.

двукратная или четырехпозиционная.

При ДОФМ два соседних сигнала могут отличаться по фазе на одно из четырех возможных значений.

| Дибит | ||||

|

Первоначально исходная последовательность разбивается на дибиты (по 2 элемента), а затем каждый дибит кодируется на единичном интервале в соответствии с модуляционным кодом.

В данном случае обеспечивается R=2B.

Диаграмма ДОФМ на сигнальной плоскости выглядит так.

Протокол V. 22.

B = 600 Бод. В режиме ОФМ - 600 бит/с. В режиме ДОФМ - 1200 бит/с.

Еще более повысить скорость R можно используя:

трехкратную (восьмипозиционную) или четырехкратную (шестнадцати позиционную ) модуляции.

Однако при увеличении числа разрешенных сдвигов фаз резко уменьшается помехоустойчивость ОФМ.

Уменьшается расстояние между разрешенными сигналами в пространстве. Вследствие этого, ОФМ кратностью более трех не используется.

Для большего увеличения скорости передачи используют амплитудно-фазовую или так называемую квадратурную - амплитудную модуляцию КАМ.

В КАМ изменяется не только фаза, но и амплитуда. На рисунке показана диаграмма КАМ – 16.

Использование КАМ - 16 позволяет при скорости модуляции 2400 Бод,

получать скорость передачи информации 2400 ´ 4 = 9600 бит/с.

Такая модуляция используется в протоколе

V. 32, R до 9600 в.p.s.

Квадратурная модуляция имеет большую помехоустойчивость в сравнении с многократной ОФМ. Но при увеличении числа позиций свыше 16 и ее помехоустойчивость оказывается недостаточно для качественной передачи.

Поэтому во всех современных высокоскоростных протоколах КАМ используется, в совокупности с помехоустойчивым кодированием.

В качестве ПУ кодирования используется один из видов сверточных кодов - решетчатый код. Такое совместное кодирование получило название “Треллис - модуляции” (ТСМ).

При применении Треллис - модуляции число сигнальных точек увеличивается вдвое за счет добавления к информационным битам одного избыточного, образованного путем сверточного кодирования.

Треллис - модуляция используется уже в протоколе V. 32, как альтернатива КАМ - 16. В этом случае к 4 информационным добавлениям 1 проверочный разряд. Получается 32 точки из которых выбирается 16 разрешенных. Треллис – модуляция обеспечивает большую помехоустойчивость.

Треллис - модуляции используется в более поздних протоколах

V. 32 bis - 14.4 b p.s. V.34 bis - 28.8 b p.s.

Напряжение полевого транзистора сток-исток UСИ0 = 6В, затвор-исток UЗИ0 = 4 В.

1. По его выходной характеристике построить передаточную характеристику при указанном напряжении стока. По этим характеристикам определить дифференциальное сопротивление и крутизну полевого транзистора.

Кратко так, полное решение в тетради

2. D - Триггер. Схема. Обозначения входов и выходов. Работа четырехразрядного ассинхронного триггера.

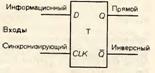

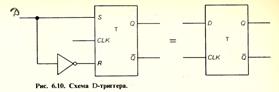

6.3. D-триггер Условное графическое обозначение D-триггера показано на рис. 6.9, а. У этого триггера имеется только один информа- информационный вход D, а также синхронизирующий вход CLK.

Выходы по-прежнему обозначаются Q и Q. D-триггер часто называют триггером с задержкой. Слово «задержка» здесь характеризует то, что происходит с данными (информа- (информацией), поступающими на вход D. Информационный сигнал @ или 1), поступающий на этот вход, задерживается в триг- триггере ровно на один такт1'*, прежде чем появляется на выхо- выходе Q. Упрощенная таблица истинности для D-триггера при-ведена на рис. 6.9,6. Обратите внимание, что сигнал на выходе Q в такте п + 1 (см. столбец Q" + ) повторяет сигнал, который был на входе D в предыдущем такте п. D-триггер можно получить из тактируемого RS-триггера, добавляя к последнему инвертор, как это показано на рис. 6.10. Чаще всего вам, вероятно, придется использовать D-триггеры, выполненные в виде монолитных ИС. На рис. 6.11, а пока- показано условное графическое обозначение типичного герийно выпускаемого интегрального D-трипера. Этот триггер имеет два дополнительных входа-предварительной уста- установки (PS) и очистки {CLRI]. Логический 0 на входе PS инициирует установку логической 1 на выходе Q. Логиче- Логический 0 на входе CLR инициирует очистку выхода Q (уста- (установку логического 0 на выходе Q). В активных состояниях входы PS и CLR блокируют действие входов D и CLK2); при разблокировании входы D и CLK действуют точно так же, как в обычном D-триггере, изображенном на рис. 6.9.Соединяя D-триггеры друг с другом, получают сдви- сдвиговые регистры и регистры хранения. Эти регистры широко используются в цифровых системах. Итак, запомните, что D-триггер задерживает поступление информационного сиг-нала на выход Q на один такт и называется триггером с задержкой.

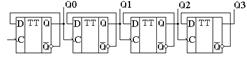

Схема счётчика, позволяющего посчитать любое количество импульсов, меньшее шестнадцати, приведена на рисунке 3. Количество поступивших на вход импульсов можно узнать, подключившись к выходам счётчика Q0 … Q3. Это число будет представлено в двоичном коде.

Рисунок 3 Схема четырёхразрядного счётчика, построенного на универсальных D-триггерах.

Для того чтобы разобраться, как работает схема двоичного счётчика, воспользуемся временными диаграммами сигналов на входе и выходах этой схемы, приведёнными на рисунке 4.

Для того чтобы разобраться, как работает схема двоичного счётчика, воспользуемся временными диаграммами сигналов на входе и выходах этой схемы, приведёнными на рисунке 4.

Рисунок 4 Временная диаграмма четырёхразрядного счётчика.

Пусть первоначальное состояние всех триггеров счётчика будет нулевым. Это состояние мы видим на временных диаграммах. Запишем его в таблицу 1. После поступления на вход счётчика тактового импульса (который воспринимается по заднему фронту) первый триггер изменяет своё состояние на противоположное, то есть единицу.

Запишем новое состояние выходов счётчика в ту же самую таблицу. Так как по приходу первого импульса изменилось состояние первого триггера, то этот триггер содержит младший разряд двоичного числа (единицы). В таблице поместим его значение на самом правом месте, как это принято при записи любых многоразрядных чисел. Здесь мы впервые сталкиваемся с противоречием правил записи чисел и правил распространения сигналов на принципиальных схемах.Подадим на вход счётчика ещё один тактовый импульс. Значение первого триггера снова изменится на прямо противоположное. На этот раз на выходе первого триггера, а значит и на входе второго триггера сформируется задний фронт. Это означает, что второй триггер тоже изменит своё состояние на противоположное. Это отчётливо видно на временных диаграммах, приведённых на рисунке 4. Запишем новое состояние выходов счётчика в таблицу 1. В этой строке таблицы образовалось двоичное число 2. Оно совпадает с номером входного импульса.

Продолжая анализировать временную диаграмму, можно определить, что на выходах приведённой схемы счётчика последовательно появляются цифры от 0 до 15. Эти цифры записаны в двоичном виде. При поступлении на счётный вход счётчика очередного импульса, содержимое его триггеров увеличивается на 1. Поэтому такие счётчики получили название суммирующих двоичных счётчиков.

Таблица 1. Изменение уровней на выходе суммирующего счётчика при поступлении на его вход импульсов.

| номер входного импульса | Q3 | Q2 | Q1 | Q0 |

Условно-графическое обозначение суммирующего двоичного счетчика на принципиальных схемах приведено на рисунке 5. В двоичных счётчиках обычно предусматривают вход обнуления микросхемы R, который позволяет записать во все триггеры счётчика нулевое значение. Это состояние иногда называют исходным состоянием счётчика.

Рисунок 5. Четырёхразрядный двоичный счётчик.

Существуют готовые микросхемы асинхронных двоичных счётчиков. Классическим примером такого счётчика является микросхема 555ИЕ5. Подобные схемы существуют и внутри САПР программируемых логических интегральных схем.

Дата добавления: 2015-04-10; просмотров: 1417;