Назначение и возможности процессора Nios II

Процессор Nios II, представленный компанией Altera в 2004 году, предназначен для замены оригинального процессора Nios, характеризующегося 16 битным набором инструкций и 16 битным регистровым окном. По мнению компании Gartner [12] в настоящее время процессор Nios II признан самым популярным конфигурируемым в кристалле FPGA процессором, лидером по гибкости использования.

Процессор Nios II может быть сконфигурирован под требуемую задачу. Существует 3 различные версии конфигурации процессора.

· Nios II/f (fast) – версия процессора, предназначенная для достижения максимальной производительности. Конфигурация имеет широкий набор опций для оптимизации процессора по производительности.

· Nios II/s (standart) – стандартная версия процессора, требующая меньше ресурсов для реализации, и характеризующаяся меньшей производительностью.

· Nios II/e (economy) – экономичная версия процессора, требующая наименьшее количество ресурсов кристалла для реализации, и обладающая ограниченным набором возможностей.

Процессор Nios II имеет RISC архитектуру, в которой арифметические и логические операции выполняются над операндами, находящимися в регистрах общего назначения. Обмен информацией между регистрами и памятью осуществляется путем выполнения команд “Load” и “Store”.

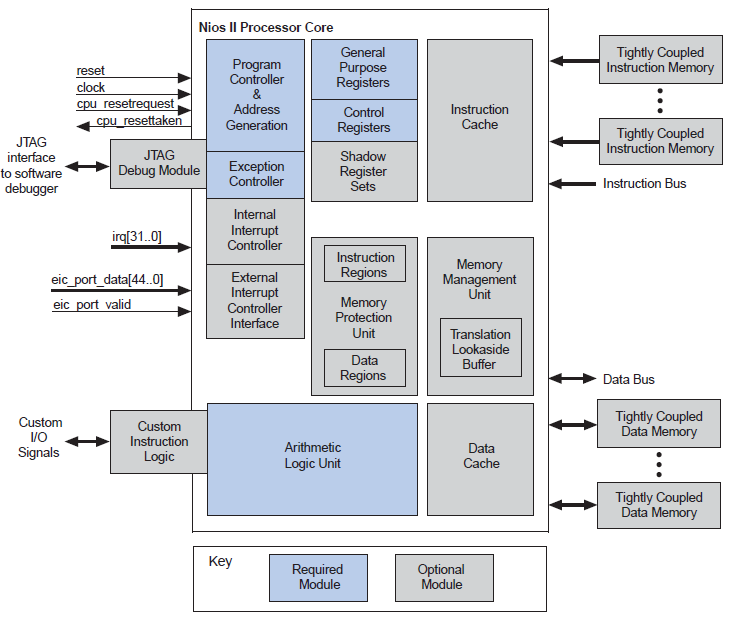

Машинное слово процессора Nios II имеет ширину 32 бита, такой же размер имеют его регистры. Для адресации байтов в слове используется little-endian стиль, при котором менее значимые байты расположены по меньшим адресам в ОП. Процессор имеет гарвардскую архитектуру, то есть использует раздельные шины для данных и команд. Структурная схема процессора Nios II, представленная в [13], воспроизведена на рис. 4.1.

Процессор Nios II может функционировать в следующих режимах.

· Режим супервизора. В этом режиме процессору разрешается выполнять все инструкции и осуществлять любые функции. Процессор переключается в этот режим после поступления сигнала сброса.

· Режим пользователя. Целью данного режима является предотвращение выполнения определенных инструкций системного назначения. Переключение в этот режим становится возможным лишь при наличии модуля управления памятью (MMU) или модуля защиты памяти (MPU).

Ниже приведены основные характеристики процессора Nios II/f:

- более 2-х гигабайт адресного пространства;

- отдельный кэш инструкций и кэш данных;

- аппаратное выполнение умножения и деления;

- 6-ти стадийный конвейер;

- поддержка исключений;

- система защиты памяти;

- система виртуальной памяти;

- выполнение операции умножения и сдвига за один такт;

- динамическое предсказание ветвлений;

- использование до 256 пользовательских инструкций;

- широкие возможности отладки через JTAG модуль;

- реализация требует 1400-1800 логических элементов FPGA;

- реализация включает 3 блока памяти M4K, плюс блоки для кэш памяти;

- производительность процессора 51 миллион операций в секунду (51 DMIPS) на частоте 50 МГц.

Процессор Nios IIи интерфейсы для сопряжения с оперативной памятью и другими периферийными компонентами системы реализуются в кристалле FPGA. Пример процессорной системы «DE2-70 Media Computer» приведен в предыдущем разделе учебного пособия. Для соединения компонентов процессорной системы используется синхронная шина Avalon. Как следует из [8], шина Avalonможет содержать следующие типы:

· Avalon Clock Interface , для передачи синхросигналов и управления ими;

· Avalon Reset Interface, для передачи сигналов сброса;

· Avalon Streaming Interface (Avalon-ST), для поддержки однонаправленных потоков данных, включая мультиплексированные, пакетные и данные цифровых сигнальных процессоров;

· Avalon Memory Mapped Interface (Avalon-MM), для чтения/записи с адресацией типа ведущий/ведомый;

· Avalon Tri-State Conduit Interface (Avalon TC), для сопряжения с модулями вне кристалла;

· Avalon Interrupt Interface, для реализации приоритетной системы прерываний;

· Avalon Conduit Interface, для объединения отдельных сигналов или групп сигналов, которые не подходят под любой другой тип шины Avalon.

Рис. 4.1 – Структурная схема процессора

Дата добавления: 2015-05-30; просмотров: 945;