Реализация алгоритмов управления последовательностных автоматов

5.6.1. Виды запоминающих устройств

Основной отличительной чертой последовательностных схем управления является наличие в их составе ЗУ. Поэтому последовательностные автоматы называются автоматами с памятью.Все реальные устройства автоматического управления содержат в своем составе элементы памяти, хотя бы в виде блок-контакта в схеме управления двигателем (см. рис. 5.9, а). Рассмотрим типовые ЗУ, применяемые в АСУТП.

По своему назначению ЗУ подразделяются на два класса: постоянные и оперативные.

ПЗУ предназначены для длительного хранения информации, потому их основным качеством является энергонезависимость, т.е. способность длительное время сохранять записанную информацию после отключения электропитания. По своей конструкции ПЗУ подразделяются на магнитомеханические и электронные.

Магнитомеханические ПЗУ — это жесткие магнитные и гибкие дискеты. Информация записывается на их дорожках в виде последовательности намагниченных и ненамагниченных участков в двоичном коде (намагниченный участок — это 1, а ненамагниченный — это 0). Магнитомеханические ПЗУ энергонезависимы и надежны, допускают перезапись информации, но их быстродействие ограничено скоростью вращения дисков. Они удобны для употребления в тех случаях, когда перезапись информации и обращение за информацией к ЗУ происходит относительно редко, как это бывает, например, при записи массива УП в памяти УЧПУ.

Электронные ПЗУ, в том числе перепрограммируемые (ППЗУ), выполняются на базе больших интегральных схем (БИС). Они обладают большей скоростью обмена информацией и используются для формирования в УВМ системного программного обеспечения (см. подразд. 6.1), а ППЗУ используются также для записи У П. Однако электронные ПЗУ имеют меньшую информационную емкость и низкую транспортабельность.

Оперативные ЗУ предназначены для скоростной обработки текущей (оперативной) информации. Эта информация не предназначена для длительного хранения, но должна быть обработана достаточно быстро, чтобы обеспечить управление быстродействующими исполнительными механизмами, электроприводами. Выполняются ОЗУ на энергозависимых БИС, но позволяют обрабатывать информацию с тактовой частотой в десятки и сотни мегагерц.

Основой БИС ОЗУ являются триггерные ячейки, выполненные на электронных элементах с двумя устойчивыми состояниями триггеров.

5.6.2. Триггеры

Триггер – логический элемент, обладающий двумя устойчивыми состояниями.

Простейшей триггерной ячейкой является асинхронный RS-триггер. Это ячейка с двумя входами (R и S) и двумя выходами: прямым выходом Q и инверсным выходом Q. По сигналу S = 1 (Set — установка) RS -триггер устанавливается в единичное состояние, которому соответствует Q = 1 и Q = 0. По сигналу R = 1 (Reset — сброс) RS -триггер сбрасывается в нулевое состояние, которому соответствует Q = 0 и Q = 1. Когда на одном из входов RS триггера имеется единичный сигнал, на другой вход должен быть подан нулевой сигнал.

Одновременная подача единичных сигналов на оба входа RS-триггера не допускается.

При наличии на обоих входах RS -триггера нулевых сигналов его состояние не изменяется. Таким образом, RS -триггер является последовательностной управляющей ячейкой, характеризующейся двумя различными внутренними состояниями, каждое из которых целесообразно обозначать сигналом на прямом выходе: Q = = 1 и Q = 0. В такую ячейку можно записать и в ней хранить информацию, объем которой не превышает 1 бит (см. подразд. 2.2).

Триггер — это стандартная ячейка ОЗУ для хранения информации емкостью 1 бит.

Функционирование RS -триггера может быть отображено таблицей выходов (табл. 5.9).

Из табл. 5.9 видно, что при R = 0 и S= 0 RS -триггер сохраняет свое состояние неизменным, т.е. хранит ранее записанную информацию: либо Q = 0, либо Q = 1. При подаче сигнала S' = 1 на выходе устанавливается Q' - 1 вместо = 0 или сохраняется Q = 1. Аналогично при подаче R' = 1 на выходе устанавливается Q'' = 0.

Запретность комбинации R= 1 и S= 1 (одновременно) означает, что клетки со звездочками можно заполнять произвольно, так как при нормальной эксплуатации . RS -триггера одновременное поступление R= 1 и S= 1 исключено. При реализации RS -тригтера на элементах ИЛИ —НЕ наиболее простая схема получается, если вместо звездочек поставить нули, а при реализации на элементах

Таблица 5.9

| R' | S' | G'-1 | Q' | Q' | Режим |

| Хранение информации Q'=Q'X | |||||

| Запись 1 Q'= 1 | |||||

| Запись 0 Q' = 0 | |||||

| *(1) | *(1) | Запретная комбинация | |||

| Q'=Q' |

И — НЕ из тех же соображений лучше поставить вместо всех звездочек единицы, что и сделано. Составляя по табл. 5.9 логические

формулы (см. подразд. 5.2) для функций Q1 и Q', получим следующие выражения:

Q' = S + RQ'] =SRQ'(5.9)

Q' = R + SQ'~l = RSQ'~l. (5.10)

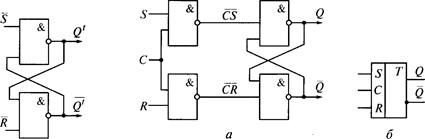

Вторые части формул (5.9) и (5.10) позволяют непосредственно по ним получить схему RS-триггера на элементах И — НЕ, приведенную на рис. 5.10.

Действительно, на выходе Q' имеем

Q' = RQ'-\ а на выходе Q' соответственно получим

Q> =SQ> =SRQ>-],

что соответствует выражению (5.9).

Аналогично проверяется правильность выражения (5.10) относительно выхода Q' схемы, показанной на рис. 5.10.

Если в формуле (5.9) принять Q = Н, S = dHdB, a R = dB, то она становится эквивалентной формуле (5.8). Таким образом, если на входе RS-триггера по схеме, представленной на рис. 5.10, поместить элемент И — НЕ, дающий S = dHdB, а на вход R подать сигнал dB, то функции схем, представленных на рис. 5.9, б и 5.10, совпадут.

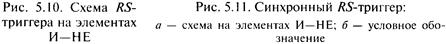

Чтобы получить синхронный RS -триггер, нужно на его входах предусмотреть две ячейки И —НЕ, на которые подается синхронизирующий импульс С (рис. 5.11).

Синхронный триггер переключается только при одновременной подаче единичных сигналов на один из информационных входов и на вход С (Clock). Так, при С = 1 и S = 1 имеем CS = 0 и триггер переключается в состояние Q - 1, Q = 0 или остается в этом состоянии (см. табл. 5.9). _

Путем подачи внутреннего сигнала CS на вход R Асинхронный RS -триггер превращается в триггер задержки — D -триггер (Delay — задержка).

У D -триггера вход R является внутренним, а информационный вход S переименован в D.

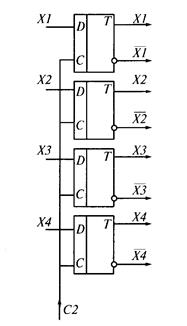

Рис. Синхронизация поступления входных сигналов X1….X4 .

Состояние D-триггера принимает то значение, которое имеется на входе D: при D = 1 получим Q= 1, а при D= 0 получим Q = 0, но только при условии, что С= 1. При С= 0 состояние выходов D -триггера не изменяется. Это свойство Д-триггера можно использовать для организации считывания информации со входов управляющего устройства.

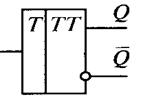

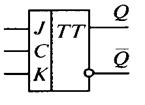

Из других типов триггеров для нас представляют интерес счетный триггер (Т- триггер) и J К- триггер (рис. 5.13). Т -триггеры лежат в основе схем различных счетчиков, а J К -триггеры являются универсальными в том смысле, что могут выполнять функции триггеров многих других типов. У Т -триггера имеется только один информационный (счетный) вход Т, который совпадает с тактовым входом С. После прохождения единичного импульса на счетном входе Т состояние триггера изменяется на противоположное.

Функционирование Т -триггера моделирует счет в двоичной системе счисления. Действительно, при подаче единичного импульса на его вход (Т = 1) при условии, что значение выхода в этот момент времени равно нулю (Q= 0), значение выхода становится равным единице (Q= 1). Это соответствует добавлению единицы в какой-либо разряд двоичного числа, значение которого до того было равно нулю. При подаче следующего единичного импульса {Т- 1) значение выхода триггера изменится от Q= 1 к Q = 0. То же самое происходит при прибавлении единицы в какой-либо разряд двоичного числа, если его значение до того было равно единице. Однако в двоичном числе при этом произойдет перенос единицы в следующий, старший, разряд. Такой же перенос единицы произойдет и на выходе счетного триггера, если к нему подключить вход следующего счетного триггера, как это делается в счетчиках (см. подразд. 5.6.3).

Универсальность J К -триггера заключается в том, что при подаче входных сигналов J = 1 или К= 1 раздельно он работает, как RS -триггер. Если же на вход К подавать инвертированный сигнал с входа J , то получится D -триггер. Апри подаче J = К= 1 одновременно он работает, как Т -триггер, т.е. изменяет свое состояние на противоположное после каждого прохождения единичного импульса на тактовом входе С. Следовательно, структура J К -триггера должна быть такой же, как Т -триггера, но должны быть предусмотрены отдельные информационные входы J и К.

Рис. 5.13. Условные обозначения Т -триггера (б) и J К -триггера (в)

5.6.3. Регистры

Триггеры, используемые в ОЗУ, применяются не по одному, а группами, называемыми регистрами.

Регистр — это электронное устройство, базирующееся на совокупности триггерных ячеек и предназначенное для хранения и преобразования помещенной в него информации, записанной в двоичном коде.

По характеру выполняемых операций регистры принято подразделять на регистры хранения, регистры сдвига и счетные регистры (счетчики).

Регистры хранения реализуют только одну, общую для регистров всех типов, функцию хранения информации в двоичном коде. Типичные регистры хранения строятся на D-триггерах. Примером простейшего регистра хранения является совокупность D-триггеров в схеме, приведенной на рис. 5.12.

Рис. 5.14. Регистр хранения RG, построенный на D-триггерах:

а — условное обозначение;

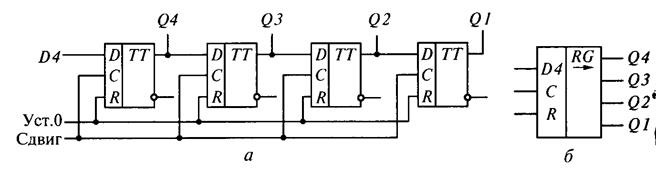

Регистры сдвига помимо приема, хранения и выдачи информации подобно регистрам хранения позволяют сдвигать записанную информацию, т.е. перемещать значения записанных битов информации от одной триггерной ячейки к другой, соседней, причем сдвиг информации производится одновременно во всех ячейках в одном направлении. На рис. 5.15 приведена упрощенная схема регистра сдвига, по которой можно судить о том, как организуется сдвиг информации в регистрах, построенных на D-триггерах.

Рис. 5.15. Схема регистра сдвига (а) и его условное обозначение (б)

Информация в такой регистр может поступать как в последовательном, так и в параллельном коде, а сдвиг информации производится подачей единичного импульса на вход сдвига. Вход сдвига организуется путем объединения всех тактовых входов регистра.

Поскольку все D -триггеры регистра соединены последовательно, а при подаче сигнала С = 1 информация со входа D-триггера передается на его выход, то при подаче единичного импульса сдвига вся информация, записанная в триггерах регистра, сдвигается слева направо на один разряд. При этом информация, хранившаяся до подачи импульса сдвига на выходе Q1, будет утрачена, если ее не переписать в какое-либо другое ЗУ, включенное на выходе Q1. Информация, передаваемая в последовательном коде, подается в регистр сдвига через информационный вход D4. Предварительно регистр может быть очищен единичным импульсом, подаваемым на входы R установки нуля. При поступлении на вход D4 информация подается поразрядно, начиная с младшего разряда. После подачи тактового импульса на вход сдвига информация переписывается из каждого разряда в соседний младший.

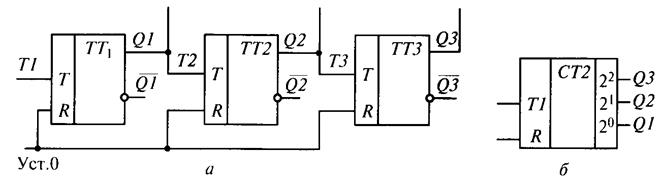

Счетные регистры, или счетчики, отличаются тем, что помимо функций записи, хранения и выдачи информации выполняют функцию счета поступающих на них импульсов с запоминанием результатов.

Рис. 5.16. Схема трехразрядного двоичного счетчика (а) и его условное обозначение (б)

Дата добавления: 2015-05-16; просмотров: 1019;