Напівпровідникові інтегральні схеми

Технологія

Напівпровідникова (монолітна, твердотіла) технологія більш придатна для масового виробництва ІС з високим ступенем інтеграції, характеристики яких не критичні щодо розкиду параметрів пасивних елементів, їх температурної нестабільності і впливу паразитних зв'язків. За напівпровідниковою технологією виготовляється більшість цифрових інтегральних схем і багатофункціональних аналогових ІС. Надійність напівпровідникових мікросхем значно вища, ніж у гібридних ІС, внаслідок невеликої кількості припаювань.

Усі елементи напівпровідникових ІС виконані всередині напівпровідникового кристала – чіпа. Товщина чіпа – 200-300 мкм, горизонтальні розміри – від 1,5 х 1,5 мм до 6,0 х 6,0 мм.

Планарно-дифузійна технологія виготовлення біполярних напівпровідникових інтегральних схем

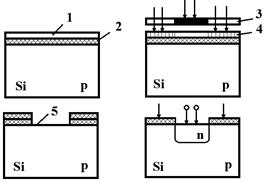

На кремнієвому кристалі (рис. 7.8) створюється тонкий шар двоокису SiO2. На нього наноситься шар 1 фоторезиста. Це речовина, яка під дією опромінення стає кислотостійкою. Фоторезист опромінюється ультрафіолетовими променями через фотошаблон 3 (фотопластинка з відповідним рисунком із прозорих і непрозорих ділянок). Опромінені ділянки 5 витравлюються кислотою. Цей процес називається фотолітографією. На ділянках 5 утворюються вікна, через які здійснюється процес дифузії донорних атомів із нагрітого газу 6.

Рисунок 7.8 – Технологія виготовлення біполярних структур ІС

Таким чином, у кремнієвому кристалі формуються n – області (так звані «кишені»), які відповідають емітерам усієї сукупності біполярних транзисторів цієї ІС. При повторенні операцій послідовно формуються області бази, потім - колектора. Паралельно формуються пасивні елементи, а на поверхні кристала – міжз'єднання і контактні площадки.

Ця планарно-дифузійна технологія має такі недоліки:

· нерівномірний розподіл домішок у областях;

· нерівномірний опір колектора і збільшення його значення;

· відсутні чіткі межі переходів, що призводить до зменшення напруги пробою між колектором і підкладкою;

· підкладка дуже впливає на електричні параметри транзистора ІС.

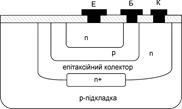

Натомість біполярні інтегральні транзистори, виготовлені за планарно-епітаксійною технологією, відзначаються рівномірним розподілом домішок (рис. 7.9).

Рисунок 7.9 – Планарно-епітаксійна біполярна структура

У них на p-підкладці вирощується колектор n - типу. Для зменшення опору колектора, а отже, зниження втрат потужності і ступеня впливу підкладки створюють прихований n+- шар, який має менший порівняно з епітаксійним n - шаром опір. Цей прихований шар створюється за допомогою додаткової дифузії донорних домішок у відповідні ділянки підкладки.

Дата добавления: 2015-04-25; просмотров: 1572;