Архитектура коммутаторов

В настоящее время используются коммутаторы следующих архитектур: матричные, шинные, с разделяемой памятью, комбинированные.

Матричные коммутаторы (cross bar) базируются на таком схемном решении, при котором практически для каждого соединения (подключения) имеется своя цепь. Входной пакет в матричном сетевом коммутаторе следует по матрице, пока не найдет пересечение с выходным портом, имеющим требуемый адрес. В таких коммутаторах число входных и выходных портов должно быть одинаковым. Матричные коммутаторы выполняют динамическую коммутацию, то есть условно в одно, и то же время поддерживает несколько соединений "порт-порт". Недостаток таких коммутаторов - сложность организации сетевого управления, так как в любой момент времени можно контролировать только одно соединение.

Недостатки матричных коммутаторов – квадратичная зависимость числа коммутирующих ключей от количества портов, поэтому такие коммутаторы строятся на небольшое количество входов.

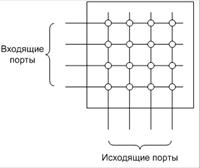

На рис. 4.4 представлена схема матричного коммутатора:

Рисунок 4.4

На рис. 4.5 показана структура шинного коммутатора:

Рисунок 4.5

В коммутаторах, имеющих шинную архитектуру, используется единая внутренняя шина, на которую путем мультиплексирования с временным разделением передаются пакеты из входных портов. В этих коммутаторах легко организовать передачу пакетов, которая называется "один ко многим" и "многие к одному". Благодаря наличию единой внутренней шины, упрощается организация сетевого управления путем наблюдения за информацией, которая присутствует на шине.

Производительность высокоскоростной шины должна быть выше в

2 n раза скорости поступления информации на порты коммутатора, где n – число портов.

Схема комбинированного коммутатора представлена на рис. 4.6.

Рисунок 4.6

В данном коммутаторе используется компромиссное решение: объединение принципов работы матричных и шинных коммутаторов. К высокоскоростной шине этого коммутатора подключается несколько модулей MK – матричных коммутаторов с небольшим числом портов. Эти коммутаторы представляют собой заказную микросхему ASIC (Application Specific Integral Circuit). Если порты, между которыми нужно передать информацию принадлежат одному модулю, информация на высокоскоростную шину не подается. Информация попадает на шину только в том случае, если порты принадлежат разным модулям. Естественно такое решение делает шину менее загруженной.

Дата добавления: 2015-02-16; просмотров: 2722;