Техническая документация МП.

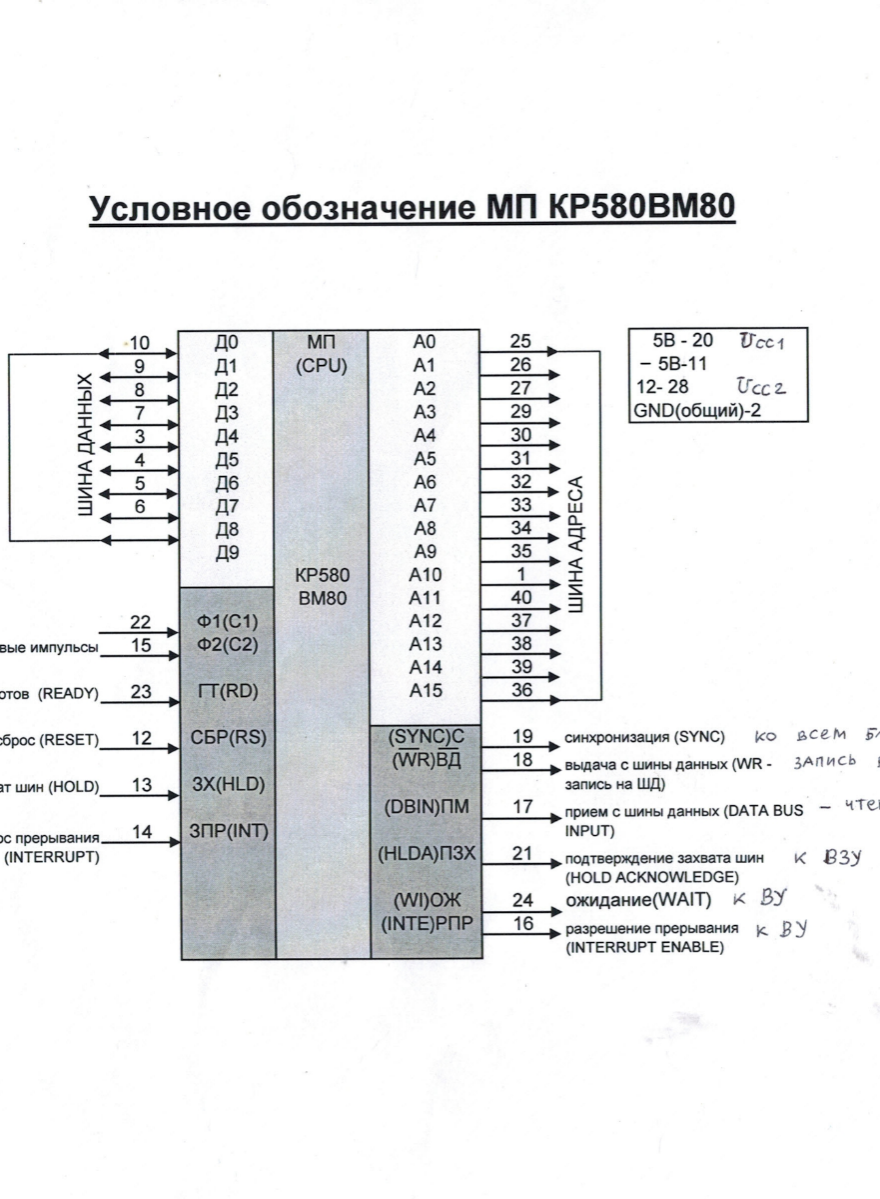

Схема выводов и их назначение.

Выводов от 32 до 64.

Схема БИС имеет следующие выводы:

1) 16 однонаправленных выводов адреса А0-А15

2) 8 двунаправленных адресов данных D0-D7

Имеются группа сигналов управления шинами INT

INTERRUPT – запрос на прерывание от внешних устройств.

INTA – от МП к устройству, которое запросило прерывание.

2 группы сигналов::

HOLD – запрос захвата внутренней шины МП

HLDA – разрешение на захват внутренней шины МП

Сигналы:

RESET – RS – сброс для возвращения внутренней схемы МП в исходное состояние.

2 сигнала тактовых импульсов:

F1 (начало такта) и F2 (сдвиг на некоторую величину) (С1 и С2).

4 сигнала управления:

MEMRD – чтение ЗУ

MEMWR – запись ЗУ

Для устройства ввода/вывода:

RDIO или IORD

WRIO или IOWR.

Главный параметр – мощность. Мощность – суммарный параметр, включающий в себя 3 параметра:

· Разрядность – количество бит информации, обрабатываемой МП за один такт. Наиболее распространенные 16,32,64 битные, 8-разрядные для учебных целей.

· Быстродействие – время выполнения операции сложения содержимого 2-х разрядов.(А)+(В)à(А).ADD B.

· Количество адресуемых слов памяти 216=65536=65к.(1 кб =210=1024 б=к)

Например,4 бита позволяют адресоваться к 16 различным словам(ячейкам памяти).т.е. диапазон адресации=16 слов.

Диапазон адресации 8-ми разрядной ША равен 256 слов памяти, а 16 битовой=65536:так как эти числа не круглые, их нелегко запомнить и произносить, то введено сокращенное обозначение этих чисел через к=1024 байт, тогда объем памяти 4096 байт составит 4 Кбайт. Кроме этих основных параметров МП характеризуется напряжением и количеством источников питания: мощностью рассеяния, температурным диапазоном, количеством воспринимаемых команд, помехоустойчивостью, нагрузочной способностью, наличием режимов прерывания, числом регистров, программным обеспечением, типом корпуса и др.

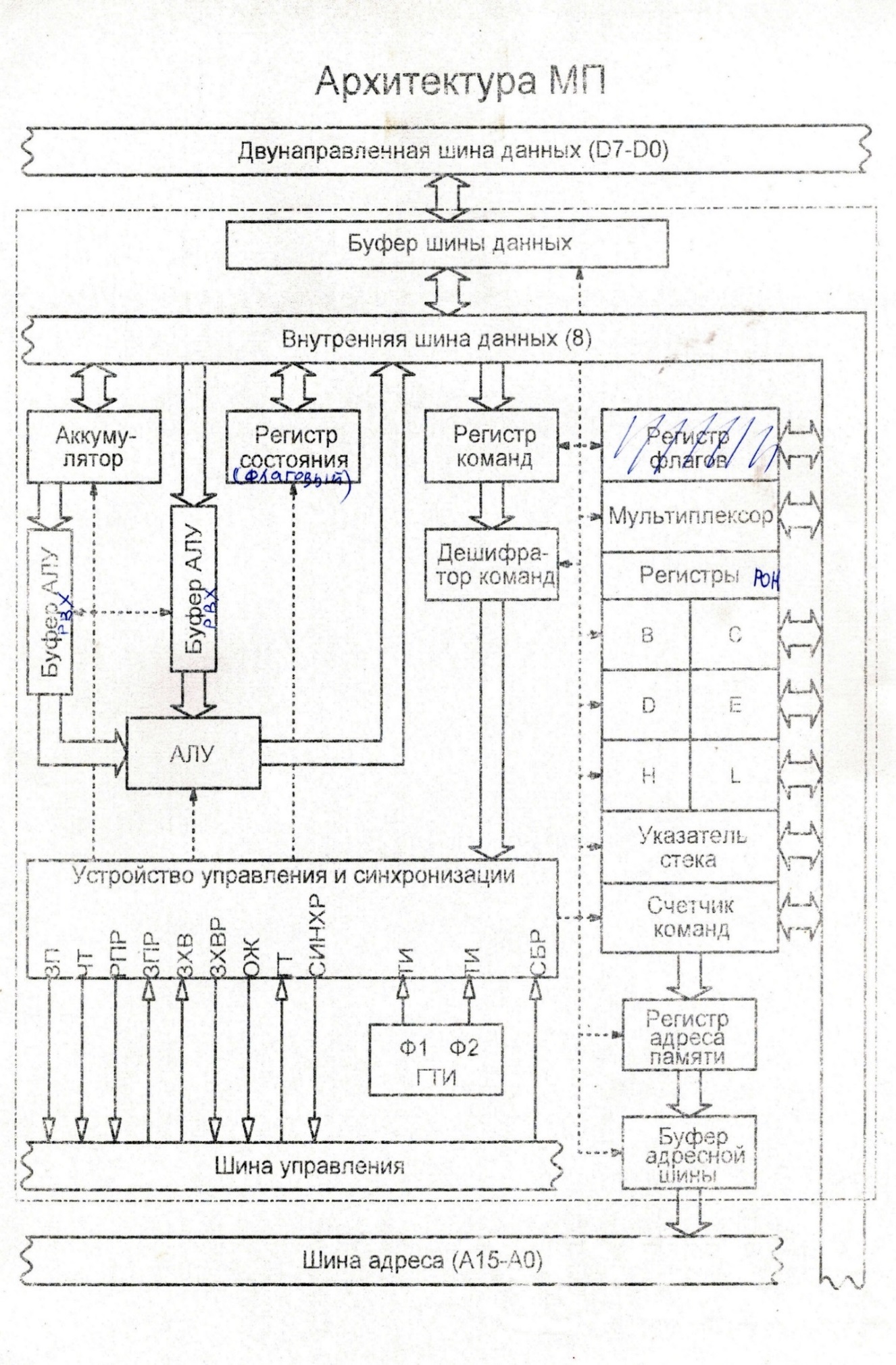

Архитектура МП

Основными двумя устройствами МП являются УУиС и АЛУ.

УУиС -ПЗУ внутри МП. МП внутри МП.

Основные функции:

· Включает секции – микропрограммы управляющих воздействий (микрокодов), необходимых

для выполнения каждой команды МП. Для КР580ВМ80-64 команды.

Управляет работой всех внутренних блоков МП и всех блоков МП системы.

· Включает питание для требуемых по программе внутренних схем МП.

· Выполняет синхронизацию работы всех устройств.

Архитектурная схема МП – система включает в себя 5 блоков.

Микропроцессор – программируемое цифровое устройство, предназначенное для автоматической обработки цифровых данных, в соответствии заложенной в систему программы.

ПЗУ(Постоянное запоминающее устройство ROM. Read Only Memory) - БИС, в которой заложены программы в процессе изготовления на заводе изготовителя, которые хранятся в этой памяти постоянно, даже при отключении питания.

ОЗУ(Оперативное запоминающее устройство.Read Acsess Memory) – память с произвольным доступом, предназначенная для хранения программ, разработанным пользователем (оператором). При отключении питания информация пропадает.

Устройство ввода – ИС называемая портом ввода цифровых данных с клавиатуры или датчиков в МП-систему.

Устройство вывода – порт вывода (регистр), предназначенный для вывода обработанных данных на монитор и к исполнительным органам всей системы.

Устройства управления и синхронизации предназначено:

1. Для выполнения всех микропрограмм для каждой команды, его ПЗУ содержит под определенными номерами все микропрограммы.

2. Подает управляющие сигналы по всем блокам МП-системы (запись, чтение, запрос прерывания, захват шин, разрешение захвата шин, ожидание WAIT, готов READY, сброс RES, синхронизация SYNC)

3. Разрешение работы всех внутренних блоков МП, путем подключения питания.

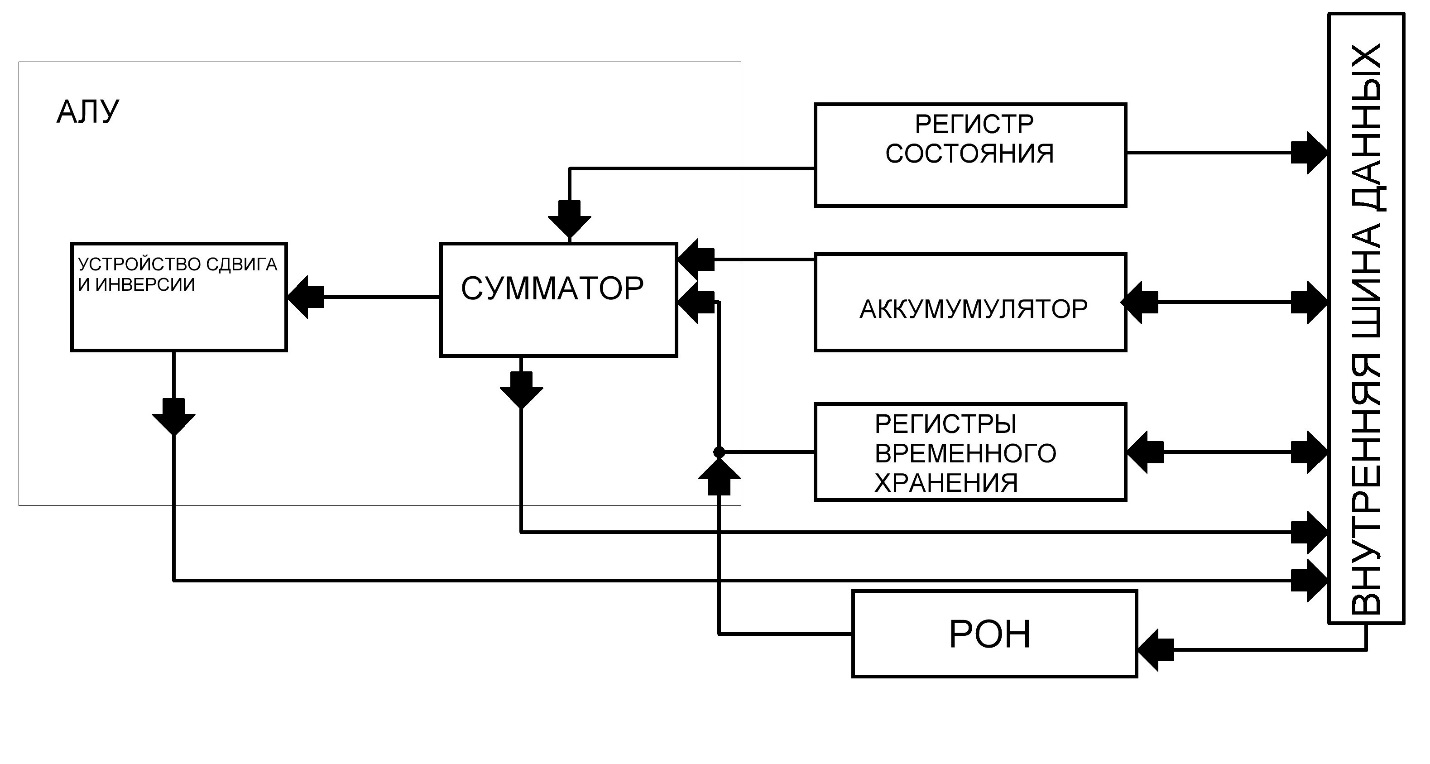

Следующий блок АЛУ предназначен для выполнения арифметических и логических операций над данными.

Представляет собой двухвходовое комбинационное устройство.

Кроме сумматора в АЛУ включен сдвиговый регистр, позволяющий выполнять программную операцию * или :.

АЛУ получает информацию:

1. Всегда от аккумулятора.

2. С внутренней шины данным МП, от регистра общего назначения B, C, D, Е, H, L или от ячейки памяти ОЗУ, в которую записаны данные.

Выдает информацию всегда в аккумулятор и на флаговый регистр, который устанавливает свои триггеры по результатам выполненной в АЛУ операции.

АЛУ не имеет внутренней памяти.2-х входовое комбинационное устройство, соединяющее логические элементы.

Схемы логических элементов подобраны для выполнения всех арифметических и логических команд.

Логические: AND, ANA, OR.

Арифметические: ADD(+), SUB(-), INR(+1), DCR(-1).

АЛУ –это двухвходовая логическая схема, на один вход которой сигнал поступает от аккумулятора .

Свое название схема получила потому, что в ней комбинации сигналов на входе однозначно определяет сигнал на выходе. Структурная схема АЛУ включает в себя двоичный сумматор, устройства сдвига и инверсии.

Результаты проведенной в сумматоре операции посредством внутренней шины помещаются в аккумулятор, и по результатам выполненной операции устанавливаются триггеры регистра состояния.

Одновременно АЛУ может совершать операции только над двумя операндами. В большинстве случаев один операнд находится в аккумуляторе, а второй извлекается командой из памяти или регистра временного хранения. Результат выполнения операции обычно остается в аккумуляторе. Основные операции, выполненные в АЛУ, это сложение и вычитание, логические операции, сдвиг вправо -влево, приращения положительные и отрицательные.

Буферные регистры АЛУ предназначены для временного хранения одного слова данных. В эти регистры на временное хранение поступают данные с внутренней шины МП, из А и регистров. Необходимость в таких регистрах вызывается отсутствием в АЛУ своего ЗУ. В состав АЛУ включены только комбинационные схемы, поэтому при поступлении исходных данных на вход АЛУ на выходе АЛУ немедленно появляются результирующие данные, как следствие выполненной операции. АЛУ должно при получении данных с внутренней шины МП, из А или регистров одновременно подать их на входы своих схем, модифицировать их, а затем уже результаты (обработанные данные) помещать в А.Все это неосуществимо без регистров временного хранения данных.Буферные регистры АЛУ недоступны (не могут быть использованы) программисту.

Буферные регистры предназначены для временного хранения обрабатываемых по программе цифровых слов. Буферы АЛУ загружаются автоматически, и они недоступны оператору.

Дата добавления: 2019-07-26; просмотров: 493;