Одноплатный микроконтроллер мМС1212

В условиях широкой компьютеризации особую роль приобретает создание развитых семейств программируемых МК. Семейства МК призваны обеспечить быструю компоновку и модификацию системы с теми или иными функциональными и скоростными свойствами с целью перекрытия ряда требований, которые предъявляет к ним конкретная задача применения. Пример проектирования базового модуля такого семейства был приведен в гл. 5, где представлен универсальный 8-разрядный одноплатный МК мМС1204, построенный на базе БИС серии КР580.

В ряде прикладных случаев быстродействие в 500 тыс. операций в секунду МК типа мМС1204 оказывается недостаточным. Поэтому предлагается использовать новый высокоэффективный одноплатный 16-разрядный МК мМС1212 с быстродействием до 2 млн. операций в секунду [51, 54]. В основу МК положен однокристальный МП К1810ВМ86 повышенного быстродействия.

Особенностью МК мМС1212, как и его 8-разрядного предшественника, является тщательно отобранный функционально полный набор аппаратных средств общесистемного профиля, организованных по открытому для расширения магистрально-модульному принципу с ориентацией на стандартную шину типа И41. Открытость архитектуры МК предопределяет возможность расширения его функций модулями системного расширения из состава семейства и специальными модулями, спроектированными исключительно для конкретного применения.

Архитектурная, функциональная, электрическая и конструктивная совместимость модулей мМС1212 и мМС1204 снизу вверх позволяет считать их элементами одного семейства. Вместе с этим получили развитие новые свойства, не характерные для систем на базе МП ВМ80, но важные для многих случаев применения МП ВМ86.

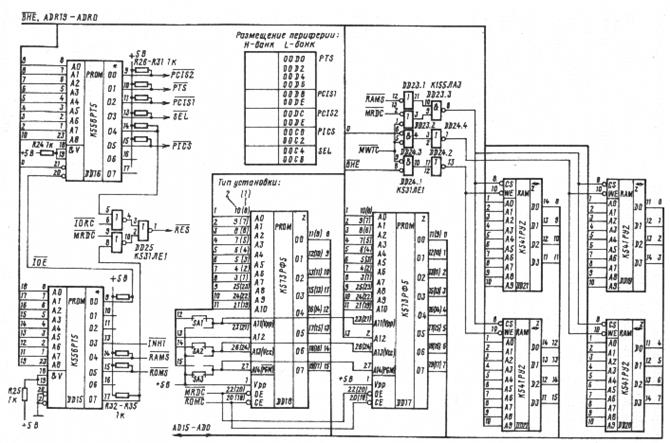

Микроконтроллер мМС1212 (рис. 7.15) собран на одной плате функционально законченной МС общего назначения. В состав МК входят 16-разрядный ЦП, ПЗУ, ОЗУ и два последовательных адаптера с интерфейсом типа ИРПС, представляющие собой резидентные средства ВВ. Для осуществления работы в режиме реального времени в состав микроконтроллера включены ядро расширяемой многоуровневой системы прерываний (СП) и таймер общесистемного времени (СТ). Все внутримодульные средства связаны между собой с помощью стандартной 16-разрядной шины типа И41, реализующей возможность многоплатного расширения функций МК в зависимости от конкретного применения. Состав системной магистрали мМС1212 и области размещения его внутримодульных ресурсов в пространствах памяти и портов ВВ МП ВМ86 также приведены на рис. 7.15.

Рис. 7.15. Схема одноплатного микроконтроллера мМС1212

Центральный процессор МК построен по схеме (см. рис. 7.8), которая подробно описана в § 7.4. Процессор формирует полный набор сигналов системной магистрали и служит для управления всеми остальными модулями МК.

В составе подсистемы памяти МК мМС1212 ОЗУ используется для хранения данных, ПЗУ—для хранения констант и программного кода. ОЗУ статического типа реализовано на четырех БИС К541РУ2 (1К´4 бит) [39] и размещено в области 00000Н—007FFH 1M-байтового адресного пространства памяти МК. Первая половина ОЗУ резервируется под организацию 256-элементной таблицы векторов прерываний, вторая предназначена для организации системного стека и хранения ряда переменных. Реальный раздел резидентного ОЗУ между таблицей прерываний и оставшейся областью пользователя зависит от конкретного приложения МК.

Оперативное запоминающее устройство организовано в виде двух 8-разрядных банков данных по 1 Мбайт каждый. Микроконтроллер осуществляет операции чтения и записи как слова, так и любого отдельного 6айта. Управление доступом производится сигналами  ,

,  ,

,  и

и  .

.

На плате МК имеются рассмотренные в § 5.1 и приведенные на рис. 5.3 универсальные панельки для установки двух 8-разрядных кристаллов УСППЗУ типа К573РФ2/РФ4/РФ5/РФ6, ЭСППЗУ К558РР3 или любых других со стандартной разводкой выводов, например 27256. Выбор типа кристаллов зависит от конкретного приложения МК. Правила установки кристаллов в МК указаны на рис. 7.16.

Рис. 7.16. Схема памяти

При включении питания или нажатии клавиши RESET управление в МП ВМ86 передается по логическому адресу 0FFFFH:0000Н, что соответствует физическому адресу 0FFFF0H. По этой причине последние 16 байт 1M-байтового адресного пространства памяти резервируется для инициализации МС. В первых пяти байтах этой области должна располагаться команда длинного перехода (FAR JMR) с 32-разрядным адресом sel:offset, загружаемым в пару CS:IP соответственно. Для организации этого перехода резидентную часть ПЗУ (2К—32К слов) лучше всего поместить в верхнюю область адресного пространства.

Постоянное запоминающее устройство организовано в виде единого 16-разрядного блока, считывание информации из которого всегда осуществляется словами без учета состояния линий  и ADR. Интерпретация данных возлагается на приемник информации—микропроцессор.

и ADR. Интерпретация данных возлагается на приемник информации—микропроцессор.

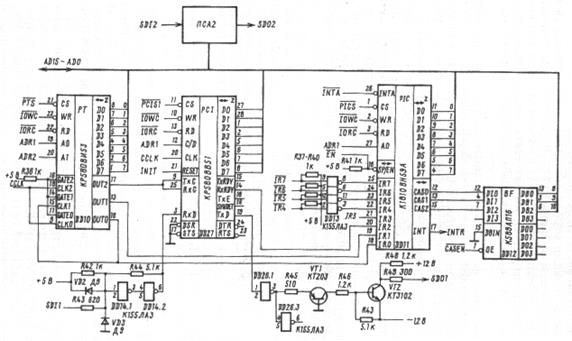

Система ВВ микроконтроллера содержит два последовательных канала связи типа ИРПС, реализованных на базе БИС программированного связного адаптера КР580ВВ51. Предполагается, что ПСА будут инициированы для работы в асинхронном старт-стоповом режиме. Один канал резервируется для подключения системной консоли, а второй может быть использован по усмотрению пользователя. Типичным вариантом его применения служит организация межмашинной связи.

Реализация средств ВВ включена в принципиальную схему рис. 7.17. Встроенные в последовательные каналы буферные схемы были обсуждены в § 3.4.

Рис. 7.17. Схема средств ВВ и поддержки реального времени

В качестве генератора скорости приема/передачи данных через ПСА используется один из трех счетчиков программируемого интервального таймера. Два других зарезервированы для общесистемных целей. Первый используется в качестве генератора меток системного времени, обычно следующих с частотой 20—100 Гц. Второй выполняет функцию счетчика пауз в единицах системного времени. Использование счетчиков ПИТ в других целях не предусмотрено.

В МК мМС1212 использована каскадно расширяемая система прерываний, резидентное ядро которой реализовано на трех микросхемах: К1810ВН59А, К589АП16 и К155ЛАЗ (DD13), см. рис. 7.17. Высокоуровневые входы ведущего программируемого контроллера прерываний IR3—IR0 связаны с запросами по готовности приемников ПСА2 и ПСА1, с сигналом окончания счета паузы и метками системного времени. Оставшиеся свободными для пользователя линии IR7—IR4 контроллера прерываний выведены на системную магистраль с низким уровнем активности. В разряд пользовательских входит также линия немаскируемого прерывания NMI с фиксированным вектором прерывания, равным 2.

В схеме на рис. 7.17 предусмотрены средства расширения системы прерываний по методу каскадирования. Для этого БИС ВН59А должна быть запрограммирована для работы в каскадном режиме в качестве ведущей. Ведомые контроллеры подключаются к пользовательским уровням запросов на прерывания  —

—  . Информация CAS2—CAS0 о выборе подчиненного контроллера передается через линии ADR10—ADR8 системной шины адреса.

. Информация CAS2—CAS0 о выборе подчиненного контроллера передается через линии ADR10—ADR8 системной шины адреса.

Генерируемый системным контроллером сигнал МСЕ активен в каждом из двух INTA-циклов, формируемых МП при приеме вектора прерывания. Этот перекрывающийся со стробом ALE сигнал позволяет пропустить адрес ведомого ВН59А CAS2—CAS0 на мультиплексную шину адреса/данных для запоминания в буферном адресном регистре. Однако выдача адреса линий CAS2—CAS0 на мультиплексную шину МП в первом цикле INTA не рекомендуется, так как гарантия о ее освобождении МП наступает лишь через 80 нс после начала цикла. Запрет сигнала МСЕ в первом цикле выполняет сигнал LOCK (см. рис. 7.8), который активизируется в такте Т2 первого цикла и снимается в такте Т2 второго цикла. Поскольку контроллер ВН59А выдает действительный адрес каскада только во втором цикле, то никакая информация не теряется.

При отсутствии БИС ВН59А последняя может быть заменена на ВН59 без изменения принципиальной и монтажной схем. В этом случае линия  не используется и должна быть отсоединена от ВН59. Ввод номера источника запросов выполняется по команде поллинга, а его декодирование—программными средствами, составляющими основу подпрограммы обслуживания прерывания с номером вектора прерывания 0FFH. Для этой и других целей мультиплексная шина адреса/данных должна быть подключена через дополнительные резисторы к источнику питания +5 В.

не используется и должна быть отсоединена от ВН59. Ввод номера источника запросов выполняется по команде поллинга, а его декодирование—программными средствами, составляющими основу подпрограммы обслуживания прерывания с номером вектора прерывания 0FFH. Для этой и других целей мультиплексная шина адреса/данных должна быть подключена через дополнительные резисторы к источнику питания +5 В.

Методика подключения БИС памяти к 16-разрядной шине И41 и других ПУ была изложена в § 7.1. Для организации логики выборки БИС в МК мМС1212 использованы две микросхемы ППЗУ К556РТ5 (512´8 бит) DD15 и DD16 (рис. 7.16). При размещении в адресном пространстве блоков резидентного ОЗУ и ПЗУ реализуется БИС DD15. Эта же микросхема с помощью сигнала  выделяет область ВВ (0000Н—07FFH) в 1 К слов для последующего размещения в ней портов всех резидентных ПУ МК. Содержимое ППЗУ DD15 для случая, когда емкость ПУ МК равна 16К словам (21728´2) приведено в табл. 7.1. Генерируемый логикой выборки кристаллов сигнал

выделяет область ВВ (0000Н—07FFH) в 1 К слов для последующего размещения в ней портов всех резидентных ПУ МК. Содержимое ППЗУ DD15 для случая, когда емкость ПУ МК равна 16К словам (21728´2) приведено в табл. 7.1. Генерируемый логикой выборки кристаллов сигнал  :

:

INH1 = ROMS + RAMS

служит сигналом запрета работы основной памяти [14], которая может иметь физические ячейки в области адресов резидентного ОЗУ/ПЗУ. Линия  выполнена по схеме с открытым коллектором. Вторая ступень логики выборки кристаллов ПУ реализована на DD16, содержимое ППЗУ которой приведено в табл. 7.2. Все 8-разрядные массивы портов программируемых периферийных БИС размещены в L-банке пространства ВВ. По этой причине БИС DD16 открывается лишь при условии доступа к L-банку (ADR0 = 0) без учета состояния

выполнена по схеме с открытым коллектором. Вторая ступень логики выборки кристаллов ПУ реализована на DD16, содержимое ППЗУ которой приведено в табл. 7.2. Все 8-разрядные массивы портов программируемых периферийных БИС размещены в L-банке пространства ВВ. По этой причине БИС DD16 открывается лишь при условии доступа к L-банку (ADR0 = 0) без учета состояния  . Вспомогательный сигнал

. Вспомогательный сигнал  используется в отладочных целях для синхронизации осциллографа.

используется в отладочных целях для синхронизации осциллографа.

Таблица 7.1 Таблица 7.2

| Адрес ПЗУ | Сос-тояние | Адрес ПЗУ | Cос-тояние | Адрес ПЗУ | Сос-тояние | Адрес ПЗУ | Состояние | |

| 15F | 1BF | 00C | CF | |||||

| 10Е | 16F | 1CF | 02C | ED | ||||

| 11F | 17F | 1DF | 06C | ЕВ | ||||

| 12F | 18F | 1EF | 08C | E7 | ||||

| 13F | 19F | 1FF | 0AC | ED | ||||

| 14F | 1AF | Осталь- ные | FF | 0EC Остальные | ЕЕ FF |

Дополнительная внешняя логика формирует сигнал  , корректирующий направление передачи драйвера шины данных. При чтении данных с устройств, расположенных непосредственно на плате, шинный драйвер автоматически включается на передачу. При вводе вектора прерывания возникают особые сложности, которые связаны с тем, что ведущий контроллер находится на мультиплексной шине, а дополнительные ведомые (возможно, отсутствующие)—на системной шине данных. Правильное решение дает схема на рис. 7.17, в которой генерируемый главным контроллером ВН59А по двунаправленной линии

, корректирующий направление передачи драйвера шины данных. При чтении данных с устройств, расположенных непосредственно на плате, шинный драйвер автоматически включается на передачу. При вводе вектора прерывания возникают особые сложности, которые связаны с тем, что ведущий контроллер находится на мультиплексной шине, а дополнительные ведомые (возможно, отсутствующие)—на системной шине данных. Правильное решение дает схема на рис. 7.17, в которой генерируемый главным контроллером ВН59А по двунаправленной линии  /

/  сигнал

сигнал  (выдача данных) используется для коррекции направления передачи через шинный драйвер. При этом вопрос о правильном вводе вектора прерывания как в каскадном, так и в одиночном режиме работы контроллера прерываний решается автоматически.

(выдача данных) используется для коррекции направления передачи через шинный драйвер. При этом вопрос о правильном вводе вектора прерывания как в каскадном, так и в одиночном режиме работы контроллера прерываний решается автоматически.

СПИСОК ЛИТЕРАТУРЫ

1.  Алексенко А. Г., Галиции А. А., Иванников А. Д. Проектирование радиоэлектронной аппаратуры на микропроцессорах.—М.: Радио и связь, 1984.—272 с.

Алексенко А. Г., Галиции А. А., Иванников А. Д. Проектирование радиоэлектронной аппаратуры на микропроцессорах.—М.: Радио и связь, 1984.—272 с.

- Алексенко А. Г., Шагурин В. И. Микросхемотехника.—М.: Радио и связь, 1982.—416 с.

- Балашов Е. П., Григорьев В. Л., Петров Г. А. Микро- и мини-ЭВМ: Учеб. пособие для вузов.—Л.: Энергоатомиздат. 1984.—376 с.

- Балашов Е. П., Пузанков Д. В. Микропроцессоры и микропроцессорные системы: Учеб. пособие для вузов/Под ред. В. Б. Смолова.—М.: Радио и связь, 1981.—328 с.

- Баррон И., Кэвил П., Мэй Д. Транспьютер с быстродействием 5 млн. операций/с и более//Электроника.—1982.—№ 24.—С. 26—35.

- Березенко А. И. Микропроцессорные комплекты общего применения.—М.: Машиностроение, 1982.—120 с.

- Бистон Дж. Микроконтроллеры второго поколения, реализующие специализированные функции//Электроника.—1978.—№ 24.—С. 52—60.

- Брусеицов Н. П. Микрокомпьютеры.—М.: Наука, 1985.—208 с.

- Вайда Ф., Чакань А. МикроЭВМ: Пер. с венг.—М.: Энергия, 1980.—360 с.

- Григорьев В. Л. Программирование однокристальных микропроцессоров.—М.: Энергоатомиздат, 1987.—288 с.

- Григорьев В. Л. Программное обеспечение микропроцессорных систем.—М.: Энергоатомиздат, 1983.—208 с.

- Гилмор Ч. Введение в микропроцессорную технику: Пер. с англ.—М.: Мир, 1984.—334 с.

- Дианов А. П., Щелкунов Н. Н. Методика программирования микросхем ПЗУ//Микропроцессорные средства и системы.—1985.—№ 3.—С. 75—79.

- Дианов А. П., Щелкунов Н. Н. Организация динамической памяти микросистем//Микропроцессорные средства и системы.—1987.—№ 4.—С. 75—80.

- Дианов А. П., Щелкунов Н. Н. Система проектирования микропроцессорных устройств//Микропроцессорные средства и системы.—1987.—№ 5.—С. 83—86.

- Каган Б. М., Сташин В. В. Микропроцессоры в цифровых системах.—М.: Энергия, 1979.—192 с.

- Каган Б. М., Сташин В. В. Основы проектирования микропроцессорных устройств автоматики.—М.: Энергоатомиздат, 1987.—304 с.

- Каган Б. М. Электронные вычислительные машины и системы: Учеб. пособие для вузов.—2-е изд.—М.: Энергия, 1985.—542 с.

- Клингман Э. Проектирование микропроцессорных систем: Пер. с англ.—М.: Мир, 1980.—576 с.

- Клингман Э. Проектирование специализированных микропроцессорных систем: Пер. с англ.—М.: Мир, 1985.—363 с.

- Кобылинский А. В., Липоветский Г. П. Однокристальные микроЭВМ серии К1816//Микропроцессорные средства и системы.—1986.—№ 1.—С. 10—19.

- Кобылинский А. В., Москалевский А. Н., Темченко В. А. Однокристальный высокопроизводительный 16-разрядный микропроцессор KM1810BM86//Микропроцессорные средства и системы.—1986.—№ 1.—С. 28—33.

- Коффрон Дж. Технические средства микропроцессорных систем. Практический курс: Пер. с англ.—М.: Мир, 1983.—344 с.

- Левенталь Л. Введение в микропроцессоры.—М.: Энергоатомиздат, 1983.—463 с.

- Линьят А. Архитектура малых вычислительных систем: Пер. с англ./Под ред. К. В. Поселена.—М.: Мир, 1981.—187 с.

- Мик Дж., Брик Дж. Проектирование микропроцессорных устройств с разрядно-модульной организацией. В 2-х кн.: Пер. с англ.—М.: Мир, 1984.—Кн. 1.—253 с.—Кн. 2.—223 с.

- Микрокомпьютер 8086, обладающий возможностями 8- и 16-разрядных процессоров/Кац, Морс, Полман, Ривенел // Электроника.—1978.—№ 4—С. 23—31.

- Микропроцессорные БИС и микро-ЭВМ: Построение и применение/А. А. Васенков, Н. М. Воробьев, В. Л. Дшхунян и др.; Под ред. А. А. Васенкова.—М.: Сов. радио, 1980.—280 с.

- Микропроцессоры. В 3-х кн.: Учеб. пособие для вузов/Под ред. Л. Н. Преснухина. М.: Высшая школа, 1986.—Кн. 1.—495 с.; Кн. 2.—383 с.; Кн. 3—351 с.

- Микропроцессоры: Системы программирования и отладки/В. А. Мясников, М. Б. Игнатьев, А. А. Кочкин, Ю. Е. Шейнин; Под ред. В. А. Мясникова, М. Б. Игнатьева.—М.: Энергоатомиздат, 1985.—272 с.

- Монолитный микрокомпьютер с аналого-цифровым преобразователем/В. Чек, Е. Чжен, Г. Хилл и др.//Электроника.—1978.—№ 11.—С. 36—44.

- Мун Дж. Микрокомпьютер для эмуляции//Электроника.—1980.—№ 16.—С. 48—53.

- Мячев А. А., Иванов В. В. Интерфейсы вычислительных систем на базе мини-и микро-ЭВМ/Под ред. Б. Н. Наумова.—М.: Радио и связь, 1986.—248 с.

- Неверески У. Дж. 8- и 16-разрядные процессоры—наиболее сложные КМОП-схемы с высокоуровневой архитектурой//Электроника.—1984.—№ 7.—С. 27—35.

- Погорелый С. Д., Слободянюк Т. Ф. Программное обеспечение микропроцессорных систем.—Киев: Техника, 1985.—240 с.

- Полупроводниковые БИС запоминающих устройств: Справочник/В. В. Баранов, Н. В. Бекин, А. Ю. Гордонов и др.; Под ред. А. Ю. Гордонова и Ю. Н. Дьякова.—М.: Радио и связь, 1987.—360 с.

- Проектирование цифровых систем на комплектах микропрограммируемых БИС/С. С. Булгаков, В. М. Мещеряков, В. В. Новоселов, Л. А. Шумилов; Под ред. В. Г. Колесникова.—М.: Радио и связь, 1984.—240 с.

- Система команд микропроцессора КМ1810ВМ86/А. В. Кобылинский, А. В. Береза, Н. Г. Сабадаш и др.//Микропроцессорные средства и системы.—1986.—№ 2.—С. 3—9.

- Соботка З., Стары Я. Микропроцессорные системы: Пер. с чеш.—М.: Энергоатомиздат, 1981.—496 с.

- Соучек Б. Микропроцессоры и микроЭВМ: Пер. с англ.—М.: Сов. радио, 1979.—520 с.

- Уокерли Дж. Архитектура и программирование микроЭВМ. В 2-х кн.: Пер. с англ.—М.: Мир, 1984.—Кн. 1.—496 с.; Кн. 2.—341 с.

- Форс. Стандартная микропроцессорная шина, упрощающая задачи разработчиков микрокомпьютеров//Электроника.—1978.—№ 15.—С. 33—41.

- Хоуп Г. Проектирование цифровых вычислительных устройств на интегральных схемах: Пер. с англ.—М.: Мир, 1984.—400 с.

- Хилбурн Дж., Джулич П. МикроЭВМ и микропроцессоры: Пер. с англ./Под ред. С. Д. Пашкеева.—М.: Мир, 1979.—463 с.

- Шевкопляс Б. М. Микропроцессорные структуры. Инженерные решения.—М.: Радио и связь, 1986.—264 с.

- Шумейкер К. Микропроцессор, содержащий ряд периферийных функциональных блоков и упрощающий построение микросистем//Электроника.—1983.—№ 9.—С. 51—59.

- Шумейкер К. 16-разрядный СБИС-микропроцессор с высокими техническими характеристиками//Электроника.—1983.—№ 10.—С. 45—51.

- Щелкунов Н. Н., Дианов А. П. Одноплатный 16-разрядный микроконтроллер общего назначения//Микропроцессорные средства и системы.—1987.—№ 1.—С. 77—83.

- Щелкунов Н. Н., Дианов А. П. Программирование микросистем реального времени//Микропроцессорные средства и системы.—1985.—№ 4.—С. 31—35.

- Щелкунов Н. Н., Дианов А. П. Процедуры программирования логических матриц//Микропроцессорные средства и системы.—1986.—№ 2.—С. 71—76.

- Щелкунов Н. Н., Дианов А. П. Техника программирования 16-разрядных микроконтроллеров//Микропроцессорные средства и системы.—1987.—№ 2.—С. 11—14.

- Щелкунов Н. Н., Дианов А. П. Техника программирования 8-разрядных микроконтроллеров//Микропроцессорные средства и системы.—1986.—№ 6.—С. 23—28.

- Щелкунов Н. Н., Дианов А. П. Универсальный одноплатный микроконтроллер//Микропроцессорные средства и системы.—1986.—№ 5.—С. 65—69.

- АРХ-186 High Integration 16-bit Microprocessor.—Intel, 1982.

- APX-286/10 High Performance Microprocessor with Memory Management and Protection.—Intel, 1983.

- MCS-80/85 Microprocessors.—Intel, 1977.

- Microcontroller Handbook.—Intel, 1985.

- The 8086 Family Users Manual.—Intel, 1979.

- UPI-41 Users Manual.—Intel, 1977.

- 80386 High Performance Microprocessor with Integrated Memory Management.—Intel, 1985.

- Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник. В 2-х т./Н. Н. Аверьянов, А. И. Березенко, Ю. И. Борщенко и др.; Под ред. В. А. Шахнова.—М.: Радио и связь, 1988.—Т. 1.—368 с.—Т. 2.—368 с.

- Лю Ю-Чжен, Гибсон Г. Микропроцессоры семейства 8086/8088. Архитектура, программирование и проектирование микрокомпьютерных систем: Пер. с англ.—М.: Радио и связь, 1987.—512 с.

- Ушкар М. Н. Микропроцессорные устройства в радиоэлектронной аппаратуре.—М.: Радио и связь, 1988.—128 с.

- Перспективные однокристальные ЭВМ/M. Г. Весноватов, Г. В. Карацюба, В В Павлов, В. А. Старшова//Микропроцессорные средства и системы.—1987.—№ 2.—С. 7, 8.

- Басманов А. С., Широков Ю. Ф. Микропроцессоры и однокристальные микро-ЭВМ: Номенклатура и функциональные возможности/Под ред. В. Г. Дорачева—М.: Энергоатомиздат, 1988.—128 с.

Дата добавления: 2019-02-07; просмотров: 772;