Правила минимизации с использованием карт Карно

1. В карте Карно группы единиц (для получения ДНФ) и группы нулей (для получения КНФ) необходимо обвести четырехугольными контурами. Внутри контура должны находиться только одноименные значения функции. Этот процесс соответствует операции склеивания или нахождения импликант данной функции.

2. Количество клеток внутри контура должно быть кратно степени двойки (1, 2, 4, 8, 16...).

3. При проведении контуров крайние строки карты (верхние и нижние, левые и правые), а также угловые клетки, считаются соседними (для карт до 4-х переменных).

4. Каждый контур должен включать максимально возможное количество клеток. В этом случае он будет соответствовать простой импликанте (имплиценте). Число контуров должно быть минимальным.

5. Все единицы (нули) в карте (даже одиночные) должны быть охвачены контурами. Любая единица (нуль) может входить в контуры произвольное количество раз.

6. Число контуров должно быть минимальным. Множество контуров, покрывающих все 1 (0) функции образуют тупиковую ДНФ (КНФ). Целью минимизации является нахождение минимальной из множества тупиковых форм.

7. В элементарной конъюнкции (дизъюнкции), которая соответствует одному контуру, остаются только те переменные, значение которых не изменяется внутри обведенного контура. Переменные булевой функции входят в элементарную коньюнкцию (для значений функции 1) без инверсии, если их значение на соответствующих координатах равно 1 и с инверсией - если 0. Для значений булевой функции, равных 0, записываются элементарные дизьюнкции, куда переменные входят без инверсии, если их значение на соответствующих координатах равно 0 и с инверсией - если 1.

Рассмотрим пример на рис. 2.52.

Рисунок 2.52 – Карта Карно двух переменных

СДНФ:  . Применяя для минимизации метод аналитических преобразований (закон склеивания и Блейка-Порецкого), получаем:

. Применяя для минимизации метод аналитических преобразований (закон склеивания и Блейка-Порецкого), получаем:

.

.

Можно пойти другим путем, применяя операцию неполного склеивания, получим дизъюнкцию импликант:

,

,

и

и  - простые импликанты, поскольку к ним невозможно применить операцию склеивания, они образуют сокращенную ДНФ. Других вариантов нет, поэтому данная ДНФ является тупиковой, кратчайшей и минимальной.

- простые импликанты, поскольку к ним невозможно применить операцию склеивания, они образуют сокращенную ДНФ. Других вариантов нет, поэтому данная ДНФ является тупиковой, кратчайшей и минимальной.

По карте Карно получаем:

МДНФ:  .

.

МКНФ:  .

.

В кубической форме процесс минимизации будет выглядеть следующим образом:

01È11=Х1,

10È11=1Х,

где 01, 10, 11 – минтермы, Х1 и 1Х – импликанты, они же простые импликанты. Остается одна простая иплицента (она же макстерм) 00. С1= {1Х, Х1}, С0= {00}.

Рассмотрим пример на рис. 2.53.

Рисунок 2.53 – Карта Карно трех переменных

СДНФ:  ,

,

МДНФ:  .

.

Рассмотрим пример на рис. 2.54.

Рисунок 2.54 – Карта Карно четырех переменных

МДНФ:  .

.

МКНФ:  .

.

Для частично (не полностью) определенных функций рассмотрим пример на рис. 2.55. Неизвестные значения, обозначаемые Х участвуют в склеивании

Рисунок 2.55 – Карта Карно четырех переменных частично определенной функции

МДНФ:  .

.

МКНФ:  .

.

КП={C0, C1},

.

.

Если рассматривать запись результатов минимизации в кубическом виде, то при минимизации булевой функции по единичным значениям каждой конъюнкции ранга R соответствует куб ранга R, где каждой переменной без инверсии соответствует 1 в кубе, переменной с инверсией - 0, а на месте отсутствующей переменной ставиться X. Полученное множество кубов образует единичное покрытие C1 (соответствующее ДНФ).

При минимизации булевой функции по нулевым значениям и представлении результатов минимизации в кубическом виде, нулевое покрытие C0 формируется на основе КНФ. Таким образом, каждой дизъюнкции ранга R (из КНФ) соответствует куб ранга R, где каждой переменной без инверсии соответствует 0 в кубе, переменной с инверсией - 1, а на месте отсутствующей переменной ставиться X. Полученное множество кубов образует нулевое покрытие C0 (соответствующее КНФ).

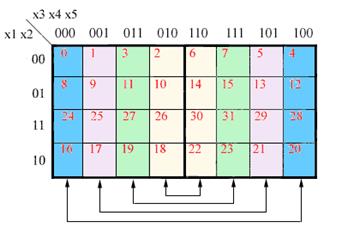

Особенностью изображения карт Карно для числа переменных более 4-х является то, что «математически» соседние столбцы карты Карно пространственно оказываются разнесенными. Таким образом, карта Карно для 5 переменных представляет собой две карты 4-х переменных, зеркально отображенные относительно центральной вертикальной линии (выделенной жирным тоном на рис. 2.56).

Рисунок 2.56 – Карта Карно пяти переменных

При этом столбцы одного цвета в правой и левой частях карты фактически оказываются соседними по переменной x3 (соседние столбцы также указываются стрелками в нижней части карты). При выполнении склеиваний следует учитывать «соседство» указанных столбцов, особенно розовых и зеленых, которые пространственно разделены.

2.2.3 Минимизация систем булевых функций

Существует два подхода в минимизации систем булевых функций:

- минимизация каждой функции в отдельности;

- совместная минимизация функций системы.

Рассмотрим первое направление. Если произвести минимизацию булевых функций, входящих в систему, независимо друг от друга, то общая схема будет состоять из изолированных подсхем. Ее можно иногда упростить за счет объединения участков подсхем, реализующих одинаковые члены, входящие в несколько булевых функций системы.

Пусть в результате минимизации функций получены следующие МДНФ:

На рис. 2.57 показана реализация системы функций без учета общих частей (термов). Аппаратурные затраты по критерию Квайна без учета инверсий для данной реализации составляют Cb = 18.

На рис. 2.58 показана реализация системы функций с объединением общих частей  . Аппаратурные затраты по критерию Квайна без учета инверсий для данной реализации составляют Cb = 14.Очевидно, что данная реализация является более простой (экономичной).

. Аппаратурные затраты по критерию Квайна без учета инверсий для данной реализации составляют Cb = 14.Очевидно, что данная реализация является более простой (экономичной).

Рисунок 2.57 – Реализация системы функций без учета общих частей

Рисунок 2.58 – Реализация система функций с объединением общих частей

Данный метод не всегда эффективен. Ниже это будет проиллюстрировано примером.

Рассмотрим второе направление. Существуют различные методы, в данном случае предлагается метод минимизации системы булевых функций. Алгоритм минимизации следующий. (Для КНФ алгоритм аналогичен).

1. Выписать все минтермы функций (можно в кубической форме), входящие в систему. Каждому минтерму присвоить признак, содержащий номера функций системы, в которые входит рассматриваемый минтерм, например, минтерм 0 (f1, f3) 0000, минтерм 15 (f1) 1111.

2. Выполнить склеивание. Если признаки склеиваемых элементарных произведений (минтермов и далее импликант) не содержат общих номеров, склеивание не выполняется, поскольку эти элементарные произведения не относятся к одной функции. Результату склеивания (импликантам) присваивать признак, состоящий из номеров функций, общих для двух склеиваемых минтермов или импликант. Не участвовавшие в склеивании импликанты и минтермы являются простыми импликантами и все они составляют сокращенную ДНФ системы, записываемой в виде функции  .

.

3. Построить таблицу покрытий функции  - для каждого минтерма выделяется столько столбцов, сколько различных номеров функций содержит его признак. Далее все аналогично, строится минимальная форма функции

- для каждого минтерма выделяется столько столбцов, сколько различных номеров функций содержит его признак. Далее все аналогично, строится минимальная форма функции  .

.

4. Произвести получение выражений МДНФ для каждой функции системы по функции  .

.

Замечание. Если функция не полностью определена, наборы, на которых она не определена, должны участвовать в склеивании, но в таблицу покрытий не вносятся.

Рассмотрим пример. Пусть дана система булевых функций (табл. 2.8). Найдем МДНФ системы булевых функций.

Таблица 2.8 – Таблица истинности системы булевых функций

|

|

| 0 0 0 | 1 1 |

| 0 0 1 | 0 0 |

| 0 1 0 | 0 1 |

| 0 1 1 | 0 1 |

| 1 0 0 | 0 0 |

| 1 0 1 | 1 1 |

| 1 1 0 | 1 0 |

| 1 1 1 | 1 0 |

Выполняем склеивания.

| 0-кубы | 1-кубы | ||

| 0 – 000 (f1, f2) | v | 0 (f1, f2) È 2 (f2) = 0х0 (f2) | |

| 2 – 010 (f2) | v | 2 (f2) È 3 (f2) = 01х (f2) | |

| 3 – 011 (f2) | v | 2 (f2) È6 (f1) нельзя | |

| 5 – 101 (f1, f2) | v | 3 (f2) È 7 (f1) нельзя | |

| 6 – 110 (f1) | v | 5 (f1, f2) È 7 (f1) = 1х1 (f1) | |

| 7 – 111 (f1) | v | 6 (f1) È 7 (f1) = 11х (f1) |

В склеивании не участвовали все 1-кубы и два 0-куба 000 (f1) и 101 (f2). Это простые импликанты. Они составляют сокращенную ДНФ функции  . Все они войдут в таблицу покрытий.

. Все они войдут в таблицу покрытий.

Строим таблицу покрытий (табл. 2.9)

Таблица 2.9 – Таблица покрытий

| Простые импликанты | Минтермы функции

| ||||||||

| f1 | f2 | f2 | f2 | f1 | f2 | f1 | f1 | ||

| A | 0x0 (f2) | v | v | ||||||

| B | 01x (f2) | v | v | ||||||

| C | 1x1 (f1) | v | v | ||||||

| D | 11x (f1) | v | v | ||||||

| E | 000 (f1, f2) | v | v | ||||||

| F | 101 (f1, f2) | v | v |

Ядро функции составляют простые импликанты B, D, E, F. Остальные импликанты являются лишними и не будут входить в тупиковую и минимальную ДНФ. Т.е. МДНФ функции  будет состоять только из ядра.

будет состоять только из ядра.

МДНФ  :

:  .

.

По МДНФ функции  строим МДНФ

строим МДНФ  и МДНФ

и МДНФ  .

.

МДНФ  :

:  .

.

МДНФ  :

:  .

.

Аппаратурные затраты по критерию Квайна без учета инверсий и с учетом объединения общих частей выражения (  ) составляют Cb =16.

) составляют Cb =16.

Попробуем для минимизации рассмотренной системы воспользоваться первым подходом, предполагающим минимизацию каждой функции отдельно.

Карта Карно для функции  представлена на рис. 2.59

представлена на рис. 2.59

Рисунок 2.59 – Карта Карно для функции

Карта Карно для функции  представлена на рис. 2.60

представлена на рис. 2.60

МДНФ  :

:  .

.

Рисунок 2.60 – Карта Карно для функции

МДНФ  :

:  .

.

Общих частей у МДНФ функций нет, в результате аппаратурные затраты по критерию Квайна без учета инверсий составляют Cb =20. По оценке аппаратурных затрат видно, что раздельная минимизация функций системы уступает совместной, хотя последняя является более трудоемкой.

2.3 Комбинационные компоненты средней степени интеграции

Сумматоры

Каким образом выполняется суммирование двух положительных чисел в двоичном коде? Например, 3+5=8:

1 1

+0101

1000.

Существует большое многообразие сумматоров в [4] приведено 9 типов сумматоров, рассмотрим самые простые из них.

Таблица 2.12 – Таблица истинности для полного сумматора

| a | b | Cin | S | Cout |

.

.

Выполнив минимизацию Cout по карте Карно, получим;

.

.

Сin – перенос из предыдущего младшего разряда,

Cout – перенос с следующий старший разряд.

На рис. 2.67 представлена схема одноразрядного полного сумматора.

Рисунок 2.67 – Схема одноразрядного полного сумматора

Для последовательного выполнения операции сложения (разряд за разрядом) используется один полный сумматор, общий для всех разрядов. Для выполнения операции операнды и перенос подаются на него последовательно, начиная с младших разрядов рис. (2.68).

Рисунок 2.68 – Схема последовательного сумматора

Последовательный сумматор имеет небольшие аппаратурные затраты, но требует большого времени выполнения операции. Более быстродействующим будет параллельный сумматор с последовательным переносом. Для примера рассмотрим четырехразрядный параллельный сумматор с последовательным переносом (рис. 2.69).

Рисунок 2.69 – Схема параллельного сумматора с последовательным переносом

Для каждого разряда в этой схеме используется отдельный одноразрядный полный сумматор. В младший разряд (a0, b0) переноса нет, поэтому Сin=0. На каждый последующий разряд подеется перенос из предыдущего. Хоть сумматор и называется параллельным, на самом деле все разряды обрабатываются не точно одновременно, а только после формирования переноса для данного разряда. Отсюда следует, что быстродействие устройства определяется суммой задержек передачи сигнала переноса с младшего разряда на выход сумматора старшего разряда.

Мультиплексоры

Мультиплексором (от английского слова multiplex - многократный) называется комбинационный узел, способный коммутировать (передавать) информацию с нескольких входов на один выход. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. На рисунке 2.70 приведен пример мультиплексора 2 в 1. Мультиплексоры имеют две группы входов и один, реже два - взаимодополняющих выхода F и  . Входы

. Входы  являются информационными, вход А - управляющими (адресными). Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен с выходным каналом. Условно мультиплексор обозначается MX или MUX.

являются информационными, вход А - управляющими (адресными). Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен с выходным каналом. Условно мультиплексор обозначается MX или MUX.

Рисунок 2.70 – Условное обозначение мультиплексора MX 2 в 1

В таблице 2.13 приведены значения адресов для соответствующих входов.

Таблица 2.13 – Информационные входы и их адреса

| Информационные входы | Адреса информационных входов А |

| D0 | |

| D1 |

На рис. 2.71 приведен механический аналог мультиплексора 2 в 1. Когда А=0, коммутируется D0 и F , когда А=1, коммутируется D1 и F.

Рисунок 2.71 – Механический аналог мультиплексора MX 2 в 1

В таблице 2.14 представлена таблица истинности MX 2 в 1.

Таблица 2.14 – Таблица истинности MX 2 в 1

| А | D0 | D1 | F |

Выполнив минимизацию по карте Карно функции F, получим выражение:

На рисунке 2.72 приведена структура мультиплексора 2 в 1.

Рисунок 2.72 – Структура мультиплексора MX 2 в 1

На рисунке 2.73 приведен пример мультиплексора 4 в 1.

Рисунок 2.73 – Условное обозначение стробируемого MUX 4 в 1

Входы  являются информационными, входы

являются информационными, входы  - управляющими (адресными). Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен с выходным каналом. В таблице 2.15 приведены значения адресов для соответствующих входов.

- управляющими (адресными). Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен с выходным каналом. В таблице 2.15 приведены значения адресов для соответствующих входов.

Таблица 2.15 – Информационные входы и их адреса в MUX 4 в 1

| Информационные входы | Адреса информационных входов А1 А2 |

| D0 | 0 0 |

| D1 | 0 1 |

| D2 | 1 0 |

| D3 | 1 1 |

Разрешающий (стробирующий) вход V управляет одновременно всеми информационными входами независимо от состояния адресных входов. Запрещающий сигнал на этом входе блокирует действие всего устройства. Наличие разрешающего входа V расширяет функциональные возможности мультиплексоров, позволяя синхронизировать его работу с работой других узлов.

На рисунке 2.74 приведен механический аналог мультиплексора MUX 4 в 1. Если V=0, то F=0, т.е. будет выполняться коммутация с нулем. Если V=1, то F будет коммутироваться с каналом в соответствии с поданным адресом на входы А1 А2, т.е. мультиплексор будет выполнять свою основную функцию..

Рисунок 2.74 – Механический аналог мультиплексора MUX 4 в 1

Разрешающий вход используется также при наращивании числа входных информационных каналов. Мультиплексор на рисунке 2.73 реализует функцию, представленную в табл. 2.16.

Таблица 2.16 – Таблица истинности MUX 4 в 1

| V | А1 | А2 | D0 | D1 | D2 | D3 | F |

| x | x | x | |||||

| x | x | x | |||||

| x | x | x | |||||

| x | x | x | |||||

| x | x | x | |||||

| x | x | x | |||||

| x | x | x | |||||

| x | x | x | |||||

| x | x | x | x | x | x |

Функция выхода мультиплексора MUX 4 в 1 будет иметь вид:

Демультиплексоры

Демультиплексоры (DMX) выполняют преобразования информации, обратное преобразованию информации в мультиплексоре. Демультиплексор выполняет коммутацию одного входного информационного канала с одним из нескольких выходных каналов. Число выходных каналов демультиплексора равно  , где n - число адресных входов. В качестве демультиплексоров можно использовать дешифраторы. Демультиплексор из 1 в 2 представлен на рис. 2.76.

, где n - число адресных входов. В качестве демультиплексоров можно использовать дешифраторы. Демультиплексор из 1 в 2 представлен на рис. 2.76.

Рисунок 2.76 – Условное обозначение мультиплексора DMX 1 в 2

В таблице 2.17 приведены значения адресов для соответствующих выходов.

Таблица 2.17 – Выходы и их адреса в DMX 1 в 2

| Информационные выходы | Адреса информационных выходов А |

| F0 | |

| F1 |

На рис. 2.77 приведен механический аналог демультиплексора 1 в 2. Когда А=0, коммутируется D и F0 , когда А=1, коммутируется D и F1.

Рисунок 2.77 – Механический аналог мультиплексора DMX 1 в 2

В таблице 2.18 представлена таблица истинности DMX 1 в 2.

Таблица 2.18 – Таблица истинности DMX 2 в 1

| А | D | F0 | F1 |

| 0/z | |||

| 0/z | |||

| 0/z | |||

| 0/z |

Запись 0/z означает, что на выходе может быть либо 0, либо z, 0 и z соответствуют различным таблицам истинности. Символ z означает состояния высокого импеданса или высокого сопротивления на выходе (обрыв связи).

Вне зависимости от того, что на выходе (0 либо z), функция реализуется уравнениями:

,

,

.

.

На рисунке 2.78 приведена структура демультиплексора 1 в 2.

Рисунок 2.78 – Структура демультиплексора DMX 1 в 2

Дешифраторы

Комбинационная логическая схема, преобразующая поступающий на её входы двоичный позиционный код в активный сигнал только на одном из выходов (унитарный код), называется дешифратором (от английского decoder). Если количество двоичных разрядов дешифрируемого кода обозначить через n, то число выходов дешифратора равно 2n. На рисунке 2.79 изображен дешифратор из 2 в 4. Слева – входы 1, 2 – степени двойки, условно будем их обозначать D1, D2 далее для удобства. V – стробирующий вход. Справа – выходы 0, 1, 2, 3 – десятичный эквивалент подаваемого на входы кода, для удобства будем далее их обозначать Q0, Q1, Q2, Q3.

Рисунок 2.79 – Условное обозначение дешифратора 2 в 4

Функции дешифратора представлены в таблице 2.19.

Таблица 2.19 – Таблица истинности DC 2 в 4

| D2, D1 | Q0, Q1, Q2, Q3. |

| 2 1 | 0 1 2 3 |

| 0 0 | 1 0 0 0 |

| 0 1 | 0 1 0 0 |

| 1 0 | 0 0 1 0 |

| 1 1 | 0 0 0 1 |

Записав МДНФ для каждой функции выхода, получим следующие уравнения:

,

,

,

,

,

,

.

.

С учетом стробирующего сигнала уравнения имеют следующий вид:

,

,

,

,

,

,

.

.

В ЭВМ с помощью дешифраторов осуществляется выборка необходимых ячеек ЗУ (запоминающих устройств), расшифровка кодов операций с выдачей соответствующих управляющих сигналов, реализация булевых функций.

Если элементы И в схеме дешифратора (рис. 2.80) заменить на элементы Шеффера (И-НЕ), то получим дешифратор с инверсными выходами, что показывается на выходах кружками. Так как дешифраторы реализуют булевы функции, являющиеся конституэнтами единицы, то любую булеву функцию можно реализовать на базе дешифратора c прямыми выходами и логических схем ИЛИ, а также на базе дешифратора c инверсными выходами и логических схем И-НЕ (рис 2.81).

а) б)

Рисунок 2.81- Реализация булевой функции y на основе дешифратора с прямыми выходами (a) и инверсными выходами (б)

Дешифраторы можно использовать в качестве демультиплексоров, если V использовать как информационный вход, а D1, D2 - как адресные.

Шифраторы

В условных обозначениях шифраторов используются буквы CD (от слова coder) (рис. 2.82).

Рисунок 2.82 – Условное обозначение шифратора 4 в 2

Таблицей, описывающей функционирование шифратора, является табл. 2,19, с той лишь разницей, что  являются входными булевыми переменными, а

являются входными булевыми переменными, а  - выходными булевыми функциями шифратора. Функция шифратора представлена в таблице 2.20.

- выходными булевыми функциями шифратора. Функция шифратора представлена в таблице 2.20.

Таблица 2.20 – Таблица истинности CD

| Q0, Q1, Q2, Q3. | D1, D2 |

| 1 0 0 0 | 0 0 |

| 0 1 0 0 | 0 1 |

| 0 0 1 0 | 1 0 |

| 0 0 0 1 | 1 1 |

| на всех остальных наборах | 0 0 |

Записав МДНФ для каждой функции выхода, получим следующие уравнения:

Структура шифратора представлена на рис. 2.83.

Рисунок 2.83 – Структура шифратора 4 в 2

Уровень представления схемы, в которой используются мультиплексоры, демультиплексоры, шифраторы, дешифраторы, сумматоры и т.п., называется функционально-блочным.

Уровень представления схемы, состоящей из логических элементов (вентилей), называется логическим.

3 Последовательностная логика

Особенность последовательностной схемы (в отличии от комбинационной) состоит в том, что значения на выходах схемы в текущий момент времени зависят не только от того, какие значения были поданы на входы, но и в каком состоянии находилась схема в предыдущий момент времени.

Представителями последовательностных схем являются триггеры. Триггер это элементарный автомат, содержащий элемент памяти (запоминающий элемент) и схему управления элементом памяти. На схему управления подают входные сигналы (информационные) и сигналы обратной связи с выхода элемента памяти (рис. 3.1). В некоторых простейших триггерах схема управления может отсутствовать.

Состояние выхода триггера определяется элементом памяти, сигналом на его прямом выходе Q. Обычно триггер имеет и инверсный выход  , иногда он обозначается Q*.

, иногда он обозначается Q*.

Рисунок 3.1– Структурная схема триггера

ЗЭ – запоминающий элемент;

КС – комбинационная схема управления;

x1,..., xn – информационные входы триггера;

С1, Сm – синхронизующие входы;

Q,  – соответственно прямой и инверсный выходы триггера;

– соответственно прямой и инверсный выходы триггера;

f1, f2 – функции возбуждения ЗЭ.

На рис. 3.2 приведены примеры запоминающих элементов. Они состоят из вентилей И-НЕ или ИЛИ-НЕ с обратными связями.

Рисунок 3.2 – Примеры запоминающих элементов

Классификация триггеров проводится по закону логического функционирования (триггеры типа RS, R*S*, JK, J*K* и другие), по способу записи информации в триггер (асинхронные и синхронные), по способу восприятия триггером тактовых сигналов (управляемые уровнями и управляемые фронтами), по структуре (одноступенчатые и двухступенчатые).

3.1 Асинхронные триггеры

Асинхронные триггеры – триггеры, у которых переход в новое состояние вызывается изменениями информационных входных сигналов. Т.е. без тактирующих или синхронизирующих сигналов.

3.1.1 RS-триггер

Триггером типа RS называется триггер с двумя устойчивыми состояниями равновесия и двумя информационными входами (рис. 3.3). Вход S (Set) служит для установки триггера в «1», вход R (Rеsеt) для установки в «0». Одновременная подача двух активных сигналов на входы R и S запрещена, т.е. R  S

S  . Подача двух нулей на входы триггера сохраняет его внутреннее состояние. Активным значением сигнала на входе является уровень 1. Вход в этом случае считается прямым. Если активным значением сигнала на входе является нуль, то такой вход считается инверсным. Обычно инверсный вход обозначается символом звездочки (*). Триггеры с инверсными входами будут рассмотрены далее.

. Подача двух нулей на входы триггера сохраняет его внутреннее состояние. Активным значением сигнала на входе является уровень 1. Вход в этом случае считается прямым. Если активным значением сигнала на входе является нуль, то такой вход считается инверсным. Обычно инверсный вход обозначается символом звездочки (*). Триггеры с инверсными входами будут рассмотрены далее.

Рисунок 3.3 – Структура и условное обозначение асинхронного RS-триггера

Для полного описания триггера достаточно задать закон его функционирования. Поскольку триггер является элементарным автоматом, то закон его функционирования задается полной таблицей переходов (ПТП) (таблица 3.1), с помощью которой можно построить сокращенную таблицу переходов (таблица 3.2). В таблице t и t+1 – соседние моменты времени, в пределах которых рассматриваются переходы состояний триггера (переходы из состояния Q в момент времени t в состояние Q в момент времени t+1). Обозначается такой переход условно  .

.

Таблица 3.1 – Полная таблица переходов RS-триггера

| t | t+1 | |||

| R | S | Q | Q | |

| X | ||||

| X |

Если разбить таблицу 3.1 по две строки сверху, видно, что значения R и S в парах строк одинаковые. Опустив значения столбца  , получим сокращенную таблицу переходов (СТП).

, получим сокращенную таблицу переходов (СТП).

Таблица 3.2 – Сокращенная таблица переходов RS-триггера

| R | S | Q(t+1) |

| Q(t) | ||

| X |

В таблице 3.3 представлена дополнительная таблица переходов (ДТП). Ее легко получить из ПТП. В первом столбце ДТП записываются входы триггера, в остальных столбцах – все возможные переходы состояний триггера  : «0-0», «0-1», «1-0», «1-1». В ПТП прослеживаются все эти переходы и помечаются (в нашем случае красной цифрой). Цифра обозначает номер перехода в ДТП. Затем в соответствии с расставленными метками из ПТП в столбцы ДТП записываются значения, подаваемые на входы R и S на данном переходе.

: «0-0», «0-1», «1-0», «1-1». В ПТП прослеживаются все эти переходы и помечаются (в нашем случае красной цифрой). Цифра обозначает номер перехода в ДТП. Затем в соответствии с расставленными метками из ПТП в столбцы ДТП записываются значения, подаваемые на входы R и S на данном переходе.

Таблица 3.3 – Дополнительная таблица переходов RS-триггера

| Вход | 1 «0-0» | 2 «0-1» | 3 «1-0» | 4 «1-1» |

| R | 0 1 | 0 0 | ||

| S | 0 0 | 0 1 |

Матрица переходов (МП) это фактически повернутая ДТП (таблица 3.4). Строки ДТП являются столбцами матрицы. Матрица переходов показывает, какие значения сигналов нужно подавать на входы триггера для осуществления указанного перехода состояний Q(t)-Q(t+1). Пары идентичных значений в ячейке ДТП заменяются одним значением в МП. Пары различных значений в ячейке ДТП заменяются одной буквой, например b1, Так как на переходе «0-0» сигнал на входе R может быть равен или 0, или 1, то его обозначают через неопределенный коэффициент b1,  . Аналогично для сигнала на входе S для перехода «1-1» ставится b2,

. Аналогично для сигнала на входе S для перехода «1-1» ставится b2,  В различных ячейках МП, где необходимо ставить буквы, должны быть либо различные буквы, либо одна и та же буква, но с различными индексами. Это удобно при синтезе триггеров, чтобы не возникало путаницы. Синтез будет рассмотрен позже.

В различных ячейках МП, где необходимо ставить буквы, должны быть либо различные буквы, либо одна и та же буква, но с различными индексами. Это удобно при синтезе триггеров, чтобы не возникало путаницы. Синтез будет рассмотрен позже.

Таблица 3.4 – Матрица переходов RS-триггера

| Q(t)-Q(t+1) | R | S |

| 0-0 | b1 | |

| 0-1 | ||

| 1-0 | ||

| 1-1 | b2 |

Еще одним способом описания триггеров является граф переходов (рис. 3.4). Вершинам соответствуют состояния триггеров, а дугам – переходы между состояниями. Состояние определяется значением выхода Q. Когда Q=0, считается, что триггер находится в состоянии а0, когда Q=1, считается, что триггер находится в состоянии а1. На дугах записываются условия того или иного переходов.

Рисунок 3.4 – Граф переходов RS-триггера

Аналитические выражения для условий переходов получают по ДТП.

Для дуги, что выходит из а0 и входит в а0 (то есть петли) – для перехода «0-0»:  ;

;

для дуги из а0 в а1 – для перехода «0-1»:  ;

;

для дуги из а1 в а0 – для перехода «1-0»:  ;

;

для дуги из а1 в а1 – для перехода «1-1»:  .

.

Функция переходов триггера  в момент t+1 может быть задана с помощью карт Карно (рис. 3.5), которые строятся по полной таблице переходов триггера.

в момент t+1 может быть задана с помощью карт Карно (рис. 3.5), которые строятся по полной таблице переходов триггера.

Рисунок 3.5 – Карта Карно для функции переходов RS-триггера

Используя карту Карно, можно найти минимальную КНФ булевой функции для описания функционирования RS-триггера (характеристическую функцию переходов)  .

.

Данное выражение соответствует схеме RS-триггера, изображенного на рис. 3.3.

3.1.2 R*S*-триггер (RS-триггер с инверсными входами)

Триггером типа R*S*-называется триггер с двумя устойчивыми состояниями равновесия и двумя информационными входами (рис. 3.6). Вход S* (Set) служит для установки триггера в «1», вход R* (Rеsеt) для установки в «0». Активным значением сигнала на входе является уровень 0. Вход в этом случае считается инверсным. Инверсный вход обозначается символом звездочки (*). Одновременная подача двух активных сигналов на входы R* и S* запрещена, т.е. R*  S*

S*  . Подача двух единиц на входы триггера сохраняет его внутреннее состояние.

. Подача двух единиц на входы триггера сохраняет его внутреннее состояние.

Рисунок 3.6 – Структура и условное обозначение асинхронного R*S*-триггера

Полная таблица переходов (ПТП) (таблица 3.5), с помощью которой можно построить сокращенную таблицу переходов (таблица 3.6). В таблице t и t+1 – соседние моменты времени, в пределах которых рассматриваются переходы состояний триггера (переходы из состояния Q в момент времени t в состояние Q в момент времени t+1). Обозначается такой переход условно  .

.

Таблица 3.5 – Полная таблица переходов R*S*-триггера

| t | t+1 | |||

| R* | S* | Q | Q | |

| X | ||||

| X | ||||

Получим сокращенную таблицу переходов (СТП) (таблица 3.6).

Таблица 3.6 – Сокращенная таблица переходов R*S*-триггера

| R* | S* | Q(t+1) |

| X | ||

| Q(t) |

Обратите внимание, что столбец Q(t+1) в сокращенной таблице переходов R*S*-триггера, перевернут относительно того же столбца RS-триггера. Это справедливо для всех одноименных триггеров с прямыми и инверсными входами. Зная СТП триггера с прямыми входами, можно легко получить СТП одноименного триггера с инверсными входами.

В таблице 3.7 представлена дополнительная таблица переходов (ДТП).

Таблица 3.7 – Дополнительная таблица переходов R*S*-триггера

| Вход | 1 «0-0» | 2 «0-1» | 3 «1-0» | 4 «1-1» |

| R* | 0 1 | 1 1 | ||

| S* | 1 1 | 0 1 |

Матрица переходов (МП) представлена в таблице 3.8).

Таблица 3.8 – Матрица переходов R*S*-триггера

| Q(t)-Q(t+1) | R* | S* |

| 0-0 | b1 | |

| 0-1 | ||

| 1-0 | ||

| 1-1 | b2 |

Граф переходов представлен на рис. 3.7.

Рисунок 3.7 – Граф переходов R*S*-триггера

Аналитические выражения для условий переходов получают по ДТП.

Для дуги, что выходит из а0 и входит в а0 (то есть петли) – для перехода «0-0»:  ;

;

для дуги из а0 в а1 – для перехода «0-1»:  ;

;

для дуги из а1 в а0 – для перехода «1-0»:  ;

;

для дуги из а1 в а1 – для перехода «1-1»:  .

.

Функция переходов триггера  в момент t+1 может быть задана с помощью карт Карно (рис. 3.8), которые строятся по полной таблице переходов триггера.

в момент t+1 может быть задана с помощью карт Карно (рис. 3.8), которые строятся по полной таблице переходов триггера.

Рисунок 3.8 – Карта Карно для функции переходов R*S*-триггера

Используя карту Карно, можно найти минимальную ДНФ булевой функции для описания функционирования R*S*-триггера (характеристическую функцию переходов)  .

.

.

.

Данное выражение соответствует схеме R*S*-триггера, изображенного на рис. 3.6.

3.1.3 JK-триггер

Триггером типа JK называется триггер с двумя устойчивыми состояниями равновесия и двумя информационными входами (рис. 3.9). Вход J (Jarк) служит для установки триггера в «1», вход K (Кill) для установки в «0». Активным значением сигнала на входе является уровень 1. Одновременная подача двух активных сигналов на входы K и J не запрещена, при этом на выходе появляется инверсное значение состояния триггера  . Подача двух нулей на входы триггера сохраняет его внутреннее состояние.

. Подача двух нулей на входы триггера сохраняет его внутреннее состояние.

Рисунок 3.9 – Условное обозначение асинхронного JK-триггера

Полная таблица переходов (ПТП) (таблица 3.9), с помощью которой можно построить сокращенную таблицу переходов (таблица 3.10).

Таблица 3.9 – Полная таблица переходов JK -триггера

| t | t+1 | |||

| K | J | Q | Q | |

Получим сокращенную таблицу переходов (таблица 3.10).

Таблица 3.10 – Сокращенная таблица переходов JK-триггера

| K | J | Q(t+1) |

| Q(t) | ||

|

В таблице 3.11 представлена дополнительная таблица переходов.

Таблица 3.11 – Дополнительная таблица переходов JK-триггера

| Вход | 1 «0-0» | 2 «0-1» | 3 «1-0» | 4 «1-1» |

| K | 0 1 | 0 1 | 1 1 | 0 0 |

| J | 0 0 | 1 1 | 0 1 | 0 1 |

Матрица переходов представлена в таблице 3.12.

Таблица 3.12 – Матрица переходов J K-триггера

| Q(t)-Q(t+1) | K | J |

| 0-0 | b1 | |

| 0-1 | b2 | |

| 1-0 | b3 | |

| 1-1 | b4 |

Граф переходов представлен на рис. 3.10.

Рисунок 3.10 – Граф переходов JK-триггера

Функция переходов триггера  в момент t+1 может быть задана с помощью карт Карно (рис. 3.11), которые строятся по полной таблице переходов триггера.

в момент t+1 может быть задана с помощью карт Карно (рис. 3.11), которые строятся по полной таблице переходов триггера.

Рисунок 3.11 – Карта Карно для функции переходов JK-триггера

Используя карту Карно, можно найти минимальную ДНФ булевой функции для описания функционирования JK-триггера (характеристическую функцию переходов)  .

.

.

.

3.1.4 J*K*-триггер

Триггером типа J*K* называется триггер с двумя устойчивыми состояниями равновесия и двумя информационными входами (рис. 3.12). Вход J* в «1», вход *K для установки в «0». Активным значением сигнала на входе является уровень 0. Одновременная подача двух активных сигналов на входы K* и J* не запрещена, при этом на выходе появляется инверсное значение состояния триггера  . Подача двух единиц на входы триггера сохраняет его внутреннее состояние.

. Подача двух единиц на входы триггера сохраняет его внутреннее состояние.

Рисунок 3.12 – Условное обозначение асинхронного J*K*-триггера

Полная таблица переходов (таблица 3.13), с помощью которой можно построить сокращенную таблицу переходов (таблица 3.14).

Таблица 3.13 – Полная таблица переходов J*K* -триггера

| t | t+1 | |||

| K* | J* | Q | Q | |

Получим сокращенную таблицу переходов (таблица 3.14).

Таблица 3.14 – Сокращенная таблица переходов J*K*-триггера

| K* | J* | Q(t+1) |

| ||

| Q(t) |

Матрица переходов представлена в таблице 3.15.

Таблица 3.15 – Матрица переходов J*K*-триггера

| Q(t)-Q(t+1) | K* | J* |

| 0-0 | b1 | |

| 0-1 | b2 | |

| 1-0 | b3 | |

| 1-1 | b4 |

3.1.5 D-триггер

Триггером типа D (Delay - задержка)называется триггер с двумя устойчивыми состояниями равновесия и одним информационным входом D (рис. 3.13). Значения, поступающие на вход D, записываются на выход Q, т.е. триггер работает как повторитель.

Дата добавления: 2017-12-05; просмотров: 30685;