Основные функциональные блоки и узлы

Блок времени опережения (БВО) (Рис. 2.3.2.4 приложения)

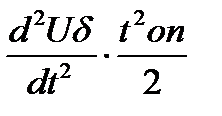

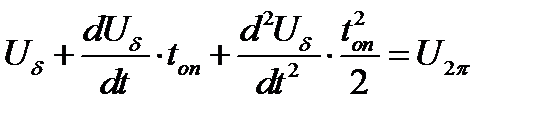

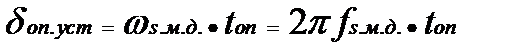

Блок БВО определяет время опережения (время подачи импульса на включение выключателя) с учетом того, что в ходе подгонки скольжения изменение частоты вращения генератора носит равноускоренный или равнозамедленный характер. Для этого схема БВО рассчитывает угол опережения по заданному значению уставки времени опережения tоп по текущей угловой скорости и ускорению вращения.

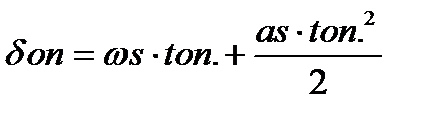

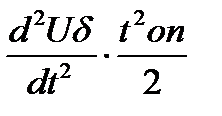

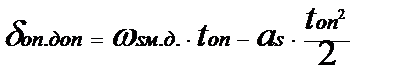

Уравнение изменения текущего угла между напряжениями с учетом равноускоренного вращения в угловых параметрах:

Здесь: ωs– угловая скоростпь скольжения,

аs- ускорение скольжения.

tоп= tвкл.В+Δt– уставка по времени опережения

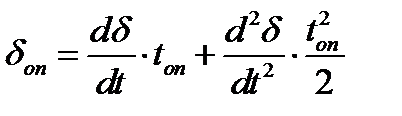

Выразим δоп в параметрах текущего угла δ между напряжениями:

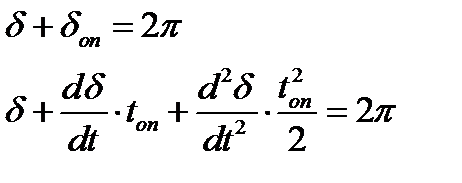

Условие срабатывания БВО определится из уравнения:

Когда текущий угол δ станет равным δоп, на выходе БВО появится импульс, разрешающий включение. Импульс сформируется за время tоп до наступления 360°.

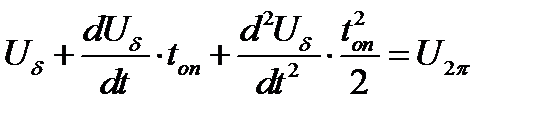

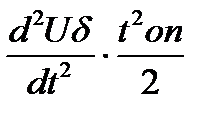

Схема БВО использует напряжение Uδ= кпр·δ выхода преобразователя ПФ и решает это уравнение относительно tоп.

То же самое уравнение срабатывания блока БВО, выраженное в напряжении схемы блока:

Каждое слагаемое уравнения – это отдельный узел схемы БВО:

· Uδ – вход с преобразователя ПФ,

·  - дифференцирующий ОУ D1,

- дифференцирующий ОУ D1,

·  - дифференцирующий ОУ D2,

- дифференцирующий ОУ D2,

· U2π - напряжение смещения компаратора D3.

Схема БВО состоит из двух дифференцирующих усилителей D1 и D2 и компаратора D3, который собственно и решает уравнение.

На компаратор D3 подаются:

· Uδвыхода с ПФ (пропорционального углу δ),

· выход дифференцирующего ОУ D1,

· выход дифференцирующего ОУ D2,

· напряжение смещения.

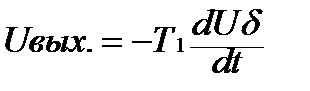

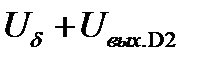

На вход дифференцирующего операционного усилителя D1подается напряжение с преобразователя ПФ:

Uвх D1=Uδ

Выход дифференцирующего усилителя Uвых D1, – производная Uδ´ входного напряжения равная  .

.

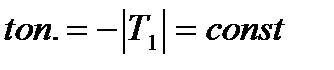

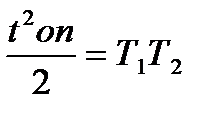

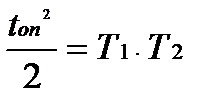

Из cравнения Uвых D1 cо вторым слагаемым уравнения  следует,что

следует,что

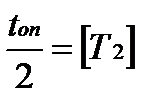

. Поскольку постоянная дифференцирования Т1 = R6˖C3определяется параметрами элементов R6и С3 внешней схемы D1, то время опережения здесь так же постоянно и не зависит от скольжения, как и в предыдущей модификации автосинхронизатора. Знак (-) указывает, что момент срабатывания выбирается перед наступлением угла 360º периода биений.

. Поскольку постоянная дифференцирования Т1 = R6˖C3определяется параметрами элементов R6и С3 внешней схемы D1, то время опережения здесь так же постоянно и не зависит от скольжения, как и в предыдущей модификации автосинхронизатора. Знак (-) указывает, что момент срабатывания выбирается перед наступлением угла 360º периода биений.

Уставка tоп регулируетсяется переменным резистором R6операционного усилителя D1.

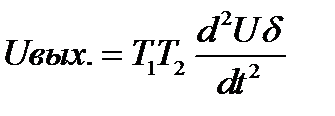

На вход дифференцирующего операционного усилителя D2подается напряжение выхода усилителя ОУ D1

Uвх D2= Uвых D1= Uδ´

Выход ОУ D2 – вторая производная Uδ´´ входного напряжения блока, равная

Из сравнения Uвых D2 cтретьим слагаемым уравнения  следует, что

следует, что

. Постоянная дифференцирования Т2 = R14˖C10 операционного усилителя D2 в равенстве

. Постоянная дифференцирования Т2 = R14˖C10 операционного усилителя D2 в равенстве  соответствует сомножителю

соответствует сомножителю  и регулирование уставки tоп здесь не предусматривается.

и регулирование уставки tоп здесь не предусматривается.

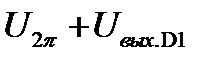

Значение напряжения смещения U2πдля компаратора задается резистором R17.

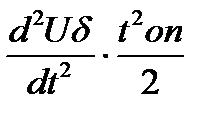

В результате имеются 4 величины напряжений для решения уравнения

На компараторе D3 сравниваются две суммы:  и

и  (значение UвыхD1 отрицательно). Уравнение решается в момент срабатывания D3, а компаратор сработает, когда сумма

(значение UвыхD1 отрицательно). Уравнение решается в момент срабатывания D3, а компаратор сработает, когда сумма  станет меньше суммы

станет меньше суммы  , и напряжение его выхода изменит полярность на положительную. Далее импульс выходного напряжения D3 пропускается через дифференцирующую R–Cцепь, чтобы на выходе блока БВО получить сигнал «А» длительностью приблизительно 30 мс.

, и напряжение его выхода изменит полярность на положительную. Далее импульс выходного напряжения D3 пропускается через дифференцирующую R–Cцепь, чтобы на выходе блока БВО получить сигнал «А» длительностью приблизительно 30 мс.

Там же, в БВО формируется импульс «Р» на запрет действия СА-1 при углах

120° < δ < 240°.

Блок запрета (БЗ)

Блок запрета содержит функциональные узлы, контролирующие условия синхронизации: допустимое отклонение амплитуд и отклонение частоты скольжения напряжения. Там же организуются дополнительные сигналы блокирования.

Узел сравнения амплитуд (Рис. 2.3.2.5 приложения)

В узле через выпрямители включаются встречно друг другу два напряжения вторичных обмоток входных транформаторов TV1и TV2, преобразующих Uг и Uс.

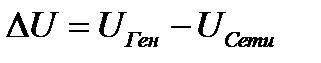

На резисторе R24выделяется

При соотношении напряжений UГен> UСети, ΔU > 0 положительно.

При соотношении напряжений UГен< UСети, ΔU < 0 отрицательно.

Потенциал точки «1» (ΔU) сравнивается с уставкой по отклонению ΔUуст на двух компараторах D1и D2. Из них D1работает при ΔU< 0, D2при ΔU> 0. Набор сопротивлений R8, R11 - R14 вместе с переключателем – узел задания уставки допустимой разности амплитуд, общий для обоих компараторов.

При срабатывании любого из компараторов (отклонение напряжения превышает уставку, включение запрещено), на его выходе появляется “1”. Выходные сигналы компараторов поступают на микросхему D3.1 с логикой «ИЛИ-НЕ». Туда же подается сигнал «Р» из БВО (запрет работы при 120° < δ< 240°). Выход D3.1,сигнал «D», будет равен “0” и, следовательно, запрещать работу СА-1, если хотя бы один из входных сигналов равен «1». Это может быть в случае, когда ΔU> ΔUуставки и всегда, на каждом периоде биений при углах 120° < δ< 240°. Сигнал «D» передается в логическую схему (БЛ) автосинхронизатора.

Узел контроля максимально-допустимой разности частот (Рис. 2.3.2.6)

Автосинхронизатор запрещает включение при частоте скольжения, которая будет больше максимально-допустимой fsм.д. в момент смыкания контактов выключателя. Значение частоты скольжения контролируется через максимально допустимый угол опережения, который вычисляется по частоте скольжения в момент срабатывания автосинхронизатора и корректируется по измеренному в этот же момент ускорению скольжения.

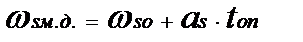

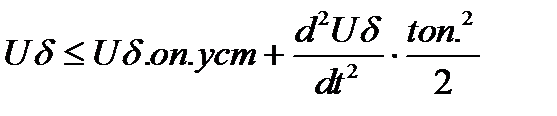

Максимально допустимая угловая скорость в момент включения выключателя должна быть:

ωsoи аs - параметры скольжения в момент срабатывания СА-1.

Максимально допустимый угол опережения:

Реально уставка максимально – допустимой частоты скольжения fsм.д. задается без учета ускорения

и корректируется схемой на величину ускорения.

В схеме узла контроля разности частот на инвертирующий вход компаратора D5 подается текущее значение Uδиз ПФ, на неинвертирующий вход – напряжение уставки с делителя R2, R5,….R18. Туда же, на неинвертирующий вход подается с выхода усилителя D2 блока БВО напряжение Uδ" поправки на ускорение скольжения, равное

В момент выполнения неравенства

компаратор D5 срабатывает, на его выходе появляется «1». После диода VD19 на выходе узла формируется сигнал «В», который разрешает образование импульса на включение. Возврат сигнала произойдет при увеличении текущего угла δ > δоп уст на следующем периоде биений.

Ускорение скольжения учитывается поправкой к Uδоп.уст в схеме компаратора.

При  > 0 разрешенный угол δоп увеличится по сравнению с уставкой δоп. уст.

> 0 разрешенный угол δоп увеличится по сравнению с уставкой δоп. уст.

При  < 0 разрешенный угол δоп уменьшится.

< 0 разрешенный угол δоп уменьшится.

Выбор уставки по углу δоп уст производится из условия, что ток включения не должен быть больше Iном. генератора, и обусловлен этот ток временными погрешностями действия аппаратуры СА-1и выключателя генератора.

Таким образом, в блоке БВО задается время опережения tоп, которое корректируется в момент подачи импульса на включение с учетом ускорения скольжения, а в блоке запрета задается уставка δоп уст с поправкой на ускорение также в момент подачи импульса, - таким образом контролируется скольжение в момент смыкания контактов выключателя. Поправка повышает точность выбора момента включения и позволяет автосинхронизатору срабатывать при углах опережения, больших, чем в предыдущем АСТ-4.

Дополнительные блокирующие сигналы в БЗ

В БЗ, кроме сигналов «D» и «В» создаются дополнительные блокирующие сигналы.

Сигнал «С»дополнительно контролирует, что частота скольжения не превышает значения 1Гц и фиксирует переход напряжения биений через нуль (δ = 0). Последнее используется для возврата схемы «памяти» после нуля биений и подготовки схемы к следующему периоду биений.

Сигнал «Е» дополнительно контролирует разность амплитуд напряжений.

Эти сигналы служат дополнительным барьером от ложной работы СА-1, возможной из-за его слабой помехозащищенности.

Блок логики (БЛ)

(Рис. 2.3.2.8 приложения)

Блок логики формирует команду на включение с заданным временем опережения при соблюдении всех условий синхронизации. Выполнен БЛ с использованием интегральных микросхем.

Входами БЛ являются сигналы «А», «B», «D», «C» и «E», сформированные в блоках БВО и БЗ:

«А» - импульс на включение, подаваемый за время tопдо наступления нуля биений,

«B» - контроль допустимого скольжения по значению максимально-допустимого угла опережения,

«D» - контроль допустимой разности амплитуд UГен и UСети и одновременно контроль

прохождение Uδзоны 120° – 240° периода биений,

«C» - блокирование по значению скольжения fs>1Гц, кроме того, выдача импульса логического «0» сразу после наступления нуля биений,

«E» - дополнительный контроль разности амплитуд.

Выходные сигналы, дублированные:

- промежуточный F1 (F2),

- сигнал на включение FК1 (FК2).

В БЛ формируются 2 равноценных канала создания сигналов F1 и F2 и сигналов FК1и FК2.

Последовательность действия элементов БЛ проследим на релейно-контактной схеме блока логики, отражающей эту последовательность (Рис. 2.3.2.7).

В этой схеме логической «1» соответствует замкнутое состояние замыкающего контакта и разомкнутое состояние – размыкающего.

Сигнал F1 (F2) - выходной сигнал схемы памяти, запоминающий заданную последовательность изменения сигналов входа в текущем периоде биений. Он сформирован по логике «И» и станет равным логической «1» при условии (см. Рис. 2.3.2.8. приложения):

- входные сигналы«А», «B» и «D» равны логическому «0» (замкнуты размыкающие контакты),

- входные сигналы «C» и «E» равны логической «1» (замкнуты замыкающие контакты).

Согласно временнóму графику работы БЛ, в ходе увеличения угла биений от нуля и более сигнал F1 (F2) станет равным логической «1» при δ =120° с появлением сигнала «D» = «0», при условии, что «C» = «1», «E» = «1», а сигналы «А» и «B» равны «0». Сигналы «B» и «D» будут сразу подхвачены выходным сигналом F1 (F2).

Сигнал на включение FК1 (FК2), управляющий выходным реле СА-1, также собранный по логике «И», станет равным логической «1», когда все входные сигналы его тоже будут равны логической «1». При этом после 240° сигнал «D» станет = «1», а сигнал F1 (F2) останется равным «1». Теперь срабатывание схемы логики будет определяться очередностью появления положительных сигналов «А» и «В». Сигнал включения сформируется, если это произойдет в последовательности, - сначала появится логическая «1» сигнала «В», а затем сигнала «А».

Если «А» появится раньше, а это случится при fs>fsм.д., сигнал в этом периоде биений не сформируется. Не будет сигнала FК1 (FК2) и в том случае, если разность напряжений  превышает уставку, тогда сигнал «D» останется логическим «нулем» после 240°.

превышает уставку, тогда сигнал «D» останется логическим «нулем» после 240°.

Разбор схемы «памяти» (снятие подхвата сигнала F1 (F2) = «0») происходит в начале следующего периода биений по сигналу «C» = «0».

Длительность управляющего сигнала FК1 (FК2) определяется длительностью сигнала «А» = ~30мсек.

В узле включения СА-1 есть возможность выполнить подхват импульса на включение, который используется, если нет подхвата в схеме управления выключателем.

Там же, в БЛ, имеется узел выявления неисправности каналов формирования сигналов FК1(FК2), который фиксирует появление неравнозначных выходов FК1и FК2. В этом случае срабатывает и встает на самоподхват реле индикации неисправности и зажигает световой сигнал «неисправность». Возврат сигнала возможен после устранения неисправности кнопкой возврата на лицевой панели СА-1.

Дата добавления: 2017-01-13; просмотров: 1441;