Контрольні завдання до глави 9

9.1. Навести форми вхідного, проміжного та вихідного сигналів із указанням числових значень амплітуд гібридної схеми на рис.9.1.

Створити гібридні схеми на елементах ОЕТ-КМОН та записати повні таблиці дійсності для реалізації:

9.2. 2 АБО.

9.3. 3І.

9.4. 2 АБО-НІ.

9.5. 2І-НІ.

9.6. RS-тригера.

9.7. Розробити гібридну схему мультиплексора (2→1).

9.8. Розробити гібридну схему демультиплексора (1→2).

9.9. Розробити гібридну схему на двоканальних ОЕТ та КМОП інверторах і заповнити таблицю станів півсуматора.

9.10. Розробити гібридну схему на двоканальних ОЕТ та КМОП інверторах і заповнити таблицю станів однорозрядного суматора.

9.11. Розробити гібридну схему універсального мажоритарного елемента (2 з 3) та скласти її таблицю дійсності.

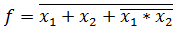

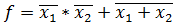

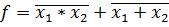

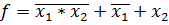

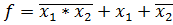

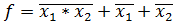

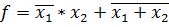

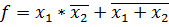

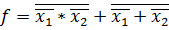

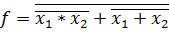

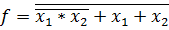

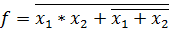

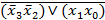

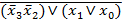

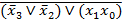

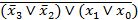

На прикладі рис.9.2 та 7.4, 7.5 побудувати гібридні програмовані схеми та записати повні таблиці дійсності на елементах ОЕТ з ЕНП-КМОН, які реалізують операції:

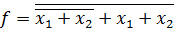

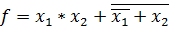

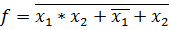

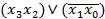

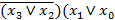

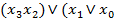

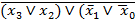

9.12.  .

.

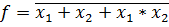

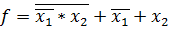

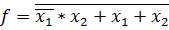

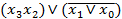

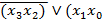

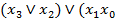

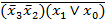

9.13.  .

.

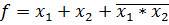

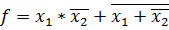

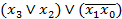

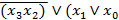

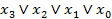

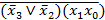

9.14.  .

.

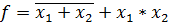

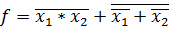

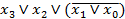

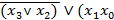

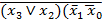

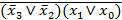

9.15.  .

.

9.16.  .

.

9.17.  .

.

9.18.  .

.

9.19.  .

.

9.20.  .

.

9.21.  .

.

9.22.  .

.

9.23.  .

.

9.24.  .

.

9.25.  .

.

9.26.  .

.

9.27.  .

.

9.28.  .

.

9.29.  .

.

9.30.  .

.

9.31.  .

.

9.32.  .

.

9.33.  .

.

9.34.  .

.

9.35.  .

.

9.36.  .

.

9.37.  .

.

9.38.  .

.

9.39.  .

.

9.40.

На прикладі рис.9.4 побудувати часові діаграми для гібридної схеми  , коли на вході діють наступні сигнали:

, коли на вході діють наступні сигнали:

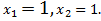

9.41 .

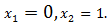

9.42 .

9.43  .

.

9.44. Використовуючи значення ємностей, розрахувати коефіцієнт передачі по напрузі одного ОЕТ зі схеми на рис.9.3.

9.45. Розрахувати загальний коефіцієнт передачі по напрузі в гібридній схемі Виключне АБО (рис.9.3).

Підсумки

Півсторіччя тому на кристалі кремнію вдалося розмістити лише один винайдений на той час біполярний транзистор. Це диво ХХ століття замінило диво ХІХ століття – електронну лампу. Сьогодні, на початку ХХІ століття на такому ж кристалі кремнію нові покоління інженерів-електронщиків створюють ВІС на мільярд транзисторів.

Тенденція до зростання ступеня інтеграції залишиться назавжди, проте це вже буде в іншому вимірі – в наносвіті.

В наносвіті можуть здійснюватись відомі ідеї схемотехнічної електроніки, в основі яких знаходиться використання вдосконалених транзисторів. Це можуть бути як транзистори на квантових точках, так і одноелектронні транзистори.

Разом з тим, наносвіт сприяє народженню нових ідей, пов’язаних з хвильовими властивостями електронів, з новими технологіями та матеріалами. Тому з’являються нові елементи і пристрої наноелектроніки, реалізовані або на геть нових принципах, або на добре відомих методах обробки інформації.

ЛІТЕРАТУРА

1. Драгунов В. П. и др. Основы наноэлектроники: Учебн. Пособие — М.: Логос, 2006. — 496с.

2. Находкін М. Г. Фізичні основи мікро- та наноелектроніки: Підручник.-К. — Видавничо-поліграфічний центр «Київський університет», 2005. — 431с.

3. Борисенко В. Е. и др. Наноэлектроника: Учебн. Пособие. — Минск: Бином. 2009, — 224с.

4. Головин Ю. Ч. Введение в наноэлектронику. — М.: Машиностроение, 2009, — 496с.

5. Мальцев П. П. Нано- и микросистемная техника. — М.: Техносфера. 2005, — 592с.

6. Пул. Ч. Нанотехнологии. — М.: Техносфера, 2006. — 336с.

7. Мальцев П. П. Наноматериалы. Нанотехнологии. Наносистемная техника. — М.: Техносфера, 2006 — 152с.

8. Чаплыгин Ю. А. Нанотехнологии в электроники. — М.: Техносфера. 2005. — 448с.

9. Reith M. Theoretical and Computational Nanotechnology. V. 10, Nanodevice Modeling and Nanoelectronics. — N.4.:ASP.2008 — 840p.

Таблиця варіантів виконання контрольного завдання з дисципліни «Основи наноелектронної схемотехніки».

| Варіант | Номер теми | |||||||||

| 5.17 | ||||||||||

| Номер контрольних завдань з конспекту | ||||||||||

| B.1 | 2.1 | 3.1 | 4.1 | 5.1 | 1+1 | 6.4 | 7.1 | 8.3 | 9.11 | |

| B.2 | 2.2 | 3.2 | 4.2 | 5.2 | 2+2 | 6.5 | 7.2 | 8.4 | 9.12 | |

| B.3 | 2.3 | 3.3 | 4.3 | 5.3 | 3+3 | 6.6 | 7.3 | 8.5 | 9.13 | |

| B.4 | 2.4 | 3.4 | 4.4 | 5.4 | 4+4 | 6.7 | 7.4 | 8.6 | 9.14 | |

| B.5 | 2.5 | 3.5 | 4.5 | 5.5 | 5+5 | 6.8 | 7.5 | 8.7 | 9.15 | |

| B.6 | 2.6 | 3.6 | 4.6 | 5.6 | 6+6 | 6.9 | 7.6 | 8.8 | 9.16 | |

| B.1 | 2.7 | 3.7 | 4.7 | 5.7 | 7+7 | 6.10 | 7.7 | 8.9 | 9.17 | |

| B.2 | 2.8 | 3.8 | 4.8 | 5.8 | 8+8 | 6.11 | 7.8 | 8.10 | 9.18 | |

| B.3 | 2.9 | 3.9 | 4.9 | 5.9 | 9+9 | 6.12 | 7.9 | 8.11 | 9.19 | |

| B.4 | 2.10 | 3.10 | 4.10 | 5.10 | 10+10 | 6.13 | 7.10 | 8.15 | 9.20 | |

| B.5 | 2.1 | 3.11 | 4.11 | 5.11 | 2+3 | 6.14 | 7.11 | 8.16 | 9.21 | |

| B.6 | 2.2 | 3.12 | 4.12 | 5.12 | 2+4 | 6.15 | 7.12 | 8.17 | 9.22 | |

| B.1 | 2.3 | 3.13 | 4.13 | 5.13 | 2+5 | 6.16 | 7.13 | 8.18 | 9.23 | |

| B.2 | 2.4 | 3.14 | 4.14 | 5.14 | 2+6 | 6.17 | 7.14 | 8.19 | 9.24 | |

| B.3 | 2.5 | 3.15 | 4.15 | 5.15 | 2+7 | 6.18 | 7.15 | 8.20 | 9.25 | |

| B.4 | 2.6 | 3.1 | 4.16 | 5.16 | 2+8 | 6.19 | 7.16 | 8.21 | 9.26 | |

| B.5 | 2.7 | 3.2 | 4.17 | 5.18 | 2+9 | 6.20 | 7.17 | 8.22 | 9.27 | |

| B.6 | 2.8 | 3.3 | 4.18 | 5.19 | 3+4 | 6.21 | 7.18 | 8.23 | 9.28 | |

| B.1 | 2.9 | 3.4 | 4.19 | 5.20 | 3+5 | 6.22 | 7.19 | 8.24 | 9.29 | |

| B.2 | 2.10 | 3.5 | 4.20 | 5.21 | 3+6 | 6.23 | 7.20 | 8.25 | 9.30 | |

| B.3 | 2.1 | 3.6 | 4.21 | 5.22 | 3+7 | 6.24 | 7.21 | 8.26 | 9.31 | |

| B.4 | 2.2 | 3.7 | 4.22 | 5.23 | 3+8 | 6.25 | 7.22 | 8.28 | 9.32 | |

| B.5 | 2.3 | 3.8 | 4.23 | 5.24 | 4+5 | 6.26 | 7.23 | 8.29 | 9.33 | |

| B.6 | 2.4 | 3.9 | 4.24 | 5.25 | 4+6 | 6.27 | 7.24 | 8.30 | 9.34 | |

| B.1 | 2.5 | 3.10 | 4.25 | 5.26 | 4+7 | 6.28 | 7.25 | 8.31 | 9.35 | |

| B.2 | 2.6 | 3.11 | 4.26 | 5.1 | 4+8 | 6.29 | 7.26 | 8.32 | 9.36 | |

| B.3 | 2.7 | 3.12 | 4.27 | 5.2 | 5+6 | 6.30 | 7.27 | 8.33 | 9.37 | |

| B.4 | 2.8 | 3.13 | 4.28 | 5.3 | 5+7 | 6.31 | 7.28 | 8.34 | 9.38 | |

| B.5 | 2.9 | 3.14 | 4.29 | 5.4 | 6+7 | 6.32 | 7.29 | 8.35 | 9.39 | |

| B.6 | 2.10 | 3.15 | 4.30 | 5.5 | 6+8 | 6.33 | 7.30 | 8.36 | 9.40 |

Курсове проектування

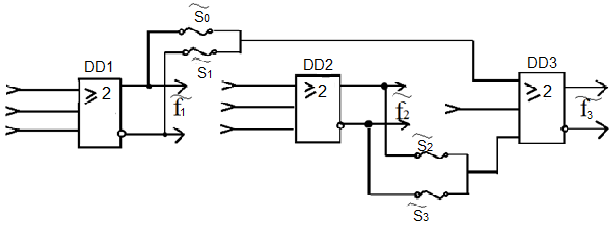

Наносхема складається з трьох універсальних мажоритарних елементів (УМЕ) DD1,DD2 та DD3, трьох програмуючих провідників з вхідними параметрами  ,

,  та

та  , чотирьох програмуючих ключів у вигляді плавких перемичок з’єднання/роз’єднання

, чотирьох програмуючих ключів у вигляді плавких перемичок з’єднання/роз’єднання  ,

,  та

та  і реалізує три функції

і реалізує три функції  та

та  чотирьох вхідних аргументів

чотирьох вхідних аргументів

. Знаком

. Знаком  позначені елементи програмування.

позначені елементи програмування.

1. Для реалізації визначених за варіантом таблиці 1 логічних функцій  та

та  запрограмувати величини параметрів

запрограмувати величини параметрів  ,

,  та

та  і під’єднати відповідні їм провідники до програмуючих (нижніх) входів УМЕ, а також з’єднати чи роз’єднати програмуючі провідники

і під’єднати відповідні їм провідники до програмуючих (нижніх) входів УМЕ, а також з’єднати чи роз’єднати програмуючі провідники  ,

,  та

та

2. З’єднати попарно провідники аргументів  ,

,  з двома інформаційними (верхніми) входами УМЕ DD1 та DD2.

з двома інформаційними (верхніми) входами УМЕ DD1 та DD2.

3. Описати принцип дії синтезованої наносхеми.

4. Записати в мажоритарному базисі рівняння для усіх трьох логічних функцій і скласти їх таблиці істинності.

5. Створити відповідну наносхему на базі квантових коміркових автоматів (КА) на проектному планшеті системи автоматизованого проектування (САПР) QCA Designer.

6. Реалізувати комп’ютерне моделювання наносхеми і перевірити повну таблицю істинності за отриманими діаграмами вихідних логічних функцій.

7. Розрахувати на САПР загальну кількість КА, їх розміри та відстані між їх центрами, діаметри квантових острівців і загальні розміри наносхеми.

8. Зробити висновки.

Таблиця 1.

Реалізіція функцій наносхеми на КА

| № | f1 | f2 | f3 |

|

|

| |

|

|

| |

|

|

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|

| |

|

|

| |

|

|  ) )

| |

|

| (

| |

|

|  ) )

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|  ) )

| |

|

|  ) )

| |

|

|

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|

| |

|

|

| |

|

|  ) )

| |

|

|

| |

|

|  ) )

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|  ) )

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|  ) )

| |

|

|

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|  ) )

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

| |

|

|

|

Дата добавления: 2016-11-02; просмотров: 693;