Квантові елементи пам'яті

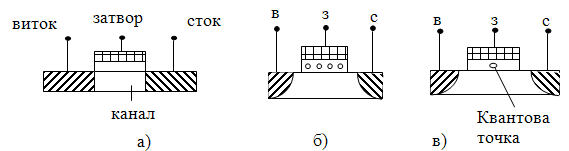

На рис 7.1 показано ряд запам'ятовуючих приладів, в яких використовують квантові точки.

Рис.7.1. Ряд квантових приладів

Ці прилади схожі на звичайні МОН-транзистори (а). Шар під затвором є нанокристалічна плівка полікремнію. Сформовані при високій температурі нанокристали працюють як надмалі області провідності, де накопичуються електрони (рис.7.1, б, в) і створюють навкруги цієї області кулонівський бар'єр. Таким чином, через зарядовий стан квантових точок вдається керувати вмиканням або вимиканням приладів. Ці квантові прилади використовують у статичних запам'ятовуючих пристроях (СЗП).

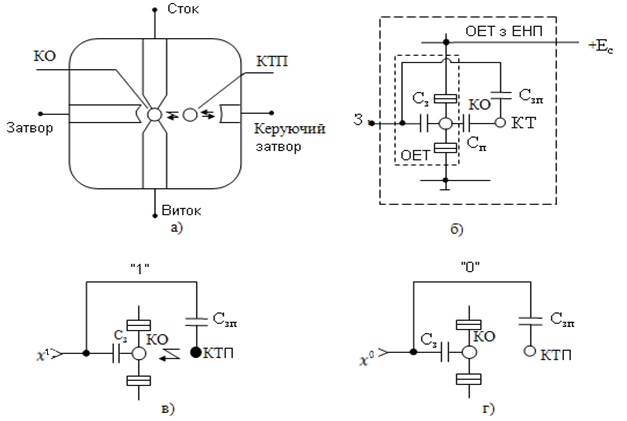

Наступний квантовий елемент пам'яті виготовляють у нанометровому шарі кремнію-на-ізоляторі (КНІ). Ізолятором може бути двоокис кремнію або сапфір. Ця структура являє собою одноелектронний транзистор (ОЕТ) з електродами витока, стока та двох затворів (рис.7.2, а).

Рис.7.2. Одноелектронний транзистор (ОЕТ) з енергонезалежною пам'яттю (ЕНП) на квантовій точці пам'яті (КТП) (а), його електрична схема (б), стани КТП після запису логічної одиниці (заповнений) х1 (в) і логічного нуля при відсутності запису (порожній) х0 (г)

Ефект пам'яті полягає у процесі зарядки-розрядки спеціально створеної квантової точки КТП після прикладання напруг запису або лічіння (рахування) на керуючий затвор. При цьому змінюється потенціал центрального острівця КО і, вочевидь, струм через нього . Запис-лічіння можливі при температурі Т ≤ 4,2 К. На рис.7.2, б наведена електрична схема ОЕТ з енергонезалежною пам'яттю. На ній для спрощення показаний тільки один затвор транзистора. Режим зберігання з ЕНП бінарної інформації ілюструють рис.7.2, в, г.

Вже створені наносхеми на ОЕТ з ЕНП об'ємом пам'яті від 4 до 256 Гбіт.

7.2. Програмовані логічні наносхеми

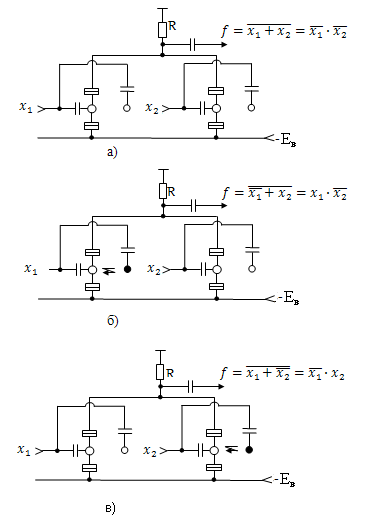

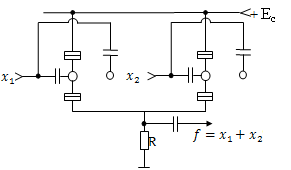

На елементарній базі ОЕТ з ЕНП реалізований ряд наносхем, що здійснюють різні логічні функції. Наприклад, на рис. 7.3 показані варіанти програмування наносхем логічного додавання із запереченням 2АБО-НІ.

Рис.7.3. Чотири варіанти програмування логічного елемента 2АБО-НІ на ОЕТ з ЕНП

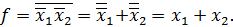

Технічна реалізація схеми має універсальну структуру матриці 2АБО-НІ:

(7.1)

(7.1)

та програмну структуру ЕНП. Цей варіант налаштування на практиці реалізують в програмованих логічних матрицях (ПЛМ).

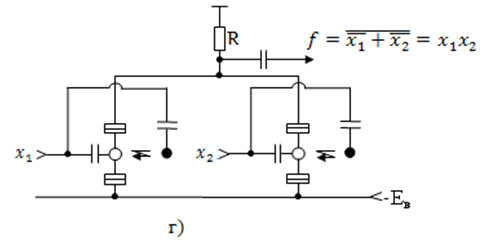

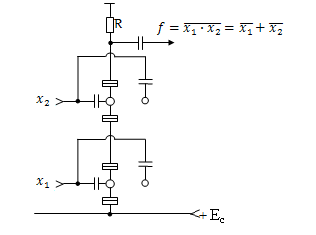

Для створення програмованої матриці 2АБО слід в наносхемі 2АБО-НІ (рис.7.3) резистор навантаження  включають до витоків ОЕТ, як зображено на рис.7.4.

включають до витоків ОЕТ, як зображено на рис.7.4.

Рис.7.4. Наносхема програмованого логічного елемента 2АБО

Для реалізації елемента логічного множення із запереченням 2І-НІ використовують послідовне з'єднання двох ОЕТ, як показано на рис. 7.5.

Рис.7.5. Нанохема програмованого логічного елемента 2І-НІ

Для програмування цього елемента записують відповідні чотири керуючих стани на квантові точки пам'яті КТП. Отримують з умовами подвійності програмоване виконання наступних функцій:

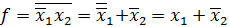

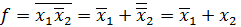

, (7.2)

, (7.2)

, (7.3)

, (7.3)

(7.4)

(7.4)

Отже, використання ПЛМ розширює номенклатуру задач обробки цифрової інформації.

Дата добавления: 2016-11-02; просмотров: 532;