Комплиментарная МДП логика

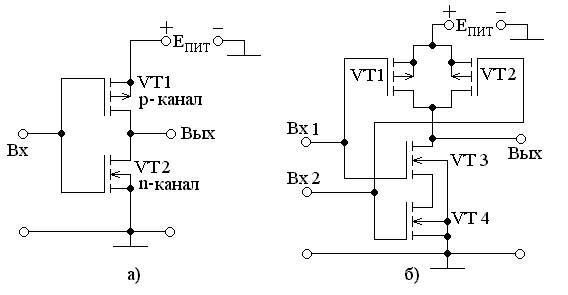

Комплиментарная МДП (КМДП) логика включает в себя пары p- и n-канальных полевых транзисторов с индуцированным каналом. Простейшая схема, выполняющая операцию НЕ представлена на рисунке 3 а.

Рис. 3. Логические элементы на КМДП.

Принцип её работы поясним с помощью таблицы 2.

Таблица 2.

| Вх | UВХ, В | VT1 | VT2 | IС | UВЫХ, В | Вых |

| Откр | Закр | |||||

| Закр | Откр |

Предположим, что напряжение питания равно ЕПИТ=10 В. Как будет показано ниже напряжение U0=0 В, а U1=10 В. Пороговое напряжение, подаваемое на затвор, у таких транзисторов составляет примерно UЗИ ПОРОГ » 4 В. Тогда при подаче на вход напряжения логического ²0² (первая строчка таблицы) транзистор VT2 будет закрыт, а транзистор VT1 будет открыт. Так как напряжение между его затвором и истоком, который соединен с подложкой, равно UЗИ = - 10 В, а пороговое напряжение для р-канального транзистора составляет UЗИ ПОРОГ »-4 В. Поскольку транзистор VT2 закрыт, ток стока IС=0. Напряжение на выходе составит UВЫХ= 10 В и, следовательно, это соответствует логической ²1².

При подаче на вход логической ²1² U1=10 В (вторая строчка таблицы) транзистор VT1 будет закрыт, поскольку напряжение между его затвором и истоком составляет UЗИ=0 В, а транзистор VT2 будет открыт. Так как транзистор VT1 закрыт, ток стока так же будет равен IС=0. Напряжение на выходе составит UВЫХ= 0 В и, следовательно, это соответствует логическому ²0². Таким образом, в статическом состоянии ток через схему отсутствует за исключением тока утечки, который составляет единицы мкА.

Рассмотрим схему, приведенную на рисунке 4 б. Принцип её работы также поясним с помощью таблицы 3.

Таблица 3.

| Вх 1 | Вх 2 | UВХ 1, В | UВХ 2, В | VT1 | VT2 | VT3 | VT4 | I | UВЫХ, В | Вых |

| Откр | Откр | Закр | Закр | |||||||

| Закр | Откр | Откр | Закр | |||||||

| Откр | Закр | Закр | Откр | |||||||

| Закр | Закр | Откр | Откр |

При подаче на оба входа логического ²0², как было рассмотрено выше транзисторы VT1 и VT2 открыты, а транзисторы VT3 и VT4 закрыты. На выходе будет высокий потенциал и ток через схему отсутствует.

При подаче на вход хотя бы одной логической ²1² один из транзисторов VT3 или VT4 открывается, а один из транзисторов VT1 или VT2 закрывается. Поскольку один из транзисторов закрыт VT3 или VT4, то ток через схему отсутствует, а на выходе будет высокий потенциал, т.е. логическая ²1² (вторая и третья строка таблицы).

При подаче на оба входа логических ²1² оба транзистора VT3 и VT4 открыты, а транзисторы VT1 и VT2 закрыты. На выходе будет логический ²0² и ток через транзисторы по-прежнему отсутствует (четвертая строчка таблицы). Таким образом, данная схема выполняет операцию И-НЕ. В статическом режиме она не потребляет тока.

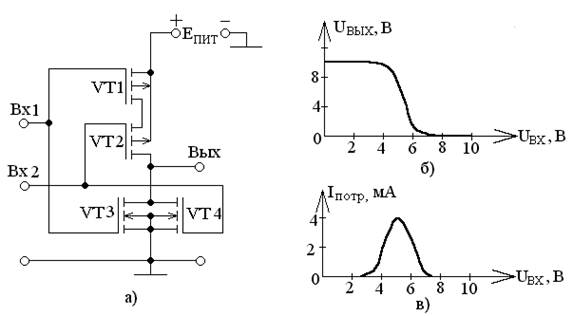

Схема ИЛИ-НЕ представлена на рисунке 4а, а её принцип работы поясним с помощью таблицы 4.

Таблица 4.

| Вх 1 | Вх 2 | UВХ 1, В | UВХ 2, В | VT1 | VT2 | VT3 | VT4 | I | UВЫХ, В | Вых |

| Откр | Откр | Закр | Закр | |||||||

| Закр | Откр | Откр | Закр | |||||||

| Откр | Закр | Закр | Откр | |||||||

| Закр | Закр | Откр | Откр |

В этом случае, в отличие от предыдущего, при подаче на один из входов логической ²1²(вторая и третья строчки таблицы) на выходе будет логический ²0², так как один из транзисторов VT1 и VT2 закрыт, а один из транзисторов VT3 или VT4 открыт, т.е. на выходе будет нулевой потенциал.

Рис. 4. Логический элемент 2ИЛИ-НЕ на КМДП,

Дата добавления: 2016-09-20; просмотров: 915;