Цифровые сумматоры и компараторы

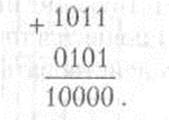

Основная арифметическая операция, выполняемая над двоичными числами в цифровых измерительно-вычислительных устройствах (и, конечно, во всех ЭВМ), — операция сложения (к которой сводятся, как известно, и вычитание, и умножение, и деление). Особенностью сложения многоразрядных двоичных чисел является то, что только в младшем разряде складываются два числа, во всех остальных три числа: два основных и перенос из предыдущего разряда. Это хорошо видно из сложения двух четырехразрядных чисел:

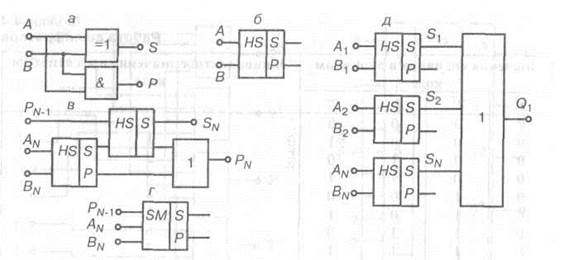

Рис. 4.27. Функциональная схема полусумматора (а) и его условное изображение (б); схема сумматора (в) и его условное изображение (г); схема цифрового компаратора (д)

Числа младшего разряда складываются с помощью полусумматора (рис. 4.27, а), состоящего из логических элементов «Исключающее ИЛИ» и «И».

Если на вход схемы «Исключающее ИЛИ» подаются сигналы Аи В, отличные друг от друга, то на выходе имеется их сумма S=1. Если А = В = 0 или A=В=1, тоS=0. При этом срабатывает схема «И», на выходе которой при А = В = 0 перенос Р = 0, а при А = В = 1 перенос Р = 1. Условное изображение полусумматора HS приведено на рис. 4.27, б.

Схема полного двоичного сумматора и его условное изображение приведены соответственно на рис. 4.27, е и на рис. 4.27, г. На входы сумматора подаются не только слагаемые N-гo разряда, но и перенос из предыдущего N-1 разряда.

Многоразрядные сумматоры собираются на основе рассмотренных схем. При этом возможно включение как с последовательным переносом, так и с параллельным, ускоренным.

Рассмотренные функциональные узлы выпускаются в России в виде интегральных микросхем, маркируемых стандартным семиэлементным кодом, в котором третий элемент — две буквы обозначают: ИЛ — полусумматоры; ИМ — сумматоры

Дата добавления: 2016-04-02; просмотров: 1841;