Суммирование двоичных чисел с учетом переноса из младшего разряда. Описание процесса, реализация на базовых логических элементах.

Схемы арифметического суммирования

Пусть требуется сложить два одноразрядных числа. Составим таблицу истинности:

| a | B | S | P |

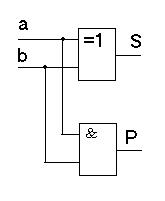

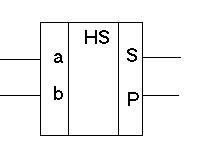

Рисунок - Принципиальная схема и условное обозначение полусумматора

Полусумматор позволяет осуществлять сложение двух одноразрядных чисел, формируя при этом сумму S этого разряда и перенос P в следующий. При сложении многоразрядных чисел в каждом текущем разряде необходимо осуществить операцию сложения трех величин. А, В а так же перенос из предыдущего разряда .

ai+bi=Pis+Si

Si+Pi=P(i+1)SSiP

PiS+P(i+1)S=PSP

| ai | bi | Pi | Si | Pis | Sip | P(i+1)s | Psp |

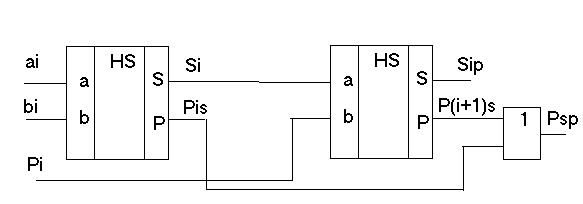

Рисунок - Схема суммирования

Операция сложения в полном одноразрядном сумматоре разбивается на три этапа: первоначально складываются значения a и b, формируя при этом первую частную сумму Si и первый частный перенос Рis. На втором этапе к частной сумме Si добавляется перенос из предыдущего разряда Pi. В результате в текущем разряде формируется сумма с учетом переноса Sip и второй частный перенос P(i+1)s. Для формирования переноса в следующий разряд Psp необходимо сложить оба частных переноса Pis и P(i+1)s. Однако, учитывая тот факт, что эти частные переносы не могут быть равными единице одновременно, для их арифметического сложения достаточно использовать элемент «ИЛИ». (элементы «ИЛИ» и «Исключающее ИЛИ» отличаются лишь последней строкой таблицы истинности)

Сложение многоразрядных чисел

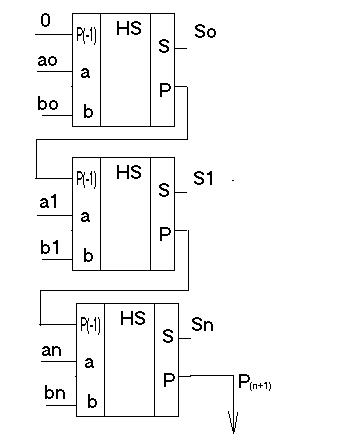

Рисунок – Схеме сложения многоразрядных чисел

Схема позволяет достаточно просто производить суммирование двух чисел произвольных разрядов. Однако, сумма и перенос в более старших разрядах формируется по последовательной схеме. Сначала формируется перенос в более младшем, затем сумма и перенос в более старшем разряде. Таким образом, формирование значений сумм и переносов в каждом разряде сопряжено с задержкой, кратность которой равна числу складываемых разрядов.

Существуют так называемые схемы ускоренного переноса, строящиеся по параллельной схеме и позволяющие формировать перенос в каждом разряде за один такт. Однако, схемы достаточно громоздки и сложность схемы напрямую зависит от разрядности складываемых чисел.

12. Дешифраторы: таблица переключений и реализация дешифратора 2Х4 на элементах И-НЕ. Дешифраторы-демультиплексоры.

Дешифратор (полный, линейный) – устройство, однозначно отображающее поступающий на его вход двоичный код появлением информационного уровня на одном из его выходов, при этом для полного дешифратора характерно при n входах – 2n выходов.

| a | b | y1 | y2 | y3 | y4 |

a y4

|

y3

b y2

0 y1

0 y1

a

1 y2

информационный уровень «1»

информационный уровень «1»

2 y3

b

3 y4

Часто некоторые информационные входные сигналы могут иметь активный управляющий уровень «0», при этом на схеме данный сигнал также снабжают значком инверсии.

Дешифраторы могут быть неполными, например BIN DEC, имеющий 4 входа, 10 выходов. Наличие информационного уровня на одном из выходов вызывает зажигание одного из 10 катодов, выполненного в виде арабской цифры. Для неполных дешифраторов подача двоичного кода, отображающего цифру >9 не допускается.

Дешифраторы могут быть неполными, например BIN DEC, имеющий 4 входа, 10 выходов. Наличие информационного уровня на одном из выходов вызывает зажигание одного из 10 катодов, выполненного в виде арабской цифры. Для неполных дешифраторов подача двоичного кода, отображающего цифру >9 не допускается.

Семисегментный дешифратор.

- позволяет отображать поступающий на вход двоичный вход в виде цифры, формируемой из семи сегментов для BIN-DEC дешифратора, либо дополнительно 6 букв для полного дешифратора.

|

| |||||||||

|  | ||||||||

|  |

f b 0-a,b,c,d,e,f 1-b,c

f b 0-a,b,c,d,e,f 1-b,c

g ………….

g ………….

A-a,b,c,e,f,g B-c,d,e,f,g

A-a,b,c,e,f,g B-c,d,e,f,g

e c F-a,e,f,g

e c F-a,e,f,g

d

d

| |||||

| |||||

| |||||

| x1 | x2 | x3 | x4 | a | b | c | d | e | f | g |

| . | . | . | . | . | . | . | . | . | . | . |

Цифры 1,2,4,8 в поле входных сигналов подчеркивают тот факт, что, мы имеем дело с натуральным двоичным кодом. Символ H служит для отображения децимальной точки, дополнительно отображая разряд формируемого числа. Для управления ЖК-индикаторами форма сигнала, подаваемого на каждый сегмент должна быть знакопеременной, в противном случае происходит разрушение индикатора. Во избежания разрушения необходимо изменить информационный уровень на противоположный с частотой ~100 Гц. Одновременно с этим меняется на обратный информационный уровень сигнала, подаваемый на подложку ЖК-индикатора.

Если I=0 – инвертор

Если I=0 – инвертор

I=1 – повторитель

Таким образом, сигнал I подается на общий провод ЖК-индикатора при условии, что форма этого сигнала будет меандр, формирующий знакопеременное напряжение с постоянной составляющей равной нулю.

Объединив все информационные входы x в один, а также убрав выходной объединяющий дизъюнктор получим устройство коммутирующее один входной информационный сигнал на несколько выходов под действием сигналов управления. Такое устройство называют демультиплексор, которое в частном случае при x=1 превращается в обычный дешифратор (дешифратор – мультиплексор). V – информационный вход.

Дата добавления: 2016-02-16; просмотров: 1770;