Тема 8 Микропроцессоры и микропроцессорные систем

Структура микропроцессорной системы

Микропроцессором (МП) называется построенное на одной или нескольких БИС/СБИС программно-управляемое устройство, осуществляющее процесс обработки информации и управление им.

Решаемая задача определяется реализуемой МП программой, структура микропроцессорной системы остается неизменной, что и определяет его универсальность.

Микропроцессоры появились, когда уровень интеграции ИС достиг значений, когда необходимые для программной реализации алгоритмов блоки удалось разместить на одном или нескольких кристаллах. МП – центральный процессорный элемент микропроцессорной системы (микро-ЭВМ), в которую также входят память и устройства ввода/вывода (внешние устройства).

Совокупность БИС/СБИС, пригодных для совместного применения в составе микро-ЭВМ, называется микропроцессорным комплектом БИС/СБИС (МПК). Понятие МПК задает номенклатуру микросхем с точки зрения возможностей их совместного применения (совместимость по архитектуре, электрическим параметрам, конструктивным признакам и пр.). В состав МПК могут входить микросхемы различных серий и схемотехнических типов при условии их совместимости.

В микропроцессорной системе (МПС) организуется процесс выполнения заданной программы, и самые различные задачи решаются путем выполнения последовательности команд, свойственных данному МП. Вычислительные, контрольно-измерительные или управляющие системы, обрабатывающим элементом которых служит МП, относятся к числу МПС.

Практически всегда структура МПС является магистрально-модульной. В такой структуре всегда имеется группа магистралей (шин), к которым подключаются различные модули (блоки), обменивающиеся между собой информацией поочередно, в режиме разделения времени.

Термин «шины» относится к совокупности цепей (линий), число которых определяется разрядностью шины.

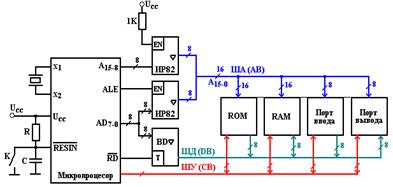

Типична трехшинная структура МПС с шинами адресов ША (английский термин Adress Bus – AB), данных ШД (Data Bus – DB) и управления ШУ (Control Bus – CB).

На рис. 40 показана структура микропроцессорной системы с МП (К1821ВМ85А), имеющим мультиплексированную шину адресов/данных.

Линии А15-8 являются адресными, через них в систему подается старший байт 16-разрядного адреса. В эту шину включен формирователь на постоянно открытом по входу разрешения EN буферном регистре ИР82, обеспечивающем работу шины на нагрузку, образуемую внешними цепями. Собственной нагрузочной способности у выводов МП, как правило, не хватает. Линии AD7-0 мультиплексируются. Вначале они передают младший байт адреса, признаком чего служит наличие сигнала ALE (Adress Latch Enable), загружающего этот байт в регистр ИР82.

Рисунок 40

После загрузки регистра сигнал ALE снимается, и содержимое регистра остается неизменным вплоть до новой загрузки в следующем цикле работы процессора. Так формируется 16-разрядная шина адреса, содержащая адрес А15-0. Этот адрес используется блоками постоянной и оперативной памяти ROM и RAM. Адресация портов ввода и вывода данных требует восьмиразрядного адреса, что соответствует возможности работы не более чем с 256 портами каждого из типов. Адрес портов можно снимать с любой половины адресной шины.

После передачи младшего байта адреса шина AD7-0 отдается для передачи данных. Эти передачи двунаправлены, направление задается буфером данных BD в зависимости от сигнала Т (Transit). При активном состоянии сигнала чтения RD (Read) данные передаются справа налево, при пассивном – в обратном направлении. К шине данных подключены информационные выводы всех модулей МПС.

Выводы х1 и х2 служат для подключения кварцевого резонатора или иных контуров, задающих частоту тактовому генератору, расположенному в МП. Тактирование системы производится на частоте, раной половине частоты резонанса кварца или иного контура, поскольку генератор работает на триггер, с которого снимаются сигналы тактирования модулей МПС, а триггер делит частоту на 2. Вход  является входом асинхронного сброса, приводящим МП в исходное состояние. Сигнал L – активный. Сброс может быть осуществлен замыканием ключа К и автоматически происходить при включении питания Ucc. В этом случае благодаря цепочке RC напряжение на входе

является входом асинхронного сброса, приводящим МП в исходное состояние. Сигнал L – активный. Сброс может быть осуществлен замыканием ключа К и автоматически происходить при включении питания Ucc. В этом случае благодаря цепочке RC напряжение на входе  нарастает постепенно, и в течение некоторого времени после включения питания остается низким (ниже порогового), что равноценно подаче сигнала

нарастает постепенно, и в течение некоторого времени после включения питания остается низким (ниже порогового), что равноценно подаче сигнала  .

.

Выполняя программу, МП обрабатывает команду за командой. Команда задает выполняемую операцию и содержит сведения об участвующих в ней операндах. после приема команды происходит ее расшифровка и выполнение, в ходе которого МП получает необходимые данные из памяти или внешних устройств. Ячейки памяти и внешние устройства (порты) имеют номера, называемые адресами, которыми они обозначаются в программе.

По однонаправленной адресной шине МП посылает адреса, определяя объект, с которым будет обмен, по шине данных (двунаправленной) обменивается данными с модулями (блоками) системы, по шине управления идет обмен управляющей информацией.

Устройства ввода-вывода (УВВ) или внешние устройства (ВУ) – технические средства для передачи данных извне в МП или память, либо из МП или памяти во внешнюю среду. Для подключения ВУ необходимо привести сигналы, форматы слов, скорость передачи и т.д. к стандартному виду, принимаемому данным МП. Это выполняется специальными блоками, называемыми адаптерами (интерфейсными блоками ввода-вывода). Интерфейсом называется совокупность аппаратных и программных средств, унифицирующих процессы обмена между модулями системы.

Кроме блоков, обозначенных на рисунке 40, в состав систем входят обычно и более сложные, чем адаптеры, блоки управления внешними устройствами – контроллеры. К их числу относятся, прежде всего, контроллеры прерываний и прямого доступа к памяти. Имеются также контролеры клавиатуры, дисплея, дисковой памяти и пр.

Контроллеры прерываний обеспечивают обмен с внешними устройствами в режиме прерывания (временной остановки) выполняемой программы для обслуживания запроса от внешнего устройства.

Контроллеры прямого доступа к памяти обслуживают режим прямой связи между внешними устройствами и памятью без участия МП. При управлении обменом со стороны МП пересылка данных между внешними устройствами и памятью происходит в два этапа – сначала данные принимаются микропроцессором, а затем выдаются им на приемник данных. В режиме прямого доступа к памяти МП отключается от шин системы и передает управление или контроллеру прямого доступа, а передачи данных осуществляются в один этап – непосредственно от источника к приемнику.

В состав МПС часто входят также программируемые таймеры, формирующие различные сигналы (интервалы, последовательности импульсов и т.д.) для проведения операций, связанных со временем.

С учетом сказанного выше обобщенная структура микропроцессорных систем может быть представленная в виде, приведенном на рис. 41.

Устройство управления (УУ), входящее в состав МП, представляет собой последовательностное устройство, реализованное на логических элементах (аппаратная реализация) или на базе ПЗУ (микропрограммная реализация). В качестве операционного устройства (ОУ) в МП обычно используется АЛУ со сдвигателем. В состав МП часто включается регистровое ЗУ (РЗУ) для хранения промежуточных результатов.

Через ИУ к системе подключаются внешние устройства. При обмене информацией то или иное ИУ (внешнее устройство) адресуется МП по шине DB (AD). При этом также формируются сигналы управления на шине СВ, определяющие режим обмена.

В МПС часто включается программируемый таймер (ПТМ), который через определенные промежутки времени вырабатывает управляющие сигналы, включающие или выключающие системы или отдельные устройства, либо изменяющие режимы их работы. Дополнительные устройства – контроллеры прерываний и прямого доступа к памяти – обеспечивают соответствующие режимы работы МПС.

Рисунок 41

Основная литература: [2, 5, 6];

Дополнительная литература: [7, 8].

Дата добавления: 2016-02-16; просмотров: 1063;