Принципы построения вычислительных устройств

Любое вычислительное устройство принципиально должно включать три самостоятельных блока. Это процессор, предназначенный для обработки информации, блок памяти, для хранения алгоритма работы и исходных данных, и устройства ввода-вывода, обеспечивающего обмен информацией между вычислительным устройством и внешним миром. Порядок взаимодействия между этими блоками определяется внутренней структурой вычислительного устройства. Все существующие в настоящий момент структуры вычислительных устройств эксплуатируют предложенные еще в середине 20 века модели. Это, так называемые, архитектура Фон Неймана (пристанская) и Гарвардская архитектура. Рассмотрим их отличия и предпочтительные области применения.

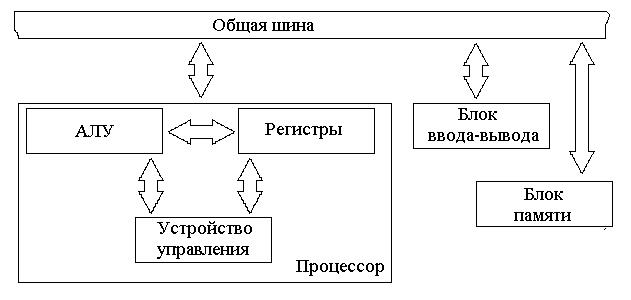

Основными принципами, заложенными группой разработчиков под руководством фон Неймана является хранения команд и данных в едином блоке памяти, последовательность выполнения инструкций и использование для вычислений двоичной системы счисления. На рис.10.9 приведена упрощенная структура вычислительного устройства, реализующая принципы фон Неймана.

Цикл работы устройства заключается в следующем. Сначала процессор выставляет на общую шину порядковый номер выполняемой команды. Используя этот номер в качестве адреса, из блока памяти считывается код команды, которая и выполняется процессором. После выполнения этой команды процессор выставляет номер следующей операции, и цикл работы повторяется. Важно отметить, что как сама команда, так и данные передаются через одну общую шину, что и предполагает пошаговость выполнения алгоритма. Этот процесс остается неизменным, отсюда и название устройство обработки – процессор.

К достоинствам данной структуры следует отнести простоту ее технической реализации, возможность оперативного распределения памяти между командами и данными, а так же возможность оперативного изменения алгоритма работы, то есть порядок и суть выполняемых операция можно изменять по результатам ранее проделанных вычислений.

|

Рис.10.9 Структура вычислителя фон Неймана.

К недостаткам рассмотренной структуры можно отнести невысокую скорость работы (все действия выполняются строго последовательно) и возможность ошибок, обусловленных как собственными сбоями, так и внешним воздействием (вирусные атаки), так как существует доступ извне как к данным, так и самой программе.

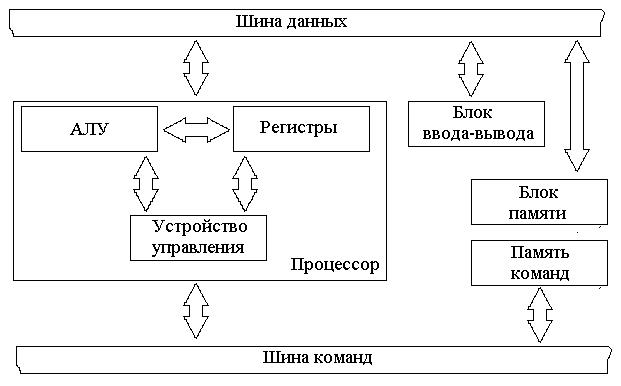

Устранить эти недостатки позволяет, так называемая гарвардская архитектура вычислительного устройства. Ее коренное отличие от рассмотренной состоит в разделении блока памяти на память команд и данных и использовании двух внутренних шин передачи информации (шины команд и шины данных). Упрощенная структура такого решения приведена на рис. 10.10.

|

Рис.10.10. Гарвардская структура вычислителя.

Данная структура, во-первых, предполагает параллельность в работе с командами и данными, что позволяет повысить быстродействие, и, во-вторых, отсутствие связи памяти команд с устройством ввода-вывода, что принципиально исключает возможность повреждения алгоритма работы при внешнем вмешательстве (вирусная атака). Однако техническая реализация гарвардской архитектуры сложнее фон Неймановской. К тому же она не обладает достаточной гибкостью, так как объем памяти команд строго ограничен аппаратными ресурсами, в то время как в архитектуре фон Неймана объем используемый для записи алгоритма работы памяти может оперативно (в том числе и в процессе работы) меняться.

Перечисленные особенности определяют область применения гарвардской архитектуры. Это микроконтроллеры и сигнальные процессоры с повышенными требованиями к надежности функционирования. В сигнальных процессорах (процессоров для обработки сигнала в режиме реального времени) для повышения быстродействия часто используют трехшинную архитектуру, что позволяет одновременно выполнять операцию чтения двух операндов и запись результата вычисления.

Микроконтроллеры

Микроконтроллером называют интегральную схему, предназначенную для управления различными устройствами. С этой целью микроконтроллер кроме рассмотренных выше средств, предназначенных для обработки информации, включает ряд периферийных (исполнительных) устройств. К таким устройствам, например, могут относиться аналого-цифровые и цифро-аналоговые преобразователи, широтно-импульсные модуляторы, таймеры, порты ввода-вывода, реализующие различные интерфейсы обмена информацией, контроллеры управления бесконтактными двигателями, дисплеями, клавиатурой и т.д. Таким образом, микроконтроллер, без использования дополнительных средств, позволяет построить схемы управления различными процессами и объектами.

Производительность вычислительных средств микроконтроллеров значительно уступает аналогичному параметру процессоров, предназначенных для профессионального применения. Однако существует большое число, практических задач, для решения которых применение микроконтроллеров вполне оправдано. Это, например, бытовая техника (телефоны, телевизоры и т.д.), автомобили, промышленные роботы и т.д.

Микроконтроллеры принять классифицировать по разрядности используемого АЛУ. Первые из разработанных микроконтроллеров были четырехразрядными. Сейчас существую 8, 16, 32 и 64 разрядные микроконтроллеры. Причем большую долю из них составляют 8 разрядные устройства.

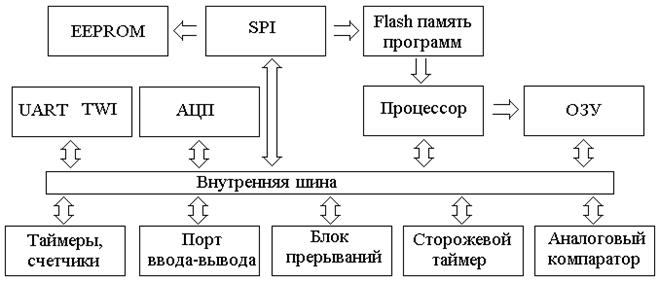

На рис.10.11. приведена упрощенная структура AVR микроконтроллера. В нем реализована гарвардская архитектура и кроме процессора, ОЗУ, портов ввода-вывода и памяти программ (Flash) входит энергонезависимая память EERPOM, последовательные интерфейсы SPI (последовательный периферийный интерфейс), UART (универсальный асинхронный приемопередатчик) и TWI (двухпроводный интерфейс) и целый ряд периферийных устройств, таких как АЦП, таймеры, счетчики, блок прерываний сторожевой таймер и аналоговый компаратор. Данный микроконтроллер разработан фирмой Atmel в 1996 году и имеет много модификаций, в том числе специализированных для работы с LCD индикаторам, радиоприемопередатчиками, электродвигателями, осветительной техникой и т.д.

|

Рис.10.11. Структура AVR микроконтроллера

Дата добавления: 2016-03-10; просмотров: 1068;