Лекция №9. Программируемый параллельный интерфейс

Содержание лекции:схема включения программируемого параллельного интерфейса в микропроцессорную систему, его адресация, коды выбора одного из портов, порядок выполнения инструкций IN и OUT, режимы работы.

Цели лекции:изучить назначение входов и выходов программируемого параллельного интерфейса, способы его инициализации, режимы работы.

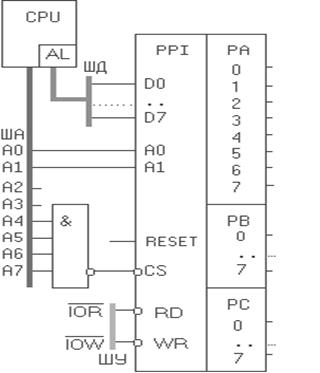

На рисунке 25 приведены условное обозначение программируемого параллельного интерфейса (ППИ или PPI-Programmable Peripheral Interface) и одна из возможных схем его включения в микропроцессорную систему. ППИ имеет три двунаправленных 8-ми битных канала связи с внешними устройствами, называемых обычно портами - PA,PB,PC.

Рисунок 25 – Схема включения ППИ в микропроцессорную систему

Порт PC отличается от остальных тем, что его можно "расчленить" на два независимых 4-х битных порта: старшую половину D7..D4 и младшую D3..D0. Как видно из рисунка 25, ППИ подключается к шине данных с помощью двунаправленных тристабильных выводов D7..D0. Входы A1,A0 осуществляют выбор одного из четырех каналов обмена данными: трех портов PA,PB,PC или внутреннего регистра управления/состояния (РУС или CSR - Control and Status Register).

Т а б л и ц а 6

A1 A1

| A0 | КАНАЛ |

| PA | ||

| PB | ||

| PC | ||

| CSR |

ППИ переводится в рабочее состояние активным значением сигнала на инверсном входе "выбор микросхемы" (Chip Select, Crystall Select, CS) ~CS = 0, снимаемым с выхода дешифратора адреса (на рисунке 25 приведен неполный дешифратор - элемент И-НЕ). Логический ноль на выходе элемента И-НЕ появится, если все сигналы на его входах равны "1" (A7=A6=A5=A4=1). Так как выбор того или иного канала производится с помощью входов A1,A0, подключенных к аналогичным линиям шины адреса (ША), то с учетом входов дешифратора возможны следующие комбинации сигналов на ША, представленные в таблице 7.

Т а б л и ц а 7

| ЛИНИИ ШИНЫ АДРЕСА | КАНАЛ/ ПОРТ | АДРЕС (HEX) | |||||||

A7 A7

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | ||

| x | x | PA | F0 | ||||||

| x | x | PB | F1 | ||||||

| x | x | PC | F2 | ||||||

| x | x | CSR | F3 |

Линии A3,A2 шины адреса в схеме не задействованы, поэтому их значения в таблице обозначены (x - Don't Care Bits). При вычислении 16-ного адреса программист в качестве значения этих бит может подставлять любые значения, в том числе нули, как это и сделано в таблице. Например, для порта PB двоичный код 1111xx01 = 11110001(BIN) = F1(HEX).

Обмен байтами данных между МП (CPU) и внешними устройствами (ВУ), подключенными к портам ППИ, может производиться по командам ассемблера IN А, Адрес порта или OUT Адрес порта, А.

Выполнение команд IN и OUT производится в два этапа (без учета тактов и циклов, зависящих от конкретной архитектуры микропроцессора). Например, рассмотрим выполнение инструкций IN A,0F1h и OUT 0F1h,A, где A – аккумулятор, F1 – адрес порта PB.

1 этап. Микропроцессор помещает адрес (например F1) на ША, где он дешифрируется (в нашем примере элемент И-НЕ). С выхода дешифратора активный уровень (0) поступает на инверсный вход ~CS и переводит ППИ в рабочее состояние.

2 этап..

а) команда OUT. В следующий момент времени МП помещает байт, находящийся в аккумуляторе на шину данных и одновременно вырабатывает строб записи ~IOW поступающий на вход управления записью ~WR. Импульс ~IOW защелкивает байт данных в выходном регистре соответствующего порта ( в нашем примере в порте PB);

б) команда IN. Микропроцессор посылает на вход управления чтением ~RD строб чтения ~IOR , которым считывается в аккумулятор по ШД байт данных из порта PB.

ППИ имеет три основных режима работы:

0 – простой ввод-вывод (для передачи информации работают все порты РА,РВ и РС).;

1 – стробируемый ввод-вывод (для передачи информации работают два порта РА и РВ, а порт РС используют для управления передачей информации, то есть для ее квитирования);

2 - двунаправленная магистраль (в этом режиме работает только порт РА, а порт РВ можно использовать в режиме 0).

Тип операций выполняемых ППИ (режим работы) зависит от управляющего слова (УС), записанного в его регистр управляющего слова (РУС).

При программировании используют два формата УС:

1) первый - для задания режима работы и направления включения портов;

2) второй – для установки или сброса произвольного разряда порта С.

Управляющее слово первого формата определяют по таблице 8.

Т а б л и ц а 8

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| х | х | PA | PCh | РВ или РС1 | PB | PCl |

где D7 = 1 – установка формата 1;

D6 = D5 = 0 – режим 0

D6 = D5 = 0 – режим 0

D6 =0, D5 = 1 – режим 1 для портов РА и РСh (старшая тетрада);

D6 = 1, D5 = х – режим 2

D4 = 1 – ввод, D4 = 0 – вывод порта РА;

D3 = 1 – ввод, D3 = 0 – вывод порта РСh;

D2 = 0 – режим 0, D2 = 1 – режим 1 портов РВ и РСl;

D1 = 1 – ввод, D1 = 0 – вывод порта РВ;

D0 = 1 – ввод, D0 = 1 – вывод порта РСl (младшая тетрада).

Разряды УС во втором формате имеют следующие значения:

D7 = 0 – установка формата 2; D6,D5,D4 – не используются;

D3,D2,D1 – определяют двоичный код номера разряда;

D0 = 1 - установка разряда, D0 = 0 – сброс разряда порта С.

При каждом изменении режима работы (новое УС первого формата) все выходные регистры и триггеры состояния сбрасываются.

Как было сказано выше, в режиме 0 базового ввода-вывода могут работать все три порта, причем порт С разделяется на два независимых 4-битных порта (РСh и РCl). Всего, таким образом, получается два 8-битных и два 4-битных порта параллельного ввода или вывода, что обеспечивает 16 возможных конфигураций адаптера в режиме 0. Выводимые данные фиксируются в регистрах-защелках, входящих в состав всех портов, а вводимые данные не запоминаются.

Режим 0 применяется в программно-управляемом вводе-выводе с медленнодействующими периферийными устройствами.

Режим 1 предназначен для однонаправленных передач данных, инициируемых прерываниями. Собственно передача слов данных осуществляется через порты А и В, а шесть линий порта С используются для управления обменом.

Например, если порт РВ установлен на ввод, то параллельно с передачей данных из периферийного устройства (ПУ) в порт РВ подается через разряд 2 порта РС логический 0, сигнализируя о выдаче информации из ПУ, а через разряд 1 порта РС ПУ получает логический 0 подтверждения приема данных. Если порт РВ установлен на вывод информации, то параллельно с выдачей информации в ПУ через разряд 1 порта РС идет сигнал логического 0, а через разряд 2 порта РС осуществляется прием от ПУ логического 0 подтверждения записи данных в ПУ.

Дата добавления: 2015-12-01; просмотров: 2468;