Системы счисления. Коды.

На базе триггеров строят различные пересчетные схемы, состояние которых в определенном коде отображает число импульсов, поступивших на вход. На практике могут использоваться различные коды в зависимости от принятой схемы счисления.

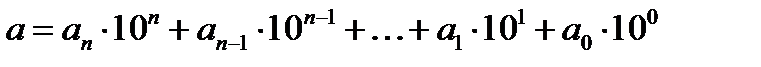

1. Десятичная система. Относится к позиционным системам, в которых значения чисел зависят не только от их цифрового выражения, но и от положения числа в многоразрядном коде. Любое число a в десятичной системе можно представить следующим образом:

Здесь 10 — основание системы счисления, m = n + 1 — число разрядов числа, an = 0,1,2,...,9 — разрядные коэффициенты.

Единица разряда числа в 10 раз больше единицы младшего разряда, стоящего справа.

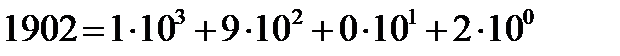

Число 1902 в десятичной системе записывается так:

При этом пишутся только значения разрядных коэффициентов ai опуская показатели основания системы.

Понятно, что для реализации одного разряда десятичный счетчик должен иметь 10 возможных состояний, каждое из которых соответствует одному из значений разряда 0–9.

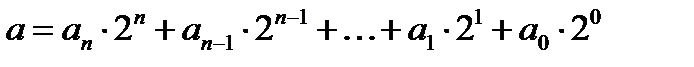

2. Двоичная система. Эго тоже позиционная система счисления с основанием 2, в связи с чем разрядные коэффициенты могут иметь только два возможных значения: 0 или 1. Простая техническая реализация этого условия предопределили широкое использование двоичной системы в электронике и вычислительной технике. В этой системе единица разряда числа в 2 раза больше единицы соседнего младшего разряда.

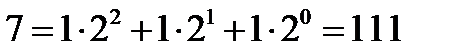

Число 7 в двоичной системе записывается следующим образом:

Каждый разряд двоичного кода технически реализуется при помощи одного триггера. Два возможных состояния триггера соответствуют двум возможным значениям разрядного коэффициента.

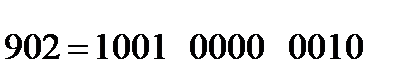

3. Двоично-десятичная система. Является компромиссом между двоичной и десятичной системами. В этой системе расположение десятичных разрядов сохраняется, но каждый десятичный разряд отображается в двоичном коде. Например, десятичное число 902 в двоично-десятичном коде выглядит следующим образом:

Для отображения одного десятичного разряда необходимо 4 двоичных разряда. Используются и непозиционные системы счисления. В этом смысле представляет интерес код Джонсона. В этом коде для отображения одного десятичного разряда надо не 10 (как в десятичной), а 5 триггеров, причем расшифровка состояния разряда производится по состоянию только 2 из 5 триггеров. В этом коде при счете за каждым входным импульсом меняется состояние только одного триггера, что позволяет увеличить скорость счета. Ниже приведено значение кода Джонсона для 10 значащих десятичных цифр:

| Десятичное число | Код Джонсона | ||||

Цифровое выражение числа в какой-либо системе счисления называют кодом числа. Коды, следовательно, могут быть двоичные, двоично-десятичные, десятичные и т.д.

В вычислительной технике и микропроцессорной электронике используют только позиционные коды. Обычно двоичные коды делятся на группы из 8 разрядов, называемых битами. Один двоичный разряд называют битом (binary digit), т.к. он несет в себе единицу информации. Для обозначения знака числа в вычислительной технике слева от двоичного кода добавляют знаковый разряд, значение которого равно 0 для положительных чисел или равно 1 для отрицательных чисел. Поэтому десятичное число +6 в двоичной системе с учетом знака выглядит так: 0.110, а число –6 — 1.110.

Кроме обычных прямых кодов используют инверсные (обратные) и дополнительные коды. Инверсные коды образуются из прямых. Для положительных чисел прямые и обратные коды совпадают. Для отрицательных чисел все разряды модуля (кроме знакового разряда) прямого кода инвертируются.

Дополнительный код — это такой код, сумма которого с прямым кодом равна единице разряда, следующего за старшим разрядом кода. Например, дополнением 8 в десятичной системе является 2. Для отрицательных чисел дополнительный получается прибавлением 1 к обратному коду.

Наличие дополнительных кодов позволяет заменить вычитание кода сложением с дополнительным кодом вычитаемого.

Счетчики импульсов

Счетчиком называют устройство, сигналы на выходах которого в определенном коде отображают число импульсов, поступивших на счетный вход. Используются для подсчета числа импульсов и деления частоты. Счетчики строятся на базе триггеров. Триггер Т-типа может служить примером простейшего счетчика, считающего до двух. Если соединить последовательно m триггеров, можно подсчитать в двоичном коде 2m импульсов. Число m определяет число разрядов, а число 2 — основание системы счисления.

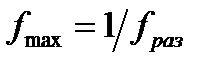

На практике могут использоваться различные системы счисления (коды). Символом счетчика на логических схемах служат буквы СТ (counter) и число, характеризующее систему счисления (2, 10, 2/10). основными эксплуатационными показателями счетчика являются его емкость и быстродействие. Быстродействие счетчика определяется двумя параметрами: разрешающей способностью tраз и временем установки кода счетчика tуст. Под разрешающей способностью понимают минимальное время между входными импульсами, при котором счетчик еще в состоянии их подсчитывать. Обратная величина

называется максимальной частотой счета. Время установки кода tуст равно времени между моментом поступления входного сигнала и моментом установки счетчика в новое устойчивое состояние. Быстродействие зависит от элементной базы счетчика и способов соединения отдельных микросхем между собой.

Классификация счетчиков. Цифровые счетчики классифицируются по следующим параметрам: используемой системе счисления (двоичные, десятичные, двоично-десятичные, в коде Джонсона); направлению счета (суммирующие, вычитающие, реверсивные); способу организации связей между разрядами (с последовательным переносом, с параллельным переносом, кольцевые).

Рассмотрим несколько примеров интегральных счетчиков.

Двоичный четырехразрядный счетчик встречается практически во всех сериях цифровых микросхем. Счетчик содержит 4 Т-триггера, выходы которых Q0 – Q3 образуют параллельный двоичный код состояния счетчика. За исходное состояние счетчика принимается такое, при котором все триггеры находятся в нулевом положении. Принудительная установка счетчика в исходное состояние осуществляется подачей сигнала лог.1 на вход сброса R. Таблица состояний счетчика имеет следующий вид:

| Номер входного импульса | Q3 | Q2 | Q1 | Q0 |

Таким образом, счетчик имеет 16 состояний, т.е. его емкость N = 2m = 16. Здесь m = 4 — число разрядов. На рис. 5.22 показаны условное обозначение такого счетчика, его внутренняя структура и временная диаграмма. Переворот триггера младшего разряда происходит по спаду входного импульса. Триггеры в разрядах соединены между собой последовательно, т.е. представляют собой схему с последовательным переносом. Такая схема логически наиболее проста, но обладает большой задержкой сигнала, особенно в тех случаях, когда последовательно срабатывает большое количество триггеров. Микросхемы позволяют последовательно наращивать емкость двоичных счетчиков кратно 4 разрядам.

В качестве примеров асинхронных двоичных счетчиков на рис.5.23 показаны микросхемы К155ИЕ5 и К555ИЕ19.

Первая в одном корпусе содержит одно и трехразрядные счетчики, а вторая — два четырехразрядных счетчика. Соединяя выход одного счетчика с входом другого (показано штрихами), можно наращивать разрядность. Сброс счетчиков К155ИЕ5 в исходное состояние производится подачей сигнала лог.1 на оба входа 2,3 одновременно.

В делителях частоты, в отличие от счетчиков, выводы могут браться не от всех разрядных триггеров. За счет этого можно повысить коэффициент пересчета (деления) микросхемы при том же количестве выводов корпуса.

Вычитающие двоичные счетчики строятся аналогично и отличаются от суммирующих только связями между разрядами. Последовательность состояний триггеров вычитающего счетчика обратна последовательности суммирующего: после исходного состояния 0000 четырехразрядный двоичный счетчик переходит в состояние 1111 и далее в последовательности от 16 состояния к 14, 13, 12 и т.д. до исходного.

В счетчиках с последовательным переносом задержка распространения сигнала возрастает с увеличением числа разрядов и в многоразрядном счетчике может быть значительной. Это является причиной двух недостатков таких счетчиков: сравнительно низкого быстродействия и возможности появления кратковременных ложных импульсов на выходах дешифраторов состояния счетчиков.

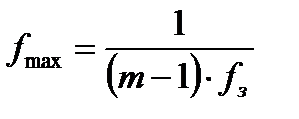

Максимальная частота счета последовательного счетчика

где m — число разрядов; tз - время задержки переключения одного триггера.

Для повышения быстродействия используют счетчики с параллельным переносом.

Счетчики с параллельным переносом состоят из синхронных Т или IK-триггеров. Счетные входные импульсы подаются одновременно на все счетные входы триггеров, но разрешение (синхронизация) срабатывания данного триггера зависит от состояния триггеров предыдущих разрядов. Задержка переключения всего счетчика равна задержке для одного триггера. В таких счетчиках кроме разрядных триггеров содержатся дополнительные логические элементы. При повышении числа разрядов растет сложность внутренних логических связей. На рис. 5.24 показана внутренняя структура 4-разрялиого счетчика с параллельным переносом. Триггер первого разряда счетчика переключается за каждым входным сигналом, но триггеры последующих разрядов переключаются лишь в том случае, если все предыдущие триггеры находятся в единичном состоянии.

Счетчики с параллельным переносом широко применяются в быстродействующих устройствах. Они обладают более высокой помехоустойчивостью, т.к. в паузах между входными импульсами триггеры счетчика, блокированы. Недостатками таких счетчиков является меньшая нагрузочная способность из-за наличия дополнительной внутренней нагрузки и трудность организации параллельного переноса при большом числе разрядов. Поэтому параллельный перенос обычно организуется только для ограниченного числа разрядов, обычно в пределах объема одной микросхемы, а наращивание дальнейшей разрядности происходит путем последовательного переноса между микросхемами. Примером синхронного двоичного счетчика может служить микросхема К561ИЕ10 — рис. 5.25. В корпусе этой микросхемы содержится два четырехразрядных двоичных счетчика с параллельным переносом. Счетчик может запускаться положительным перепадом по входу V при наличии лог.1 на входе С или отрицательным перепадом по входу С при наличии лог.1 на входе V. Штриховой линией показана организация 8-разрядного счетчика на базе микросхемы К561ИЕ10.

Реверсивный двоичный счетчик с предварительной установкой. Реверсивные счетчики позволяют осуществить подсчет входных импульсов как в режиме суммирования, так и в режиме вычитания в зависимости от состояния входа управления реверсом. Сигнал реверса переключает связи между триггерами разрядов счетчика. Предварительная установка позволяет устанавливать триггеры разрядов счетчика в желаемое состояние по установочным уходам. Примером такого счетчика является микросхема К561ИЕ11 — рис. 5.26. Микросхема имеет 4 установочных входа D1 – D4 и вход разрешения установки V. При подаче лог.1 на вход V происходит запись установочного кода со входов D1 – D4 в триггеры счетчика. Вход ± 1 служит для управления реверсом счетчика: при наличии лог.1 на этом входе счетчик работает в режиме сложения, а при лог.1 — в режиме вычитания. Вход С является счетным входом счетчика, а вход Р0 — входом сигнала переноса с микросхемы соседнего младшего разряда. Микросхема имеет 4 двоичных выхода и один выход сигнала переноса в микросхему старших разрядов. Асинхронное каскадирование счетчиков ИЕ11 получится, если сигнал переноса Р подать на вход С последующей микросхемы. Синхронное каскадирование получается, если соединить параллельно тактовые входы С всех микросхем и подать сигнал от выхода переноса Р первой микросхемы на вход переноса Р0 последующей (старшей разрядности) микросхемы.

Реверсивный двоично-десятичный счетчик. Для того чтобы образовать из двоичного счетчика двоично-десятичный, необходимо внутри микросхемы создать логическую цепь, которая бы зафиксировала переход счетчика в 11-е (по счету) состояние 1011 и сразу же сбросила триггеры микросхемы в исходное состояние 0000. Тем самым, число состояний двоичного счетчика ограничивается 10. Сигналы на выходе двоично-десятичного счетчика чередуются в порядке двоичной последовательности 8421 от первой комбинации 0000 до десятой 1010. На рис.5.27 показан реверсивный двоично-десятичный счетчик с предварительной установкой К561ИЕ14. Сброс в нулевое состояние такого счетчика происходит путем предварительной установки кода 0000 по входам D1 – D4. По сигналу высокого уровня на входе 2/10 счетчик работает как двоичный, а при низком уровне — как двоично-десятичный. Режимы работы микросхемы в зависимости от состояния управляющих сигналов представлены в следующей таблице:

| Входы | Режим работы | |||

| V | ±1 | C | 2/10 | |

| X | X | Хранение | ||

| Суммирование в двоичном коде | ||||

| Суммирование в двоично-десятичном коде | ||||

| Вычитание в двоичном коде | ||||

| Вычитание в двоично-десятичном коде | ||||

| X | X | X | Параллельная установка |

Знаком X в таблице обозначено произвольное состояние входа.

Счетчик-делитель на 8 состояния с дешифратором показан на рис. 5.28. Этот счетчик содержит в своем составе 4 триггера, меняющих состояние в соответствии с кодом Джонсона. 8 состояний счетчика расшифрованы при помощи встроенного дешифратора, так что микросхема имеет 8 информационных выходов 0 ¸ 7 и выход переноса Р. Сигнал на каждом информационном выходе возникает тогда, когда счетчик устанавливается в соответствующее состояние. В зависимости от соотношения сигналов V и С на входах можно выбрать фронт счетного импульса, по которому происходит счет. Вход сброса R всегда имеет приоритет по отношению к другим входам. В связи с тем, что в счетчике использован код Джонсона, сигнал переноса Р имеет скважность, равную 2. Если требуется уменьшить коэффициент пересчета в пределах одной микросхемы, достаточно соединить вход сброса R с надлежащим информационным выходом. При наращивании микросхем, с целью получения больших коэффициентов деления, кратных 8, выход Р микросхемы младшего разряда соединяют со входом С соседнего старшего разряда.

Десятичный счетчик с дешифратором, например, К561ИЕ8 отличается от счетчика-делителя на 8 лишь наличием 5 триггеров и соответственно 10 выходов — рис. 5.29.

Делители могут работать только, в режиме деления частоты, поэтому имеют один выход. Иногда делители имеют несколько выходов, но все равно не от всех разрядов счетчика. Микросхема может иметь жесткий коэффициент деления или перестраиваемый коэффициент. В последнем случае он устанавливается предварительной установкой состояния разрядных триггеров делителя. Например, коэффициент деления делителя 564ИЕ15 может быть установлен от 3 до 21327 с шагом единица. Этот делитель может работать в двух режимах: непрерывного счета (деления), когда на выходе образуются импульсы с частотой fвх/Kдел и длительностью, равной периоду входных импульсов, или однократного счета, когда после поступления на вход определенного числа импульсов выходной сигнал из состояния 0 переходит в состояние 1 и остается в этом состоянии.

Регистры

Регистры — это устройства, предназначенные для приема, хранения и передачи дискретных кодов (слов). В основе регистра используются триггеры. Число триггеров определяет разрядность слова.

Занесение информации в регистры называется операцией ввода или записи. Выдачу информации внешним устройством называют операцией вывода или считывания.

В зависимости от функционального назначения все регистры подразделяются па две категории: регистры памяти (хранения) и регистры сдвига. В свою очередь, сдвигающие регистры в зависимости от способа ввода и вывода информации делятся на параллельные, последовательные и комбинированные (последовательно-параллельные), а по направлению передачи информации (сдвига) — на однонаправленные и реверсивные.

Запоминающие регистры — простейший вид регистров. Их назначение — хранить кодовую информацию небольшого объема в течение относительно непродолжительного времени. Эти регистры представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа — бит информации. Запись и считывание информации производится одновременно во всех разрядах параллельным кодом. Структура запоминающего регистра иллюстрируется рис.5.30.

Наращивание разрядности регистров памяти достигается добавлением нужного числа триггеров.

В качестве примера рассмотрим запоминающий регистр К155ИР15 — рис.5.31. Это четырехразрядный регистр, выходы которого могут иметь третье, высокоимпендансное состояние Z. Входы E1, E2 определяют режим ввода, а входы Z1, Z2 — режим вывода информации. Вход R — сбросовый. Параллельный ввод информации в триггеры регистра со входов D1 – D4 происходит по переднему фронту тактового сигнала С при наличии лог.0 на обоих входах E1, E2. При наличии лог.1 хотя бы на одном из входов E1, E2 регистр переходит в режим хранения. Подача сигнала лог.1 на сбросовый вход R обнуляет регистр независимо от состояния других входов. Зависимость режимов работы регистра от комбинации входных сигналов показана в следующей таблице:

| Входы | Режимы работы | ||||

| R | C | E1 | E2 | Di | |

| X | X | X | X | Обнуление | |

| Запись | |||||

| Запись | |||||

| X | X | X | Хранение | ||

| X | X | X | Хранение |

Отличительная особенность этой микросхемы — наличие буферных выходных каскадов, управление которыми осуществляется по двум входам Z1, Z2. Если хотя бы на одном из этих входов существует сигнал высокого уровня, то буферные каскады закрыты и выходы микросхемы находятся в высокоимпендансном состоянии, т.е. практически отключены от триггеров. И только при Z1 = 0 и Z1 = 0 состояние триггеров передается на выходы регистра. Состояние буферных выходных каскадов не сказывается на режимах работы микросхемы.

Регистр К155ИР15 имеет тактовую частоту, равную 25 мГц и потребляет ток 72 мА.

Регистры сдвига представляют собой основную массу регистров, используемых на практике. Этот вид регистров отличается большим разнообразием, как в функциональном отношении, так и в отношении схемных решений и параметров. Регистры сдвига кроме операции хранения осуществляют преобразование последовательного кода в параллельный и наоборот, служат в качестве цифровых элементов задержки, выполняют арифметические и логические операции. Регистр состоит из последовательно соединенных триггеров. Передача информации с триггера на триггер происходит под воздействием тактовых импульсов.

Блок-схема сдвигаемого нереверсивного регистра показана на рис.5.32, а пример реализации на D-триггерах — на рис.5.33. Значение входного сигнала появится на выходе последнего разряда через m тактов, где m — число разрядов регистра. Поэтому для ввода в регистр m-разрядного слова потребуется m тактов. Показанный на рисунке регистр преобразует входной последовательный код в выходной параллельный. Следует иметь в виду, что информационный сигнал, бывший на выходе старшего разряда регистра, с приходом очередного тактового импульса выводится из регистра и исчезает.

В реверсивных сдвиговых регистрах может происходить передача информации как в направлении от младшего разряда к старшему, так и в обратном направлении. Регистр кроме последовательного входа может иметь параллельный установочный вход. В качестве примеров рассмотрим несколько серийно выпускаемых микросхем сдвиговых регистров.

На рис.5.34,а показана микросхема К561ИР2. В состав микросхемы входит два четырехразрядных однонаправленных регистра сдвига с последовательным вводом и параллельным выводом информации. Вход D — информационный. Сдвиг информации происходит по положительному фронту тактовых импульсов на входе С. Обнуление регистра производится сигналом лог.1, подаваемым на вход R. Способ наращивания разрядности регистра показан на рис. 5.34,б.

Микросхема К155ИР1 — рис.5.35 — представляет собой четырехразрядный реверсивный регистр сдвига с последовательным и параллельным вводом информации и параллельным выводом. Микросхема используется в качестве буферной памяти, прямого кольцевого распределителя импульсов, элемента задержки на несколько тактов и др. D0 — вход регистра для последовательного кода, a D1 – D4 — входы для параллельного кода. Вход V служит для выбора режима работы регистра. При V = 0 происходит сдвиг вправо при каждом отрицательном перепаде потенциала па входе C1, параллельные входы D1 – D4 отключаются. При V = 1 разрешается параллельные установка по входам D1 – D4 сдвиг влево при отрицательном перепаде потенциала на входе С. Для сдвига влево необходимо произвести внешние соединения выходов , Q4, Q3, Q2 со входами D3, D2, D1 соответственно. Информация в последовательном коде в этом случае вводится через вход D4.

Дешифраторы

Дешифраторы представляют собой комбинационные схемы, не имеющие элементов памяти и предназначенные для распознавания кодовых комбинаций (слов). Другими словами, дешифраторы преобразуют слово, заданное в одной системе счисления, в слово, представленное в системе с основанием бесконечность, когда сигнал присутствует на одном из всех выходов дешифратора. В качестве примера приведем таблицу состояний одноразрядного дешифратора двоично-десятичною кода в десятичный.

| Номер комбинации | Двоично-десятичный код | Десятичный код | ||||||||||||

| x3 | x2 | x1 | x0 | y0 | y1 | y2 | y3 | y4 | y5 | y6 | y7 | y8 | y9 | |

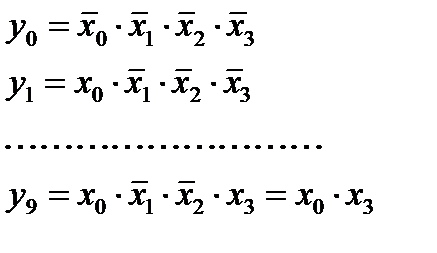

Каждая строка этой таблицы может быть описана логической функцией, связывающей выходной сигнал с комбинацией входных сигналов:

Уменьшение количества входных переменных для некоторых из этих функций (например, только две переменные из четырех для функции у9) возможно благодаря тому, что используется только 10 из 16 возможных комбинаций входных переменных.

На рис.5.36,а показана функциональная схема дешифровки двоично-десятичного кода, записанного в триггеры входного регистра, а на рис.5.36.б — условное обозначение дешифратора. Практически, дешифратор можно реализовать на диодной матрице по рис.5.37, каждая строчка которой представляет собой схему совпадения И.

В интегральном исполнении дешифраторы формируются при помощи активных логических элементов. Описанный дешифратор двоично-десятичного кода в десятичный присутствует практически во всех сериях цифровых интегральных микросхем, например, К561ИД1. Иногда такой дешифратор объединяют в одном корпусе с двоично-десятичным счетчиком, например, микросхема К561ИЕ8.

Часто используется полный двоичный дешифратор двоичного кода. В этом случае при четырех входных переменных дешифратор имеет 16 выходов. К таким дешифраторам относится микросхема К155ИДЗ (рис.5.38). Этот дешифратор имеет инверсные выходы, поэтому в исходном состоянии сигнал лог.1 присутствует на всех выходах, кроме выхода у0. Микросхема имеет два управляющих входа V1, V2. При дешифровке на обоих управляющих входах должен быть разрешающий сигнал лог.0.

Дешифратор К155ИД3 может работать как демультиплексор с одного входа (V1) на один из 16 выходов в зависимости от состояния входного кода x0 – x3. Вход V2, при этом используется как стробируюший.

Широко используются дешифраторы сигналов двоично-десятичного кода в сигналы управления семисегментными цифровыми индикаторами. Такие дешифраторы можно считать преобразователями кода. На рис.5.39 показан дешифратор такого типа K176ИД2. Дешифратор содержит в своем составе 4 триггера для запоминания входного кода. Вход S определяет полярность входных сигналов: при уровне лог.1 на входе S для зажигания сегментов индикатора используется уровень 0 на информационных входах, а при уровне лог.0 на входе S — уровень 1.

Вход С управляет работой входных триггеров: при уровне лог.1 на входе С триггеры превращаются в повторители, а при уровне лог.0 переходят в режим хранения входной информации.

Уровень, лог.1 на входе R гасит индицируемый знак, а уровень лог.0 разрешает индикацию.

Шифраторы

Шифраторы производят обратную дешифраторам операцию. У них входной сигнал присутствует только на одном из входов, а на выходе формируется комбинация сигналов в заданном коде.

На рис. 5.40 показан двоичный шифратор К555ИВ1. Этот шифратор принимает входной сигнал низкого уровня на один из 8 входов, а на выходе формируется 3-разрядный двоичный инверсный код, соответствующий номеру использованного входа. При наличии лог. 1 на управляющем входе Е все выходы 1–8 отключаются. Для работы шифратора необходимо E = 0. Шифратор К555ИВ1 приоритетный: в том случае, если входной сигнал подан на несколько входов, то дешифратор будет кодировать сигнал со входа с максимальным номером.

Существуют шифраторы без управляющих сигналов, у них шифрация происходит автоматически, если хотя бы на одном входе присутствует уровень лог.1.

Шифраторы используются достаточно редко и поэтому выпускаются ограниченной номенклатурой.

Дата добавления: 2016-02-09; просмотров: 2271;