Метод эталонных контрольных точек.

В основе данного метода лежит проверка сигналов в контрольных точках при работе схемы с их эталонными контрольными точками.

«+» Метод позволяет проверить работу элементов, узлов, всего устройства в целом.

«-» Имеет высокую трудоёмкость.

Этапы разработки схемы:

1. Производится анализ работы схемы, выбирается элемент для проверки.

2. Выбираются контрольные точки.

3. Составляется эталонная таблица истинности состояния выбранных контрольных точек.

4. Реализуется схема анализа работоспособности схемы или элементы.

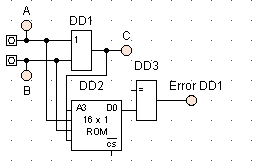

Схема анализа работоспособности:

| A | B | C | |

Элемент памяти DD2 используется для хранения таблицы истинности проверяемого элемента. При этом адресные входы памяти подключаются к входным контрольным точкам. Желательно подключение производить с младших адресов.

С помощью таблицы истинности формируем сигнал проверки работы схемы:

| Адрес | Y Error DD1 | |||

| A | B | C | ||

Здесь память элемента DD2 используется в качестве элемента анализа работоспособности схемы, и в неё уже прошивается таблица анализа ошибочного или неошибочного состояния.

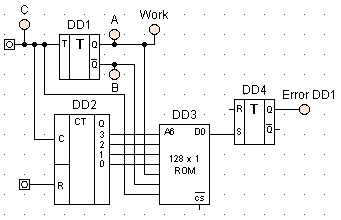

C помощью счётчика в таблицу вносятся такты работы схемы.

| Выходы счётчика | «Ноги» Т триггера | ||

| 0 такт | |||

| 1 такт | |||

Для динамических элементов разбиваем процесс работы на временные характеристики (такты), при этом внутри такта у нас получается статическое состояние сигналов в контрольных точках. Для элемента проверки работоспособности на счётчике реализуется динамическая часть (перебор тактов), на памяти записывается статическое состояние внутри заданных тактов. При этом желательно счётчик подключать к старшим адресам памяти, реализуя страничную организацию памяти. Контрольные точки подключаются к младшим адресам памяти, тем самым получая внутри такта нужную статическую комбинацию.

Дата добавления: 2016-01-20; просмотров: 843;