Конвейерные (Subranging, Pipelined) АЦП

Хотя целесообразность построения параллельных АЦП с высоким разрешением (большим, чем 10-разрядов) вызывает сомнения, такие АЦП часто используются в качестве подсистем конвейерных (subranging) АЦП (иногда называемых полупараллельными (half-flash)АЦП), которые обладают значительно более высокой разрешающей способностью (до 16-разрядов).

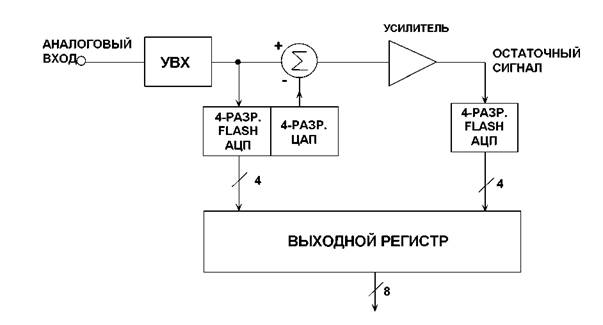

Блок-схема 8-разрядного конвейерного АЦП на основе двух параллельных 4-разрядных АЦП показана на рис.3.24. Учитывая широкую распространенность 8-разрядных параллельных преобразователей с высокими частотами дискретизации, пример такого преобразователя мы используем для иллюстрации концепции. Процесс преобразования осуществляется в два этапа. Первые четыре старших разряда (MSB) оцифровываются первым параллельным АЦП (обладающим точностью выше 8 разрядов), и двоичный выходной 4-разрядный код подается на 4-разрядный ЦАП (также обладающий точностью выше 8 разрядов). Выходной сигнал с ЦАП вычитается из сохраненного аналогового входного сигнала, и результат вычитания (остаток) усиливается и подается на второй параллельный АЦП. Затем выходные сигналы двух 4-разрядных параллельных преобразователей объединяются в один 8-разрядный выходной код. Если динамический диапазон остаточного сигнала не точно заполняет динамический диапазон второго параллельного преобразователя, возникает нелинейность и, возможно, потеря кода.

| 8-РАЗРЯДНЫЙ КОНВЕЙЕРНЫЙ АЦП |

Рис. 3.24

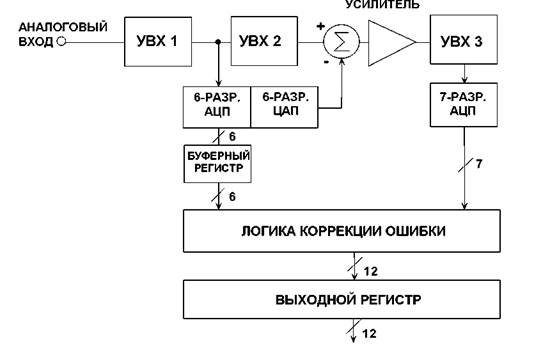

Современные конвейерные АЦП используют методы, называемые цифровой коррекцией, для устранения проблем, связанных с архитектурой, представленной на рис.3.24. Упрощенная блок-схема 12-разрядного конвейерного АЦП с цифровой коррекцией (DCS) представлена на рис.3.25. Представленная архитектура подобна той, что используется в 12-разрядном АЦП AD6640 с быстродействием 65MSPS. Обратите внимание, что 6-разрядный и 7-разрядный АЦП используются для получения выходного кода в 12 разрядов. Данные АЦП не являются параллельными АЦП, но используют архитектуру усилителей модуля (magnitude-amplifier, MagAmp™), которая вскоре будет описана.

Если в преобразовании первой ступени нет ошибок, 6-разрядный остаточный сигнал, поданный на 7-разрядный АЦП с суммирующего усилителя, никогда не превысит половину диапазона 7-разрядного АЦП. Избыточный динамический диапазона второго АЦП, совместно с логикой исправления ошибки (обычно это просто полный сумматор), используются для исправления в выходных данных большинства ошибок, свойственных традиционным преобразователям с конвейерной архитектурой без коррекции. Важно обратить внимание, что 6-разрядный ЦАП должен иметь точность, соответствующую не менее чем 12-разрядам, потому что при цифровой коррекции не исправляются ошибки ЦАП. На практике вместо "двоичного" ЦАП часто используются ЦАП типа "термометр" или полностью декодирующие ЦАП, имеющие на каждый уровень один коммутатор тока (63 коммутатора в случае 6-разрядного ЦАП). Этим гарантируется высокая дифференциальная и интегральная линейность и минимизируются переходные процессы, вызванные коммутацией.

| 12-РАЗРЯДНЫЙ 65MSPS КОНВЕЙЕРНЫЙ АЦП С ЦИФРОВОЙ КОРРЕКЦИЕЙ ОШИБОК AD6640 |

Рис. 3.25

УВХ-2 хранит сигнал с выхода УВХ-1 до тех пор, пока выполняется преобразование первой ступени, максимизируя, таким образом, производительность. УВХ-3 ограничивает значение ложного сигнала (glitch) по остаточному сигналу, таким образом, давая возможность осуществить полный цикл преобразования сигнала 7-разрядным АЦП (6- и 7-разрядные АЦП в AD6640 являются поразрядными АЦП, построенные по архитектуре MagAmp, которые требуют большего времени установки, чем параллельные АЦП).

Такой метод многоступенчатого преобразования иногда упоминается как конвейерная обработка. Дополнительные регистры сдвига, подключенные последовательно с цифровыми выходами АЦП первой ступени, гарантируют, что, когда их выводы объединяются в логике коррекции ошибки, они оказываются синхронизированными по времени с последними 7 разрядами второго АЦП. Поэтому конвейерный АЦП имеет специфическое число тактовых циклов ожидания результата, или конвейерную задержку, связанную с выходными данными. Передний фронт тактового импульса дискретизации (отсчета N) используется для синхронизации выходного регистра, но данные, которые появляется по фронту этого тактового импульса, соответствует отсчету N - L, где L — число тактовых циклов конвейерной задержки. В AD6640 конвейерная задержка выполняется в два тактовых цикла.

Схема коррекции ошибки, описанная выше, рассчитана на исправление ошибок, допущенных при первом преобразовании. Ошибки внутреннего усиления АЦП, смещения и линейности корректируются, пока остаточный сигнал находиться в пределах динамического диапазона АЦП второй ступени. Эти ошибки не будут затрагивать линейности передаточной характеристики всего АЦП. Но ошибки конечного преобразования становятся ошибками общей функции передачи всего АЦП. Ошибки линейности или усиления ЦАП и усилителя остаточного сигнала не корректируются и проявятся как нелинейность или немонотонность в общей функции передачи всего АЦП.

Мы рассмотрели пока только двухступенчатые конвейерные АЦП, поскольку они являются самыми простыми для анализа. Но нет причины останавливаться на двух ступенях. Трех- и четырехступенчатые конвейерные АЦП являются весьма обычной продукцией и могут быть реализованы самыми разными способами, как правило — с цифровой коррекцией ошибок.

Упрощенная блок-схема 12-разрядного CMOS АЦП AD9220 с быстродействием 10MSPS, однополярным питанием и потребляемой мощностью 250 мВт представлена на рис.3.26. АЦП AD9221 (1,25 MSPS, 60 мВт) и AD9223 (3MSPS, 100 мВт) имеют идентичную архитектуру, но работают с более низким энергопотреблением и на более низких частотах дискретизации. Это четырехступенчатая конвейерная архитектура с дополнительным разрядом, использующимся для коррекции ошибки на второй, третьей и четвертой ступенях. Благодаря конвейерной архитектуре, эти АЦП имеют три тактовых цикла конвейерной задержки (см. рис.3.27).

|

| Рис. 3.26 |

12-РАЗРЯДНЫЕ КОНВЕЙЕРНЫЕ CMOS АЦП AD9220/9221/9223

КОНВЕЙЕРНАЯ ЗАДЕРЖКА АЦП AD9220/9221/9223

Рис. 3.27 Каскадные АЦП (BIT-PER-STAGE, последовательные)

Для выполнения аналого-цифрового преобразования существуют различные архитектуры, использующие принципы последовательного преобразования. В действительности, конвейерный АЦП с одним разрядом на ступень и без коррекции ошибок может рассматриваться как АЦП последовательного счета. На рис.3.28 представлена общая концепция. УВХ хранит значение входного сигнала в течение цикла преобразования. Существует N ступеней, каждая из которых имеет одноразрядный цифровой выход и выход остаточного сигнала. Остаточный сигнал каждой ступени является входным сигналом для следующей ступени. Как показано на рисунке, последний разряд является просто выходным сигналом компаратора.

Дата добавления: 2016-01-07; просмотров: 2456;