Логические элементы на полевых транзисторах

Особенности ЛЭ на полевых транзисторах:

1. высокая технологичность;

2. малая потребляемая мощность в статическом состоянии;

3. высокое входное сопротивление;

4. сравнительно невысокое выходное сопротивление, позволяющее работать ЛЭ на емкостную нагрузку (до 500 пФ);

5. сравнительно невысокое быстродействие, обусловленное наличием большой входной емкости;

6. среднее время задержки до 20 нс.

Обычно логические элементы строят на комплиментарных транзисторах (серия КМОП: К176, К561, К564, К765).

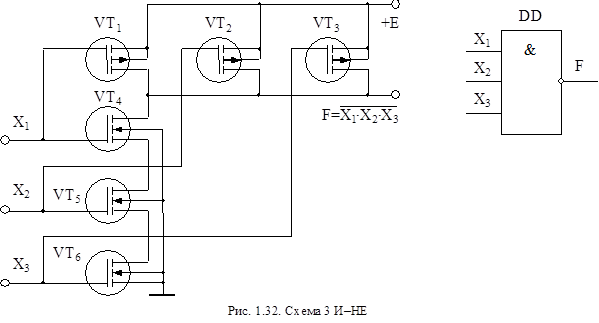

Транзисторы VT1, VT2, VT3 соединены в схеме параллельно, а транзисторы VT4, VT5, VT6 — последовательно (ярусно).

1) Если на всех входах X1=X2=X3=0, то транзисторы VT4, VT5, VT6 закрыты, а транзисторы VT1, VT2, VT3 — открыты. Тогда F=1, и на выходе — напряжение, примерно равное E.

2) Если X1=X2=0, а X3=1, то транзисторы VT1, VT2, VT6 открыт, а VT3, VT4, VT5 — закрыты, и F=1.

3) Если X1=X2=X3=1, то есть uВХ>EЗ0 для транзисторов VT4, VT5, VT6, то F=0.

Мощность, потребляемая схемой в статическом состоянии PСТ=0,1 мВт.

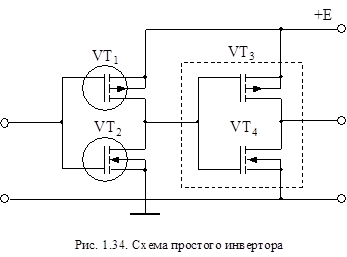

Транзисторы VT1, VT2, VT3 с p-каналом соединены в схеме последовательно, а транзисторы VT4, VT5, VT6 — параллельно.

1) Если на всех входах X1=X2=X3=0, то транзисторы VT4, VT5, VT6 закрыты, а транзисторы VT1, VT2, VT3 — открыты. Тогда F=1.

2) Если X1=X2=0, а X3=1, то транзистор VT6 открывается, а VT3 — закрывается, и F=0.

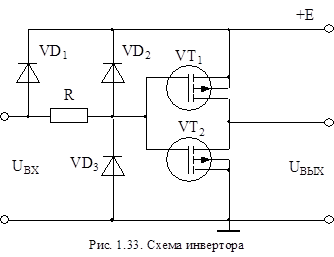

Для повышения помехоустойчивости рассматриваемых ЛЭ на входе ставят инвертор.

Диод VD1 защищает входную цепь от слишком больших входных сигналов. При uВХ>E диод VD1 открывается. Диоды VD2 и VD3 и резистор R защищают входные цепи транзисторов VT1 и VT2 от статического напряжения. Если входное статическое напряжение UСТ<0, срабатывает диод VD3.

Постоянная времени

t=R1×C = 10 нс, (1.21)

где С — барьерная емкость диода, то есть она мало сказывается на быстродействии логического элемента.

|

Сопротивление R1 и барьерная емкость C диода образуют интегрирующую цепь. Используя ее, можно уменьшить сопротивление на затворе транзистора. В большинстве логических элементов такая цепь ставится на входе. Ее включение позволяет увеличить напряжение помех на входе до значения UПОМ = 0,3×E.

Для повышения нагрузочной способности ЛЭ на выходе включают простой или сложный инверторы.

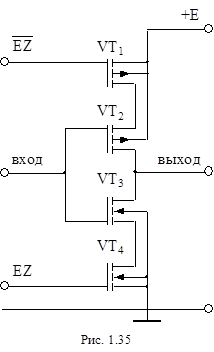

На полевых транзисторах легко реализуется схема ЛЭ с тремя устойчивыми состояниями.

|

Если транзисторы VT1 и VT4 закрыты, то выходное сопротивление такой схемы велико (высокоимпедансное состояние). На входы вспомогательных транзисторов VT1 и VT2 подается сигнал EZ, дающий разрешение для работы транзистора.

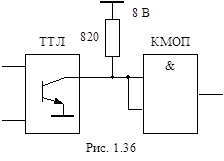

Часто требуется согласовать элементы ТТЛ и элементы КМОП. Для ТТЛ UВЫХ1=2,4 B, UВЫХ0=0,4 B, для КМОП — UВЫХ1=8 B. Для согласования по уровню входного и выходного сигналов существуют 3 способа:

1. Записать КМОП пониженным напряжением так, чтобы входной и выходной сигналы были близки к ТТЛ.

2. Использовать элементы ТТЛ с открытым коллектором.

3. Использовать преобразователи уровня.

КМОП в ТТЛ à 564 ПУ4

ТТЛ в КМОП à 564 ПУ7, ПУ8.

Незадействованные входы логических элементов либо соединяются параллельно с исследуемым входом, либо подключаются к источнику питания. ЛЭ на полевых транзисторах используются в высокоэкономичных цифровых устройствах с относительно невысоким быстродействием.

Дата добавления: 2015-12-16; просмотров: 1548;