Логические элементы со связанными эмиттерами

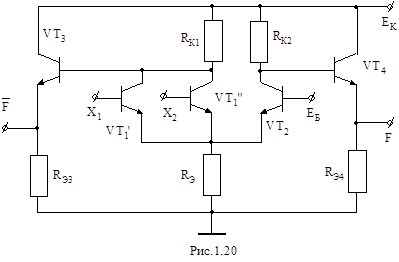

Схема логического элемента со связанными эмиттерами представлена на рис.1.20.

Входные сигналы Х1, Х2 подаются на транзисторы VT1' и VT1". Транзистор VT2 ¾ вспомогательный транзистор, на базу которого подается постоянное напряжение +ЕБ. Эмиттеры транзисторов VT1 и VT2 связаны ¾ у них общее сопротивление RЭ, через которое течет постоянный ток IЭ = сonst.

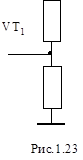

Если входные сигналы Х1 = Х2 = 0, то транзисторы VT1' и VT1" закрыты, а через транзистор VT2 протекает ток, и в этом случае

. (1.17)

. (1.17)

Если Х1 = 1, т.е. UBX1 > 0, то транзистор VT1' откроется, потенциал эмиттеров всех транзисторов возрастет, а т.к. потенциал базы фиксирован, то VT2 закроется и весь ток потечет через VT1, на выходе F появится сигнал F = 1, а на выходе  ¾ сигнал

¾ сигнал  = 0.

= 0.

Таким образом, данный логический элемент реализует функцию логического "ИЛИ", т.е.  ,

,  .

.

Рассмотрим схему соединения в данном ЛЭ транзисторов VT1 и VT2 (рис.1.21). Допустим, что входной сигнал изменяется медленно. Если входное напряжение UВХ = 0, то транзистор VT1 закрыт, а VT2 открыт, и его напряжение соответствует логическому нулю. Если UВХ = ЕБ, то оба транзистора открыты, и это состояние соответствует точке А на рис.1.22.

Если UВХ медленно увеличивается от значения ЕБ, то транзистор VT1 будет продолжать открываться. Т.к. потенциал базы VT2 фиксирован, а ЕЭ увеличивается, то транзистор VT2 будет закрываться. В точке В транзистор VT2 закрыт, и этому соответствует пороговое напряжение логического элемента UП2. Когда VT2 закрылся, его входное сопротивление RВХ резко возросло. Это означает, что эквивалентное сопротивление в цепи эмиттеров тоже возросло:

RЭКВ(Э) = RЭ || RВХ2, (1.18)

и поэтому наклон участка DE изменился. В точке Е транзистор VT1 входит в насыщение, т.е. он может быть представлен в виде эквипотенциальной точки (рис.1.23). На участке EF транзистор VT1 насыщен и напряжение UК1 повторяет входное напряжение.

Характеристика схемы с точки зрения параметров.

1. Быстродействие определяется tЗ.СР., которое в этой схеме достаточно мало и составляет величину меньше 10 нс. Таким образом, данный ЛЭ относится к классу сверхбыстродействующих. Этому способствуют:

1) Транзисторы работают в активном режиме без захода в область насыщения.

2) Транзистор VT2 включен по схеме ОБ, поэтому его быстродействие оценивается постоянной времени ta.

3) Сопротивления RK1 и RK2 невелики.

2. Коэффициент объединения по входу n £ 5, а коэффициент разветвления по выходу m £ 15.

3. Схема обладает плохой помехоустойчивостью, т.к. ширина активной зоны (UП1 – UП2) составляет десятые доли вольта. Допустимое напряжение помех примерно 0.15В.

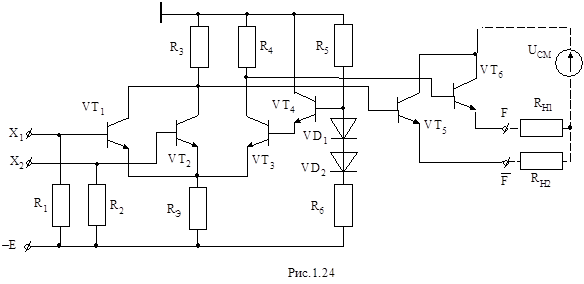

Рассмотрим реальную схему ЛЭ со связанными эмиттерами (рис.1.24). Схемы такого типа - это схемы 500 и 1500 серий.

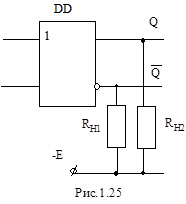

Такая схема включения позволяет увеличить помехоустойчивость ЛЭ. Сопротивление нагрузки выбирается в пределах RН = 50…240Ом. Напряжение питания Е = –5.2В. роль источника напряжения для питания опорного транзистора играет делитель R5 – R6. Такой ЛЭ на схеме обозначается как на рис.1.25. У ЛЭ 500 серии среднее время задержки tЗ,СР @ 3нс, а у 1500 серии tЗ,СР < 1нс.

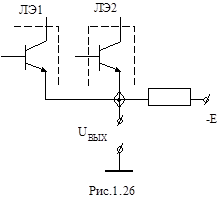

Чтобы расширить возможности ЛЭ, можно реализовать дополнительное соединение выходов ¾ "монтажное ИЛИ" (рис.1.26).

Часто возникает проблема согласования ТТЛ и ЭСЛ (эмиттерно-связанной логики). Для этого используют специальные схемы согласования, которые называются преобразователями уровня. Например, схема К500ПУ124 используется для согласования ТТЛ с ЭСЛ, а схема К500ПУ125 ¾ для согласования ЭСЛ с ТТЛ.

Дата добавления: 2015-12-16; просмотров: 820;